## THE PARALLEL UNIVERSE

# Vectorization in LLVM and GCC for Intel CPUs and GPUs

Efficient Heterogeneous Parallel Programming Using OpenMP

ArrayFire Interoperability with oneAPI, Libraries, and OpenCL

## Contents

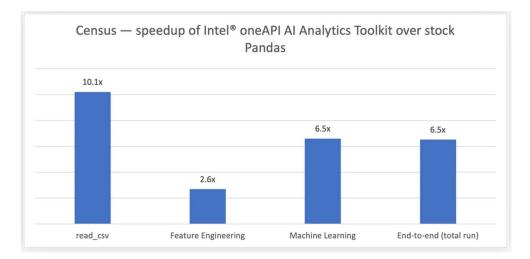

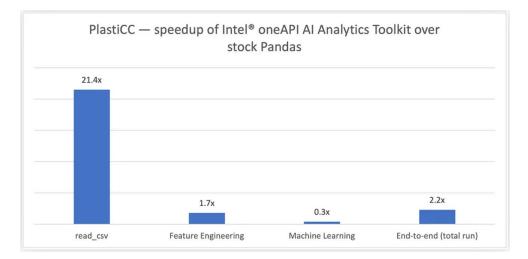

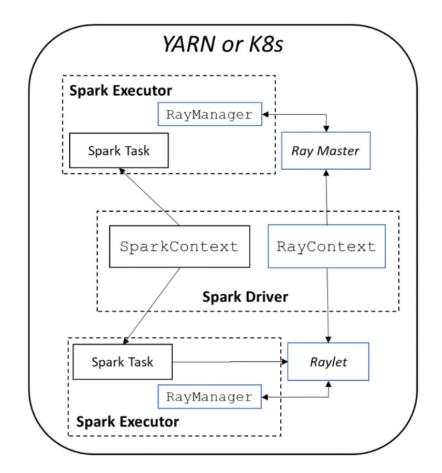

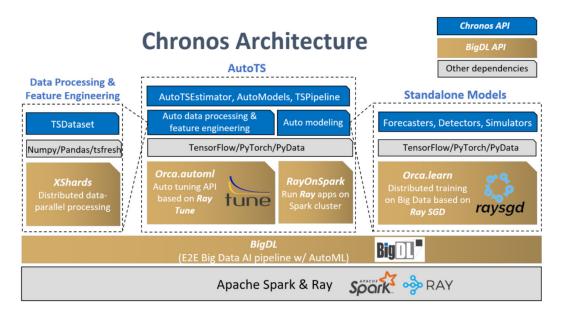

FEATURE

#### Letter from the Editor 3 Vectorization in LLVM and GCC for Intel CPUs and GPUs 5 SIMD Support Is Evolving Rapidly in Modern Compilers Efficient Heterogeneous Parallel Programming Using OpenMP 17 Best Practices to Keep the CPU and GPU Working at the Same Time ArrayFire Interoperability with oneAPI, Libraries, and OpenCL 22 Taking Advantage of oneAPI to Avoid Code Rewrites Using the oneAPI Level Zero Interface 29 A Brief Introduction to the Level Zero API Hyperparameter Optimization with SigOpt for MLPerf Training on 38 Habana Gaudi Achieve Faster Convergence with Higher Accuracy in AI Training Scale Your Pandas Workflow with Modin 50 Scalable Data Analytics with No Rewrite Required **From Ray to Chronos** 55 Build End-to-End AI Use-Cases with BigDL on Top of Ray

## Letter from the Editor

Henry A. Gabb, Senior Principal Engineer at Intel Corporation, is a longtime high-performance and parallel computing practitioner who has published numerous articles on parallel programming. He was editor/coauthor of "Developing Multithreaded Applications: A Platform Consistent Approach" and program manager of the Intel/Microsoft Universal Parallel Computing Research Centers.

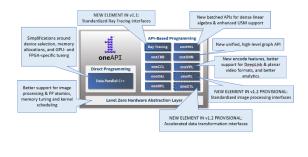

## oneAPI Continues Gaining Momentum

When I became editor of *The Parallel Universe*, I noted in my first letter to readers that I dreaded the heterogeneous parallel computing future. Five years later, I'm downright optimistic about it, mainly because of <u>oneAPI™</u>. Sanjiv Shah (Intel Vice President and General Manager of Developer Software) is similarly optimistic in his recent "<u>Giving thanks for oneAPI</u> <u>progress</u>" blog. The new oneAPI v1.1 specification is now live, and the provisional v1.2 specification adds a lot of new features. Eleven new oneAPI Centers of Excellence were launched around the world last year. And finally, oneAPI won yet another HPCwire Reader's Choice Award, this time for <u>2021 Best HPC</u> <u>Programming Tool or Technology</u>. That's a lot of momentum going into 2022.

#### Our feature article in this issue, Vectorization in

**LLVM and GCC for Intel CPUs and GPUs**, describes how single instruction, multiple data (SIMD) support is evolving in modern compilers. The authors show examples of automatic vectorization, programmer-guided vectorization, and a data parallel library approach.

**Efficient Heterogeneous Parallel Programming Using OpenMP** shows some best practices to keep both the CPU and GPU working at the same time. The authors provide advice and code examples to express true asynchronous, heterogeneous parallelism using standard OpenMP directives.

In the spectrum of <u>separation of concerns</u>, I'm more of a domain scientist than a performance tuning engineer, so I'm interested in programming abstractions that deliver performance while hiding hardware details. Lately, I've been experimenting with the <u>ArrayFire</u> heterogeneous parallel library. The results have been good in terms of productivity and performance. I plan to write an article about my experiments for a future issue, but in the meantime, Stefan Yurkevitch (ArrayFire, Software Engineer) discusses **ArrayFire Interoperability with oneAPI and OpenCL**<sup>™</sup> in this issue.

From high-level software abstractions for heterogeneous parallelism, we go lower in the stack to hardware abstractions with **Using the oneAPI Level Zero Interface**.

We close this issue with three data science articles. The first shows how to do efficient

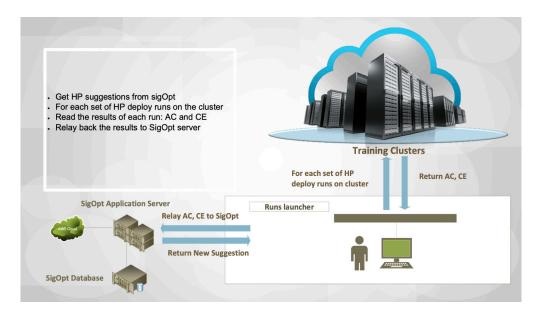

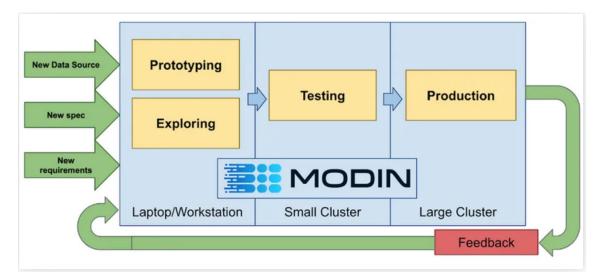

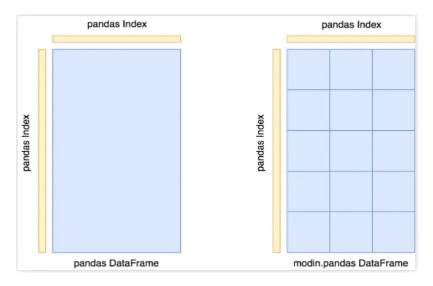

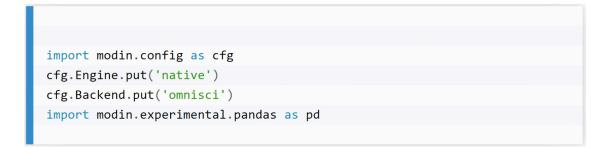

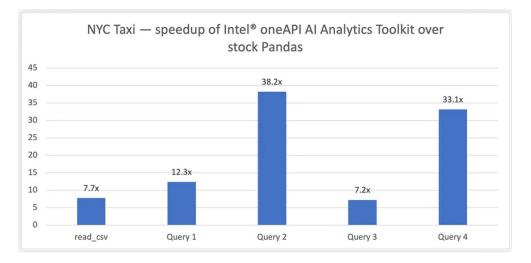

Hyperparameter Optimization with SigOpt for MLPerf<sup>™</sup> Training on Habana<sup>®</sup> Gaudi<sup>®</sup> while also achieving better model accuracy. The next article describes how to Scale Your Pandas Workflow with Modin – no recoding necessary. The final article, From Ray to Chronos, shows how to build scalable, end-to-end AI workflows with BigDL on top of Ray.

As always, don't forget to check out <u>Tech.Decoded</u> for more information on Intel solutions for code modernization, visual computing, data center and cloud computing, data science, systems and IoT development, and heterogeneous parallel programming with oneAPI.

Henry A. Gabb January 2021

## Vectorization in LLVM and GCC for Intel CPUs and GPUs

SIMD Support Is Evolving Rapidly in Modern Compilers

Xinmin Tian, Senior Principal Engineer, Hideki Saito, Principal Engineer, Hongtao Liu, Compiler Engineer, James Reinders, oneAPI Evangelist and Editor Emeritus of The Parallel Universe, Intel Corporation

Modern CPU and GPU cores use single instruction, multiple data (SIMD) execution units to achieve higher performance and power efficiency. The underlying SIMD hardware is exposed via instructions such as SSE, AVX, AVX2, AVX-512, and those in the Intel<sup>®</sup> X<sup>e</sup> Architecture Gen12 ISA. While using these directly is an option, their low-level nature severely limits portability and proves unattractive for most projects.

To provide a more portable and easier to use interface for programmers, three avenues are explored in this article: auto-vectorization, programmer-guided SIMD vectorization through language constructs or programmer hints, and a SIMD data-parallel library approach. We provide an overview of these methods and show SIMD vectorization evolution in the LLVM and GCC compilers through code examples. We also examine a couple of vectorization techniques in the LLVM and GCC compilers to achieve optimal performance on Intel<sup>®</sup> Xeon<sup>®</sup> processors and Intel X<sup>e</sup> Architecture GPUs.

#### Enhancing LLVM and GCC

Our goal is to enhance vectorization of both the LLVM and GCC compilers, so contributing to open source has been a key design consideration. The VPlan vectorizer, and the related VectorABI, have been designed so they are applicable for integration into both LLVM and GCC [13] optimizers.

The framework for the VPlan vectorizer may be integrated into the LLVM trunk. Our VectorABI [12] is published and is being utilized by the LLVM and GCC communities for function vectorization. The VPlan vectorizer has started to surpass the results previously provided by the proprietary Intel compilers for Intel Xeon processors.

#### **Utilizing SIMD**

Modern CPUs support SIMD execution. SIMD is a hardware feature for a wavefront parallel execution of a single instruction over multiple data elements. It is useful for operating on multiple pieces of data at once given that their control flow is similar (minimal vector divergence) and the operation is not memory-bound. Unfortunately, writing a program that directly uses the SIMD ISA is not straightforward and has limited portability. We will discuss three approaches to improve this situation for programmers: auto-vectorization, programmer-guided SIMD vectorization through hints or language constructs, and using the C++ SIMD data-parallel library.

#### **Auto-Vectorization**

Automatically performing data- and control-dependency analysis and converting a scalar program to a corresponding vector form based on a built-in cost model is called auto-vectorization [4][5]. While the simplicity of this approach is attractive to programmers for its productivity and portability, auto-vectorization does not always produce optimal code because of compile-time unknowns like loop bounds and memory access patterns.

#### **Programmer-Guided SIMD Vectorization**

OpenMP (version 4.0 and later) includes SIMD constructs to support vector-level parallelism [7]. These constructs provide a standardized set of vector constructs so programmers no longer need to use non-portable, vendor-specific intrinsics or directives [6]. In addition, these constructs provide additional hints about the code structure to the compiler and allow for better vectorization that blends well with parallelization [5].

#### C++ SIMD Data-Parallel Library

There is an ISO C++ proposal for a data-parallel library [3]. Its intent is to support acceleration through data-parallel execution resources such as SIMD registers and instructions or execution units driven by a common instruction decoder. If such execution resources are unavailable, the interfaces support a

transparent fallback to sequential execution. A SIMD memcpy example using the C++ SIMD data-parallel library is shown in Figure 1. This example can be compiled to generate LLVM Vector IR and binary for core-avx512.

```

define void @_Z11simd_memcpy_Pv(<16 x float> %x.coerce,

namespace stdsimd = std::experimental;

<16 x float> %y.coerce, i8*

void simd memcpy(

nocapture %p)

stdsimd::native simd<float> x,

{

stdsimd::native_simd<float> y,

entry:

void *p)

%0 = fcmp fast olt <16 x float> %x.coerce, %y.coerce

{

%cmp.sroa.0.sroa.0.0.p.sroa_cast = bitcast i8* %p to <16 x i1>*

auto cmp = x < y;

store <16 x i1> %0, <16 x i1>* %cmp.sroa.0.sroa.0.0.p.sroa cast

memcpy(p, &cmp, cmp.size()*4);

ret void

}

}

```

#### Figure 1. An example of the C++ SIMD data-parallel library

The SIMD vectorization is critical to delivering optimal performance of compute-intensive workloads on modern CPUs and GPUs regardless of which vectorization method is used to produce SIMD code. In the next sections, we present recent LLVM SIMD vectorization advances for CPUs and GPUs with more code examples.

#### LLVM VPlan Vectorization

#### **VPlan Vectorizer**

Intel LLVM Compiler introduces a newly designed loop vectorizer aimed at matching or exceeding the capability and performance of the vectorizer in Intel Classic Compiler. The new vectorizer is often referred to as VPlan Vectorizer after the name of its major internal data structure, VPlan (vectorization plan), to distinguish it from the LLVM community Loop Vectorizer (a.k.a. LV). LORE and RAJAPerf experiments show that Intel LLVM Compiler can generate equivalent or better performing code than Intel Classic Compiler for a variety of computational kernels extracted from HPC applications [9]. At the time of writing, Intel LLVM Compiler enables VPlan Vectorizer for auto-vectorization at -O2 or higher optimization plus the -x (/Qx for Windows) target flag. Without the -x flag, the community Loop Vectorizer will be used. VPlan Vectorizer is enabled at -O0 or higher for OpenMP SIMD when Intel's OpenMP implementation is enabled with the -qopenmp (/Qopenmp for Windows) flag. At the time of writing, many of frequently used OpenMP 4.5 SIMD features are functional and performant. We continue our efforts to support the latest OpenMP 5.2 SIMD features.

Figure 2 shows how a simple outer loop (left column) is vectorized by Intel Classic Compiler (icc, center column) and Intel LLVM Compiler (icx, right column). Overall ASM code generated by Intel Classic Compiler looks more concise and easier to follow, but Intel LLVM Compiler generates noticeably better ASM code for the inner while-loop (basic block .LBB0\_7 for icx versus ..B1.7 for icc) due to its better handling of the inner loop execution condition in the %k1 mask register.

```

void foo(int N, float *a,

icc -02 -qopenmp-simd -xCORE-

icx -O2 -qopenmp-simd -xCORE-

AVX512 -c -S -unroll0

AVX512 -c -S -unroll0

float *b, float *c) {

#pragma omp simd

..B1.5:

.LBB0 4

for (int i=0;i<N;i++) {</pre>

ami

vmovups (%rsi,%r8,4), %ymml

.LBB0 5:

float x = a[i];

float y = b[i];

vmovups (%rdx,%r8,4), %ymm0

vxorps %xmm2, %xmm2, %xmm2

vcmpps $14, %ymm0, %ymm1, %k1

.LBB0 8:

while(x>y){

kortestw %k1, %k1

vcmpltps %ymm0, %ymm1, %k1

x = x^*x;

..B1.9

vmovaps %ymm2, %ymm0 {%k1}

}

je

..B1.6:

vmovups %ymm0, (%rcx,%rax,4)

c[i] = x;

%k1, %k0

kmovw

addq $8, %rax

}

..B1.7:

%rdi, %rax

cmpq

}

%k0, %k1, %k2

.LBBO 9

kandw

jae

vmulps %ymm1, %ymm1, %ymm1{%k2}

.LBB0 4:

vcmpps $14, %ymm0, %ymm1, %k3

vmovups (%rsi,%rax,4), %ymm0

vmovups (%rdx,%rax,4), %ymm1

kandw %k3, %k2, %k4

kandw %k0, %k4, %k0

vcmpltps %ymm0, %ymm1, %k0

..B1.7

jne

kortestb %k0, %k0

..B1.9:

je .LBBO 5

add]

$8, %r9d

# %bb.6:

vmovups %ymm1, (%rcx,%r8,4)

vmovaps %ymm0, %ymm3

addq

kmovq %k0, %k1

$8, %r8

cmpl

%eax, %r9d

.LBB0 7:

jb

..B1.5

vmulps %ymm3, %ymm3, %ymm3

vmovaps %ymm3, %ymm2 {%k1}

vcmpltps %ymm3, %ymm1, %k1 {%k1}

ktestb %k0, %k1

jne .LBB0_7

jmp .LBB0_8

```

Figure 2. Outer loop vectorization using VPlan Vectorizer

#### **Kernel and Function Vectorization**

Intel LLVM Compiler implements DPC++/OpenCL kernel vectorization and OpenMP function vectorization through VPlan vectorizer [5][10]. This is accomplished by converting a function vectorization problem into a loop vectorization problem. Customers can expect that most of the optimizations implemented for vectorizing loops are also available to vectorizing kernels/functions.

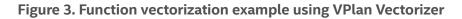

Figure 3 is an equivalent vectorization expressed in OpenMP declare SIMD directive form [7]. An 8-way non-mask vectorized AVX-512 vector variant function (\_ZGVcN8luuu\_bar) is shown. Even though the basic block layout is different, and the outer loop control flow is naturally absent because the compiler knows it is vectorizing for "8-instances" of the function bar, the rest of the ASM code is strikingly similar to icx-generated ASM code in the loop vectorization example (Figure 2) because it is vectorized by the same VPlan Vectorizer by letting the compiler inject an 8-iteration loop around the function body.

```

#pragma omp declare simd \setminus

icx -O2 -qopenmp-simd -xCORE-AVX512 -c -S -unroll0

linear(i) uniform(a,b,c)

_ZGVcN8luuu_bar:

void bar(int i, float *a, float *b, float *c){

movslq %edi, %rax

float x = a[i];

vmovups (%rsi,%rax,4), %ymm0

float y = b[i];

vmovups (%rdx,%rax,4), %ymm1

while(x>v){

vcmpltps %ymm0, %ymm1, %k1

x = x^*x;

kortestb %k1, %k1

}

je .LBB3_1

c[i] = x;

# %bb.2:

}

vcmpltps %ymm0, %ymm1, %k0

vmovaps %ymm0, %ymm3

.LBB3_3:

vmulps %ymm3, %ymm3, %ymm3

vmovaps %ymm3, %ymm2 {%k1}

vcmpltps %ymm3, %ymm1, %k1 {%k1}

ktestb %k0, %k1

jne .LBB3_3

.LBB3 4

jmp

.LBB3 1:

vxorps %xmm2, %xmm2, %xmm2

.LBB3 4:

vcmpltps %ymm0, %ymm1, %k1

vmovaps %ymm2, %ymm0 {%k1}

vmovups %ymm0, (%rcx,%rax,4)

vzeroupper

retq

```

#### **New ISA Support**

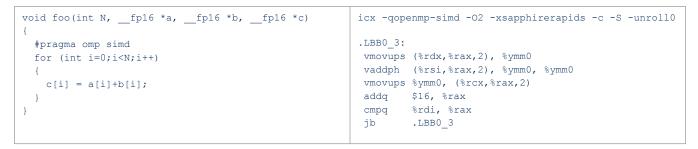

One of the benefits of implementing a vectorizer on the LLVM compiler framework is first-class support of vector data types. When AVX-512-FP16 [11] was introduced, the vectorizer was able to take advantages of it as soon as the ASM/OBJ code generation support was added, giving vectorizer developers a pleasant surprise. Figure 4 is a simple FP16 vectorization example.

#### Figure 4. FP16 vectorization example (I) using VPlan Vectorizer

Note that not all optimizers work well out-of-the-box for the newly introduced instruction set. Figure 5 is the same example from Figure 2 but using the FP16 data type. The innermost loop with the vmulph instruction is currently not as nicely optimized as in Figures 2 and 3. In the upcoming releases, we'll continue uncovering and improving these issues.

```

void foo(int N, __fp16 *a, __fp16 *b, __fp16 *c)

icx -qopenmp-simd -O2 -xsapphirerapids -c -S -unroll0

jmp

.LBB0_4

#pragma omp simd

.LBB0 5:

for (int i=0;i<N;i++)</pre>

vpxor %xmm2, %xmm2, %xmm2

__fp16 x = a[i];

.LBB0 12:

vcmpltph

%ymm0, %ymm1, %k1

fp16 v = b[i];

vmovdqu16 %ymm2, %ymm0 {%k1}

while(x>y)

vmovdqu %ymm0, (%rcx,%rax,2)

{

addq $16, %rax

x = x^*x;

cmpq %rdi, %rax

jae .LBB0_13

}

c[i] = x;

.LBB0 4:

}

vmovups (%rsi,%rax,2), %ymm0

}

vmovups (%rdx,%rax,2), %ymm1

vcmpltph %ymm0, %ymm1, %k0

kortestw

%k0, %k0

je .LBB0_5

# %bb.6:

vmovaps %ymm0, %ymm3

kmovq %k0, %k1

jmp

.LBB0 7

.LBB0 11:

vmovdqul6 %ymm3, %ymm2 {%k1}

kandw %k1, %k2, %k1

ktestw %k0, %k1

je .LBB0_12

.LBB0 7:

ktestw %k1, %k0

vmulph %ymm3, %ymm3, %ymm4

vxorps %xmm3, %xmm3, %xmm3

je .LBB0_9

# %bb.8:

vmovaps %ymm4, %ymm3

.LBB0 9:

kxorw %k0, %k0, %k2

je .LBB0_11

# %bb.10:

vcmpltph %ymm4, %ymm1, %k2

jmp .LBB0_11

```

#### Figure 5. FP16 vectorization example (II) using VPlan Vectorizer

#### **Enhancing Auto-Vectorization in GCC12**

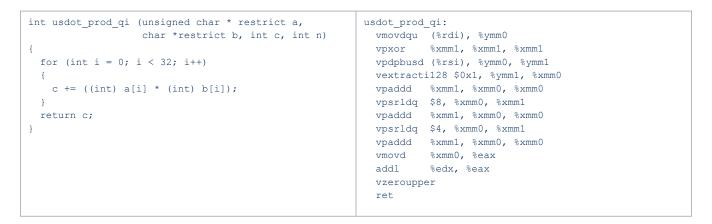

In this section, we describe several auto-vectorization enhancements developed recently for AVX-512/ AVX-512-VNNI support in GCC12 compiler based on GCC vectorization framework previously done for Intel Xeon Phi processors.

• GCC12 auto-vectorization is enabled by default at -O2 using a "cheap" cost model, which permits loop vectorization if the trip count of a scalar vectorizable loop is a multiple of the hardware vector length, and with no observable code size increasing. For example, Figure 6 shows an example of GCC -O2 auto-vectorization using SSE4.2. Meanwhile, the default cost model for loop vectorization at -O3 employs a "dynamic" model with more checkpoints to determine whether the vectorized code path will achieve performance gains.

```

void ArrayAdd(int* __restrict a, int* b)

ArravAdd:

xorl %eax, %eax

{

for (int i = 0; i != 32; i++)

.L2:

a[i] += b[i];

movdqu (%rdi,%rax), %xmm0

}

movdqu (%rsi,%rax), %xmm1

paddd %xmm1, %xmm0

movups %xmm0, (%rdi,%rax)

addq $16, %rax

$128, %rax

cmpq

jne

.L2

ret

```

#### Figure 6. GCC (-O2) auto-vectorization example

GCC vectorization for the \_Float16 type is enabled to generate corresponding AVX512FP16 instructions. In addition to those SIMD instructions that are similar to their float/double variants, the vectorizer also supports vectorization for the complex \_Float16 type. Figure 7 shows an example that performs a conjugate complex multiply and accumulate operations on three arrays, and the vectorizable loop can be optimized to generate a vfcmaddcph instruction.

| <pre>#include<complex.h></complex.h></pre>                               | fmaconj:                                                                                                                       |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| <pre>void fmaconj (_Complex _Float16 a[restrict 16],</pre>               | <pre>vmovdqul6 (%rdx), %zmml<br/>vmovdqul6 (%rsi), %zmm0<br/>vfcmaddcph (%rdi), %zmm1, %zmm0<br/>vmovdqul6 %zmm0, (%rdx)</pre> |

| <pre>{   for (int i = 0; i &lt; 16; i++)     c[i] += a[i] * ~b[i];</pre> | vzeroupper<br>ret                                                                                                              |

| }                                                                        |                                                                                                                                |

#### Figure 7. GCC auto-vectorization of using the AVX512FP16 vfcmaddcph instruction

• GCC auto-vectorization is enhanced to perform idiom recognition such as the dot-plus idiom, which triggers the AVX/AVX512VNNI instruction generation. Figure 8 shows that the compiler generates the vpdpbusd instruction plus a summation reduction.

Figure 8. AV512VNNI idiom recognition in GCC auto-vectorization

In addition to the three aforementioned enhancements in GCC auto-vectorization, we have improved GCC to utilize <code>vpopcnt[b,w,d,q]</code> instructions when the redundant zero extension and truncation is recognized by the vectorizer as well. These improvements significantly extend GCC auto-vectorization capability for Intel Xeon Scalable processors.

#### SIMD Vectorization for Intel GPUs

#### **Design Rationale**

Intel GPUs, using Intel X<sup>e</sup> Architecture, are designed to support both OpenCL SIMT (Single Thread Multiple Data) and SIMD. In this section, we describe how to enable our LLVM VPlan vectorizer for converting OpenMP SIMD loops to SIMD code by leveraging underlying SIMD ISA in X<sup>e</sup> GPUs. The rationale behind the design and implementation is two-fold:

- Provide a relatively smooth transition to migrate existing C++ and Fortran OpenMP CPU applications that uses SIMD constructs to X<sup>e</sup> GPUs utilizing OpenMP offloading and SIMD.

- Exploit SIMD loop vectorization flexibility with different explicit SIMD schemes in the OpenMP offloading region to fully leverage X<sup>e</sup> GPU SIMD ISA.

The oneAPI C++/Fortran OpenMP compiler SIMD vectorization for Intel GPUs is designed to exploit the underlying hardware features, allowing fine-grained register management, SIMD size control, and cross-lane data sharing.

#### **High-Level SIMD Vectorization Framework**

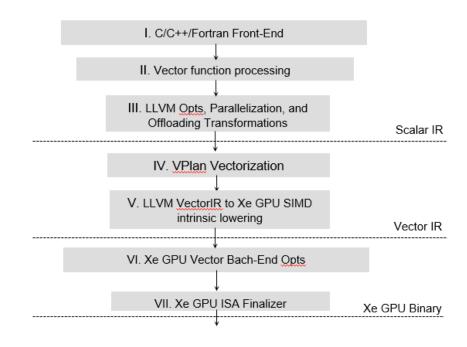

Figure 9 outlines the SIMD vectorization framework implemented in the device compilation path for Intel GPUs, which fully leverages the LLVM VPlan Vectorizer we built for CPUs [4][5] in oneAPI compilers. The VPlan Vectorizer (box IV) takes LLVM scalar IR from the language Front-End (box I) and middle end optimizations (boxes II and III) performing LLVM Vector IR generation in conjunction with a lowering transformation to GPU target intrinsics defined for X<sup>e</sup> GPU operations (box V). Then, passing GPU-ready LLVM Vector IR to the GPU Vector Back-End compiler (boxes VI and VII) [8] using SPIR-V as an interface IR.

Figure 9. SIMD vectorization framework for device compilation

There is a sequence of explicit SIMD-specific optimizations and transformations (box VI) developed around those GPU-specific intrinsics. Note that programmers are provided with controls on loop vectorization and vector length selection through OpenMP programming APIs while the compiler Vector Back-End (boxes VI and VII) strives to achieve a tradeoff among various compiler optimizations based on programmer annotations. In addition, OpenMP explicit SIMD kernels generated by the compiler middle end are fully compatible with the Intel GPU OpenCL runtime [1] and oneAPI Level Zero [2] and can be launched directly as if they are written in OpenCL.

#### Intel X<sup>e</sup> Architecture GPU SIMD Code Generation Example

Figure 10 shows an OpenMP offload example. In the target region, there are two SIMD loops: one operates on single-precision multiply-and-add (FMA) with simdlen(8) and the other operates on double-precision multiply-and-add with the simdlen(8) clause. So, the compiler can perform 512-bit SIMD vectorization for both loops.

```

Float a[N][M]; double b[N][M];

....

#pragma omp target teams distribute parallel for map(tofrom:a[0:N][0:M]) map(tofrom:b[0:N][0:M])

for (int k = 0; k < N; ++k) {

float x = k * 1.0f;

double y = k * 1.0;

#pragma omp simd simdlen(16)

for (int j = 0; j < M; ++j) {

a[k][j] = a[k][j] + x*a[k][j];

}

#pragma omp simd simdlen(8)

for (int j = 0; j < M; ++j) {

b[k][j] = b[k][j] + y*b[k][j];

}

}

. . . . . . .

```

#### Figure 10. An example with different SIMD width in OpenMP target region

For SIMD loop vectorization, if a loop trip count is known at compile-time, the compiler can decide to unroll the loop. In this program example, the first SIMD loop is vectorized with SIMD16 and unrolled by two, the second SIMD loop is vectorized with SIMD8 and unrolled by four for the given trip count M=32 as shown in Figure 11. A common issue to compilers is that the loop trip count is unknown at compile-time. However, if application programmers can reason about and predict the trip count and provide a hint to the compilers using #pragma loop count, it will enable the compiler to perform the desired loop unrolling for compute-bound loops (i.e., computation takes more time than memory accesses).

|                 | M0)      | r7.0<   | 1>:f     | r5.0< | 1;0>:f     | r5.0< | <1;0>:f r1.6<0>:f {Compacted,\$8.dst} |

|-----------------|----------|---------|----------|-------|------------|-------|---------------------------------------|

| (W&f1.0.any16h) | send.dc1 | (16 MO) | null     | r33   | r7         | 0x80  | 0x020D43FF {\$3}                      |

| (W&f1.0.any16h) | send.dc1 | (16 MO) | r9       | r34   | null       | 0x0   | 0x022D0BFF {\$9}                      |

| mad (16         | M0)      | r11.0   | <1>:f    | r9.0< | 1;0>:f     | r9.0< | <1;0>:f r1.6<0>:f {Compacted,\$9.dst} |

| (W&f1.0.any16h) | send.dc1 | (16 M0) | null     | r35   | r11        | 0x80  | 0x020D43FF {A@1,\$6}                  |

| (W&f1.0.any16h) | send.dc1 | (16 MO) | r13      | r36   | null       | 0x0   | 0x022D0BFF {\$10}                     |

| mad (8 1        | 40)      |         | r15.0<12 | >:df  | r13.0<1;0> | >:df  | r13.0<1;0>:df r4.2<0>:df {\$10.dst}   |

| (W&f1.0.any16h) | send.dc1 | (16 MO) | null     | r37   | r15        | 0x80  | 0x020D43FF                            |

| (W&f1.0.any16h) | send.dc1 | (16 M0) | r17      | r38   | null       | 0x0   | 0x022D0BFF                            |

| mad (8 1        | 40)      |         | r19.0<12 | >:df  | r17.0<1;0> | >:df  | r17.0<1;0>:df r4.2<0>:df {\$11.dst}   |

| (W&f1.0.any16h) | send.dc1 | (16 M0) | null     | r39   | r19        | 0x80  | 0x020D43FF {A@1,\$4}                  |

| (W&f1.0.any16h) | send.dc1 | (16 M0) | r22      | r40   | null       | 0x0   | 0x022D0BFF {\$12}                     |

| mad (8 1        | 40)      |         | r24.0<12 | >:df  | r22.0<1;0> | >:df  | r22.0<1;0>:df r4.2<0>:df {\$12.dst}   |

| (W&f1.0.any16h) | send.dc1 | (16 M0) | null     | r41   | r24        | 0x80  | 0x020D43FF {A@1,\$7}                  |

| (W&f1.0.any16h) | send.dc1 | (16 M0) | r26      | r42   | null       | 0x0   | 0x022D0BFF {\$13}                     |

| mad (8 1        | 40)      |         | r28.0<12 | >:df  | r26.0<1;0> | >:df  | r26.0<1;0>:df r4.2<0>:df {\$13.dst}   |

| (W&f1.0.any16h) | send.dc1 | (16 MO) | null     | r43   | r28        | 0x80  | 0x020D43FF {A@1,\$5}                  |

|                 |          |         |          |       |            |       |                                       |

|                 |          |         |          |       |            |       |                                       |

Figure 11. Intel GPU SIMD code generated with unrolling based on data types

#### Summary

We presented the recent evolution of SIMD vectorization technology in the LLVM and GCC compilers for underlying Intel CPU and Intel GPU ISAs. Several vectorization features are illustrated for how to expose the underlying hardware capabilities to exploit SIMD parallelism. On Intel GPUs, SIMD vectorization is a complementary to the existing popular SPMD model. As a continuous effort, more performance tuning and optimizations will be added into Intel oneAPI LLVM-based compilers and GCC compilers for Intel CPUs AVX-512 and AVX-512-FP16/VNNI ISA and Intel GPUs Gen12 ISA.

#### References

- [1] Intel, Intel<sup>®</sup> Graphics Compute Runtime for oneAPI Level Zero and OpenCL Driver, https://github.com/intel/compute-runtime, 2020.

- [2] Intel, oneAPI Level Zero Specification, 2020. https://spec.oneapi.com/level-zero/latest/index.html

- [3] C++ Standards Committee, Data-parallel vector library, 2020. https://en.cppreference.com/w/cpp/experimental/simd

- [4] H. Saito, S. Preis, N. Panchenko, and X. Tian. Reducing the Functionality Gap between Auto-Vectorization and Explicit Vectorization. In Proceedings of the International Workshop on OpenMP (IWOMP), LNCS9903, pp. 173-186, Springer, 2016.

- [5] X. Tian, H. Saito, E. Su, J. Lin, et.al. LLVM Compiler Implementation for Explicit Parallelization and SIMD Vectorization. LLVM-HPC@SC 2017: 4:1-4:11

- [6] X. Tian, R. Geva, B. Valentine. Unleash the Power of AVX-512 through Architecture, Compiler and Code Modernization, ACM Parallel Architecture and Compiler Technology, September 11-15, 2016, Haifa, Israel.

- [7] X. Tian, Bronis R. de Supinski: Explicit Vector Programming with OpenMP\* 4.0 SIMD Extensions, HPC Today America, Nov 19. 2014. http://www.hpctoday.com/hpc-labs/explicit-vector-programming-withopenmp-4-0-simd-extensions/

- [8] Guei-Yuan Lueh, Kaiyu Chen, Gang Chen, Joel Fuentes, Wei-Yu Chen, Fangwen Fu, Hong Jiang, Hongzheng Li, and Daniel Rhee, C-for-Metal: High Performance SIMD Programming on Intel GPUs. CGO 2021, 289-300.

- [9] "Intel C/C++ compilers complete adoption of LLVM" <u>https://www.intel.com/content/www/us/en/</u> <u>developer/articles/technical/adoption-of-llvm-complete-icx.html</u>

#### < The Parallel Universe

- [10] Matt Masten, Evgeniy Tyurin, K. Mitropoulou, Eric N. Garcia, and H. Saito Function/Kernel Vectorization via Loop Vectorizer, 2018 IEEE/ACM 5th Workshop on the LLVM Compiler Infrastructure in HPC (LLVM-HPC)

- [11] Intel AVX-512-FP16 Architecture Specification <u>https://software.intel.com/content/dam/develop/</u> <u>external/us/en/documents-tps/intel-avx512-fp16.pdf</u>

- [12] Intel Corporation, Vector Function Application Binary Interface <u>https://docplayer.net/197118571-</u> Vector-function-application-binary-interface.html

- [13] GCC patches can be found under https:/gcc.gnu.org/git (look for AVX512/VNNI/FP16 support), see also <u>https://www.phoronix.com/scan.php?page=news\_item&px=AFX-512-FP16-GCC-Patches</u> for more on FP16 patches.

Diverse Workloads Require Diverse Architectures

Develop heterogeneous applications quickly and correctly with Intel oneAPI toolkits. Explore Toolkits >

## Efficient Heterogeneous Parallel Programming Using OpenMP

Best Practices to Keep the CPU and GPU Working at the Same Time

Elmira Volkova, Undergraduate Intern, Alexander Bobyr, Software Enabling and Optimization Engineer, Igor Ermolaev, Principal Engineer

In some cases, offloading computations to an accelerator like a GPU means that the host CPU sits idle until the offloaded computations are finished. However, using the CPU and GPU resources simultaneously can improve the performance of an application. In OpenMP<sup>®</sup> programs that take advantage of heterogenous parallelism, the *master* clause can be used to exploit simultaneous CPU and GPU execution. In this article, we will show you how to do CPU+GPU asynchronous calculation using OpenMP.

The SPEC ACCEL <u>514.pomriq</u> MRI reconstruction benchmark is written in C and parallelized using OpenMP. It can offload some calculations to accelerators for heterogenous parallel execution. In this article, we divide the computation between the host CPU and a discrete Intel® GPU such that both processors are kept busy. We'll also use Intel VTune<sup>™</sup> Profiler to measure CPU and GPU utilization and analyze performance.

We'll look at five stages of heterogeneous parallel development and performance tuning:

- 1. Looking for appropriate code regions to parallelize

- 2. Parallelizing these regions so that both the CPU and GPU are kept busy

- 3. Finding the optimal work distribution coefficient

- 4. Launching the heterogeneous parallel application with this distribution coefficient

- 5. Measuring the performance improvement.

Initially, the parallel region only runs on the GPU while the CPU sits idle (Figure 1). As you can see, only the "OMP Primary Thread" is executing on the CPU while the GPU is fully occupied (GPU Execution Units→EU Array→Active) with the ComputeQ offloaded kernel.

| G      | GPU Offload GPU Offloa                          | id 🔹 🕐  |                                                                |                  |                                                                                     |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |                                                                    |

|--------|-------------------------------------------------|---------|----------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------|

| A      | nalysis Configuration Collecti                  | ion Log | Summary Graphics P                                             | latform          |                                                                                     |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |                                                                    |

| Queue  | 𝒫: + - ☞ ☞           Intel(R) Graphics [0x020a] | 0s      | 5s [<br>main\$omp\$offloading:237<br>main\$omp\$offloading:237 | 8.31s 10         | 0s 15s<br>I I I I I I I I I I I I I I I I I I I                                     | 20s                                           | 255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 305                           | GPU Computing Queue     GPU Computing Task     GPU Computing Queue |

| Thread | OMP Primary Thread #0 (TI                       |         |                                                                |                  | ) Graphics [0x020a]                                                                 | المعالمة والمعالمة المعالم                    | 1997), 1 dl . 10 B B 1 B 1 B 1 B 1 B 1 B 1 B 1 B 1 B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               | Thread     Imread     Imread     Imread                            |

|        | OMP Worker Thread #150 (                        |         |                                                                | Start: 2         | Computing Queue<br>2.396s Duration: 26.81s<br>uting Task: main\$omp\$offloading:237 | 1 <b>14.1 16.1</b>                            | muun fin eine fin finsen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A films and the second second | ✓ ▲ CPU Time ✓ □ User Tasks ✓ □ GPU Computing Task                 |

|        | OMP Worker Thread #151 (                        |         | η                                                              | Purpos<br>Thread | se: Compute<br>d: OMP Worker Thread #8 (TID: 26465)                                 | لى <b>لا</b> رىن خايدان قىدىنى ئىتىرىتىتىنى ت | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               | GPU Execution Units                                                |

|        | OMP Worker Thread #149 (                        |         |                                                                |                  | l Size: 1363200<br>Size: 64                                                         | ويتارز ويعيد والمطري والمتقرية والمتعارية     | land of states and the states of the states | ····                          | EU Arrays                                                          |

| nits   | GPU Tile 0                                      |         |                                                                |                  |                                                                                     |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               | 🗹 📥 Stalled                                                        |

Figure 1. Profile of the initial code using Intel VTune Profiler

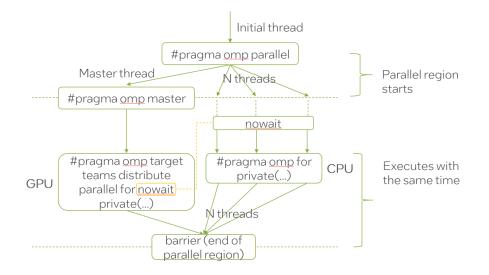

After examining the code, we decided to duplicate each array and each executed region so that the first copy is executed on the GPU and the second is executed on the CPU. The master thread uses the OpenMP *target* directive to offload work to the GPU. This is shown schematically in Figure 2. The *nowait* directives avoid unnecessary synchronization between the threads running on the CPU and GPU. They also improve load balance among the threads.

Figure 2. OpenMP parallelization scheme to keep the CPU and GPU busy

Balancing the work distribution between the CPU and GPU is regulated by the *part* variable that is read from STDIN (Figure 3). This variable is the percentage of the workload that will be offloaded to the GPU multiplied by *numX*. The remaining work will be done on the CPU. An example of the OpenMP heterogeneous parallel implementation is shown in Figure 4.

```

float part;

char *end;

part = strtof(argv[2], &end);

int TILE_SIZE = numX*part;

Qrc = (float*) memalign(alignment, numX * sizeof (float));

Qrg = (float*) memalign(alignment, TILE_SIZE * sizeof (float));

```

Figure 3. The coefficient of distribution work between the CPU and GPU

```

#pragma omp parallel

{

#pragma omp master

#pragma omp target teams distribute parallel for nowait private(expArg, cosArg, sinArg)

for (indexX = 0; indexX < TILE_SIZE; indexX++) {</pre>

float OrSum = 0.0;

float QiSum = 0.0;

#pragma omp simd private(expArg, cosArg, sinArg) reduction(+:QrSum, QiSum)

for (indexK = 0; indexK < numK; indexK++) {</pre>

expArg = PIx2 * (GkVals[indexK].Kx * xg[indexX] + GkVals[indexK].Ky * yg[indexX] + GkVals[indexK].Kz * zg[indexX]);

cosArg = cosf(expArg);

sinArg = sinf(expArg);

float phi = GkVals[indexK].PhiMag;

QrSum += phi * cosArg;

QiSum += phi * sinArg;

Qrg[indexX] += QrSum;

Qig[indexX] += QiSum;

#pragma omp for private(expArg, cosArg, sinArg)

for (indexX = TILE_SIZE; indexX < numK; indexX++) {</pre>

float OrSum = 0.0;

float QiSum = 0.0;

#pragma omp simd private(expArg, cosArg, sinArg) reduction(+:QrSum, QiSum)

for (indexK = 0; indexK < numK; indexK++) {</pre>

expArg = PIx2 * (CkVals[indexK].Kx * xc[indexX] + CkVals[indexK].Ky * yc[indexX] + CkVals[indexK].Kz * zc[indexX]);

cosArg = cosf(expArg);

sinArg = sinf(expArg);

float phi = CkVals[indexK].PhiMag;

QrSum += phi * cosArg;

QiSum += phi * sinArg;

Qrc[indexX] += QrSum;

Qic[indexX] += QiSum;

```

### Figure 4. Example code illustrating the OpenMP implementation that simultaneously utilizes the CPU and GPU

The Intel<sup>®</sup> oneAPI DPC++/C++ Compiler was used with following command-line options:

```

-O3 -Ofast -xCORE-AVX512 -mprefer-vector-width=512 -ffast-math

-qopt-multiple-gather-scatter-by-shuffles -fimf-precision=low

-fiopenmp -fopenmp-targets=spir64="-fp-model=precise"

```

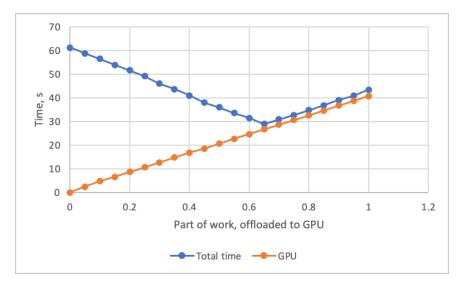

Table 1 shows the performance for different CPU to GPU work ratios (i.e., the *part* variable described above). For our system and workload, an offload ratio of 0.65 gives the best load balance between the CPU and GPU, and hence the best utilization of processor resources. The profile from Intel VTune Profiler shows that work is more evenly distributed between the CPU and GPU, and that both processors are being effectively utilized (Figure 5). While "OMP Primary Thread" submits the offloaded kernel (main: 237) for execution on the GPU, other "OMP Worker Threads" are active on the CPU.

| Offload part | Total time, s | GPU time, s |

|--------------|---------------|-------------|

| 0.00         | 61.2          | 0.0         |

| 0.20         | 51.6          | 8.6         |

| 0.40         | 41.0          | 16.8        |

| 0.60         | 31.5          | 24.7        |

| 0.65         | 28.9          | 26.7        |

| 0.80         | 34.8          | 32.6        |

| 1.00         | 43.4          | 40.7        |

Table 1. Hotspot times corresponding to different amounts of offloaded work (i.e., the part variable)

| Analysis Configuration Collection Log Summary Graphics F                             | Platform   |              |         |                 |                             | //         |

|--------------------------------------------------------------------------------------|------------|--------------|---------|-----------------|-----------------------------|------------|

| Grouping: Thread / Function / Call Stack                                             |            |              |         |                 | ~                           | 🛠 વિ ୟ     |

| Thread / Function / Call Stack                                                       | CPU Time 🔻 | Task Count   | Module  | Function (Full) | Source File                 | Start Ad   |

| ▶ [Import thunk sched_yield]                                                         | 0.003s     |              | libiomp | [Import thunk   |                             | 0x27890    |

| ▶kmp_yield                                                                           | 0.001s     |              | libiomp | kmp_yield       | z_Linux_u                   | 0x1414f    |

| OMP Worker Thread #35 (TID: 12946)                                                   | 27.544s    |              |         |                 |                             | 0          |

| svml_cospif16_ep_z0                                                                  | 10.875s    |              | a.out   | svml_cosp       |                             | 0x4055b    |

| main.DIR.OMP.PARALLEL.25                                                             | 8.215s 🛑   |              | a.out   | main.DIR.O      |                             | 0x4050e    |

| svml_sinpif16_ep_z0                                                                  | 4.062s 📒   |              | a.out   | svml_sinpi      |                             | 0x40564    |

| init_scratch_end                                                                     | 2.589s 🛢   |              | vmlinux | init_scratc     |                             | 0xfffffff8 |

| _kmp_execute_tasks_64<(bool)0, (bool)1>                                              | 0.961s     |              | libiomp | intkmp_ex       | kmp_taski                   | 0xf7d20    |

| kmp_get_random                                                                       | 0.309s     |              | libiomp | kmp_get_r       | kmp_runti                   | 0xb6ea0    |

| INTERNAL2fb12104::kmp_wait_template <kmp_flag_64<(bool)< p=""></kmp_flag_64<(bool)<> | 0.231s     |              | libiomp | bool _INTER     | kmp_wait                    | 0x6f070    |

| sched_yield                                                                          | 0.149s     |              | libc-2  | sched_yield     |                             | 0x10589    |

| INTERNAL4894dd2b::kmp_steal_task                                                     | 0.087s     |              | libiomp | _INTERNAL       | kmp_taski                   | 0xed6d0    |

| ▶ [sep5]                                                                             | 0.039s     |              | sep5    | [sep5]          |                             | 0          |

| Q: + - r r os 5s 10s                                                                 | 15s 20s    | 25s          | 30s     | 355             | Thread                      | ~          |

| OMP Worker Thread #5 (TI                                                             | chronize   | Herrini tete |         | 0               | ✓ I Running ✓ ▲ CPU Tim     | e          |

| kworker/24:1H (TID: 2799)                                                            |            |              |         |                 | Spin and Spin and Clocktick |            |

| GPU Execution Units                                                                  |            |              |         |                 | GPU Engine                  |            |

| GPU Computing Threads Di                                                             |            |              |         |                 | 0:77:0.0                    | ) : Displa |

|                                                                                      |            |              |         |                 | 0:77:0.0                    | Dianta     |

Figure 5. Profile of code with 65% GPU offload

Figure 6 shows the run times for different values of *part*. Keep in mind that a *part* of zero means that no work is offloaded to the GPU. A *part* of one means that all work is offloaded. It's clear that a balanced distribution of work across the CPU and GPU gives better performance than either extreme.

Table 1. Comparing training and prediction performance (all times in seconds)

OpenMP provides true asynchronous, heterogeneous execution on CPU+GPU systems. It's clear from our timing results and VTune profiles that keeping the CPU and GPU busy in the OpenMP parallel region gives the best performance. We encourage you to try this approach.

## ArrayFire Interoperability with oneAPI, Libraries, and OpenCL

Taking Advantage of oneAPI to Avoid Code Rewrites

Stefan Yurkevitch, Software Engineer, ArrayFire

oneAPI greatly simplifies development on heterogeneous accelerators. With a code once, run anywhere approach, the APIs offer a powerful way to develop code. <u>ArrayFire</u> is a GPU library that already offers a vast collection of useful functions for many computational domains. It shares the philosophy oneAPI brings to the software development world. In this article, we'll be exploring how to integrate the oneAPI Deep Neural Network (<u>oneDNN</u>) library and the SYCL-based Data Parallel C++ (DPC++) programming language into existing codebases. Our goal is to allow the programmer to take advantage of oneAPI to avoid the code rewriting often required when migrating to a new programming model.

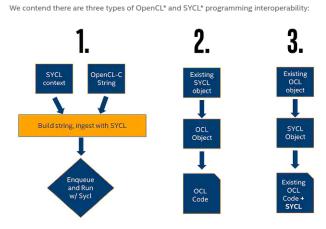

#### Interoperability with SYCL

oneAPI is the combination of DPC++ and libraries to simplify cross-architecture parallel programming. The libraries are tightly integrated with the DPC++ language. They both provide a variety of methods for interoperability with the underlying OpenCL implementation. The base language provides three main methods of interoperability with OpenCL that cover most use-cases (Figure 1). The flow of interoperability functions can be from existing code to SYCL or vice versa, specifically:

- 1. Using existing OpenCL kernels within DPC++ code by creating a kernel object from the kernel string

- 2. Extracting OpenCL objects from existing SYCL objects

- 3. Creating SYCL objects from existing OpenCL objects

#### Interoperability Types

Figure 1. SYCL interoperability with OpenCL

Let's consider how the existing ArrayFire codebase could be integrated with these interoperability options. In the first case, we could directly reuse the raw ArrayFire kernels (Figure 1, left):

```

queue q{gpu selector()};

// Create command queue targeting GPU

program p(q.get context());

// Create program from the same context as q

// Compile OpenCL vecAdd kernel, which is expressed as a C++ Raw String as indicated by R"

p.build with source (R" ( _____ kernel void existingArrayFireVecAdd( __global int *a,

__global int *b,

global int *c)

{

int i = get_global_id(0);

c[i] = a[i] + b[i];

} )");

// buffers here ...

q.submit([&](handler& h) {

// accessors here...

// Set buffers as arguments to the kernel

h.set args(A, B, C);

// Launch vecAdd kernel from the p program object across N elements.

h.parallel for(range<1> (N), p.get kernel("vecAdd"));

});

```

In reality, ArrayFire kernels rely on more complicated data structures than simple buffers so reusing kernels in this manner isn't as trivial as copy-pasting the CL string. We'll need to handle the data exchange using one of the other two methods.

The second method (Figure 1, middle) of extracting OpenCL components from SYCL objects is based on the simple convention of using the .get () method on existing SYCL objects. Each call on a SYCL object will return the corresponding underlying OpenCL object. For example, cl::sycl::queue::get() will return an OpenCL cl command queue.

The third method (Figure 1, right) takes existing OpenCL objects and uses them to create SYCL objects. This can be done using the SYCL object's constructors, such as sycl::queue::queue (cl command queue, ...). In these cases, the constructors will also retain the OpenCL instance to increase the reference count of the OpenCL resource during construction and will release the instance during the destruction of the SYCL object.

#### Interoperability with oneAPI Libraries

Similar interoperability conventions exist within the oneAPI libraries. Some of the libraries, like oneMKL, directly rely on the DPC++ interoperability. Their functions can accept unified shared memory (USM) pointers. Others, like oneDNN, which we will be using in our example, provide similar .get () and constructor() mechanisms.

oneDNN has similar, yet slightly different data structures from DPC++. The sycl::device and sycl::context are combined into a single dnnl::engine object, and the dnnl::stream replaces the sycl:: queue. Despite these differences, the mechanism for OpenCL interoperability remains the same. OpenCL objects can be obtained with getter functions while new oneDNN objects can be created from existing OpenCL objects through their constructors. oneDNN also provides an explicit interoperability header with the same functionality.

oneDNN is flexible in terms of its supported runtime backend. It can use either the OpenCL runtime or the DPC++ runtime for CPU and GPU engines to interact with the hardware. Developers may need to use oneDNN with other code that uses either OpenCL or DPC++. For that purpose, the library provides API extensions to interoperate with the corresponding underlying objects. Depending on the target, the interoperability API is defined in either the dnnl ocl.hpp or dnnl sycl.hpp header. For our usecase, we're interested in supplementing the capabilities of oneDNN's inference engine with the existing preprocessing capabilities offered by the ArrayFire library. For now, this will be done through the OpenCL interoperability functions.

#### ArrayFire and oneDNN: The Details

The motivating example we'll be using to explore the details of OpenCL interop with oneDNN is based on the <u>cnn\_inference\_f32.cpp</u> sample. This example sets up an AlexNet network using oneDNN for inference. Our goal is to use ArrayFire's many OpenCL image processing functions to preprocess the user input images before feeding the data to the existing inference engine. The full workflow involves the following steps:

- Include the relevant interoperability headers

- Create a GPU engine while sharing the cl\_context with ArrayFire

- Create a GPU command queue via the OpenCL interoperability interface

- Perform preprocessing and data preparation with ArrayFire

- Create a GPU memory descriptor/object

- Access GPU memory via OpenCL interoperability interface for input

- Create oneDNN primitives/descriptors/memory to build the network

- Execute the network as usual with oneDNN

- Release GPU memory

The first additions we need to make to the file include the interoperability headers for both ArrayFire and oneDNN. The OpenCL headers are included as well.

```

#include "oneapi/dnnl/dnnl.hpp" // oneDNN header

#include "oneapi/dnnl/dnnl_ocl.hpp" // oneDNN OpenCL interop header

#include <CL/cl.h> // OpenCL header

#include <arrayfire.h> // ArrayFire header

#include <af/opencl.h> // ArrayFire OpenCL interop header

```

Next, we'll grab the OpenCL context and queue from ArrayFire to share with oneDNN:

```

cl_device_id af_device_id = afcl::getDeviceId();

cl_context af_context = afcl::getContext();

cl command queue af queue = afcl::getQueue();

```

The OpenCL objects will be used to create the corresponding oneDNN objects. This will use the interoperability functions defined in the <u>interop header</u>. These functions reside in the additional ocl\_ interop namespace. Remember that this will retain the objects throughout the lifetime of the oneDNN scope:

```

dnnl::engine eng = dnnl::ocl_interop::make_engine(af_device_id, af_context);

dnnl::stream s = dnnl::ocl_interop::make_stream(eng, af_queue);

```

Then we can load and preprocess our images reusing the ArrayFire library's accelerated GPU functions:

oneDNN finally requires the dnnl::memory object. This isn't raw memory, but rather some memory together with additional metadata such as a dnnl::descriptor.oneDNN supports both buffer and USM memory models. Buffering is the default. To construct a oneDNN memory object with interop support, we will use the following interop function:

```

ocl::interop make_memory(

const memory::desc& memory_desc, // descriptor describing memory shape and layout

const engine& aengine, // our interop engine

memory_kind kind, // buffer or USM

void* handle = DNNL_MEMORY_ALLOCATE // handle to underlying storage

)

```

Here, the descriptors follow those of the sample where we expect the input to AlexNet to be a 227 x 227 NCHW image. The engine is just our execution engine that we have been sharing between ArrayFire and oneDNN. The memory kind should specify if we're using the USM or buffer interface. If we chose to pass in a handle pointer, it should then proceed to match the type of memory we pass in. If the handle is a USM pointer or an OpenCL buffer, the oneDNN library doesn't own the buffer and the user is responsible for managing the memory. With the special DNNL\_MEMORY\_ALLOCATE value, the library will allocate a new buffer on the user's behalf.

oneDNN supports both buffer and USM memory models, so replacing the engines and queues with objects shared with ArrayFire will result in incompatible memory creation modes. During the creation of the dnnl::memory object, the following error can occur:

```

oneDNN error caught:

Status: invalid_arguments

Message: could not create a memory object

```

Instead of the default method of dnnl::memory creation, the interoperability functions must be used instead, as follows:

This applies all instances of default dnnl::memory allocation. The interoperability functions to specify the ocl interop::memory kind::buffer must be used:

ocl\_interop::make\_memory(descriptor, engine, ocl\_interop::memory\_kind::buffer);

Finally, after all weights are loaded, the inference primitives can be created and called as usual. After the network has run, we should free the resources that we are responsible for:

```

// additional alexnet network setup

// loading of weights following cnn_inference_f32.cpp

...

// execute all primitive steps for full inference using our inputs

for (size_t i = 0; i < net.size(); ++i) {

net.at(i).execute(s, net_args.at(i));

}

s.wait(); // wait until stream finishes writing to memory

images.unlock(); // return memory ownership to arrayfire to free resources

```

We want to make sure we're running oneDNN with the OpenCL runtime rather than the DPC++ runtime. This can be achieved by specifying the SYCL\_DEVICE\_FILTER=opencl environment variable. A modified, working cnn\_inference\_f32.cpp for reference can be found in this gist.

#### Conclusion

oneAPI provides all the tools required to integrate existing OpenCL codebases with the new heterogeneous programming approach. The underlying OpenCL objects can be shared in either direction with DPC++. oneAPI's libraries have their own methods to handle the interoperability tasks. With minor code changes, whole OpenCL libraries can be reused rather than rewritten. oneAPI saves future development time by avoiding redevelopment efforts of already useful code.

## Break Free of Code Boundaries

Experience the power of cross-architecture programming in the Intel <sup>®</sup> DevCloud for oneAPI.

#### Demo

Run our Mandelbrot demo on different architectures to see cross-architecture performance for yourself.

#### Learn

Get hands-on experience with Data Parallel C++ with 25 Jupyter notebooks loaded with code samples.

### Develop

Plan and test future-ready applications on the latest Intel CPUs, GPUs, and FPGAs.

### GET STARTED NOW >

For more complete information about compiler optimizations, see our Optimization Notice at software.intel.com/articles/optimization-notice#opt-en. Intel and the Intel logo are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. © Intel Corporation

## Using the oneAPI Level Zero Interface

A Brief Introduction to the Level Zero API

Rama Kishan Malladi, Solution Architect, Amazon Web Services Nitya Hariharan, Application Engineer, Intel Corporation

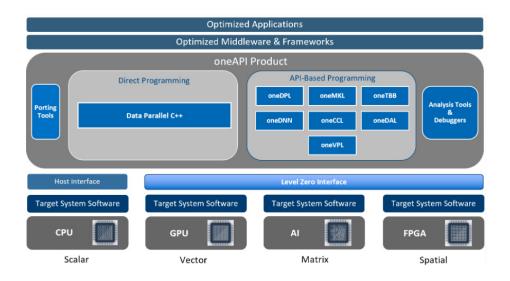

The <u>oneAPI specification</u> simplifies software development by providing the same language, API, and programming model across accelerator architectures. It defines a set of APIs for common data parallel domains, across a variety of architectures. Both the API and the direct programming approaches are based on data parallelism (i.e., the same computation is performed on each data element). The oneAPI<sup>™</sup> platform consists of a host and a collection of accelerator devices (Figure 1). The API programming model is implemented using oneMKL, oneDPL, oneDNN, oneCCL, and other libraries. Direct programming is done using DPC++.

### Figure 1. The oneAPI platform execution model. Note that the Intel<sup>®</sup> implementation of the oneAPI specification also contains programming tools.

#### Level Zero: Introduction

The oneAPI Level Zero provides a low-level, direct-to-metal interface for the devices in a oneAPI platform. Level Zero provides support for broad language features in addition to fine-grained explicit controls/APIs for device discovery, memory allocation, inter-process communication, kernel submission, synchronization, and metrics reporting. It has an API that exposes both the logical and physical abstractions of the underlying devices. While heavily influenced by other low-level APIs (i.e., OpenCL™), Level Zero is designed to evolve independently. It has support for GPUs and other compute devices, such as FPGAs. Most applications should not require the additional control provided by the Level Zero API. It is intended for the explicit controls needed by higher-level runtime APIs and libraries:

- Device discovery and partitioning

- Kernel execution and scheduling

- Peer-to-peer communication

- Metrics discovery and profiling

- Kernel profiling, instrumentation

- System management, query power, performance

The Level Zero C APIs are provided to applications by a shared import library. So, C/C++ applications must include "ze\_api.h" and link with "ze\_api.lib" (or a shared library).

#### Level Zero: APIs

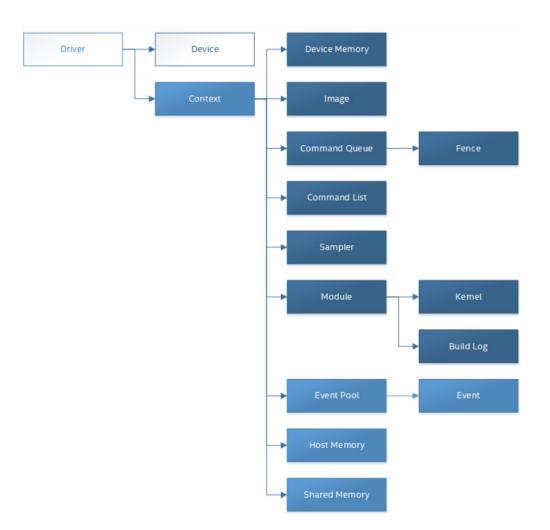

Level Zero APIs are categorized into Core, Tools, and System Programming, but we will only discuss the Core Programming APIs (Figure 2) in this article. It has support for devices, drivers, contexts, memory, command queues/lists, synchronization, barriers, modules, and kernels. Tables 1 and 2 list the most commonly used APIs. Figure 3 shows the execution flow using Level Zero.

Figure 2. Components of the Core Programming APIs

| APIs for Device, Context, Queue    | Short description                         |  |  |  |  |

|------------------------------------|-------------------------------------------|--|--|--|--|

| zeInit, zeDriverGet                | Initialize and discover all the drivers.  |  |  |  |  |

| zeDeviceGet, zeDeviceGetProperties | Find a driver instance with a DEVICE_TYPE |  |  |  |  |

| zeContextCreate                    | Create a context                          |  |  |  |  |

| zeMemAllocHost, zeMemAllocDevice,  | Allocate memory on Host, Device or shared |  |  |  |  |

| zeMemAllocShared                   |                                           |  |  |  |  |

| zeCommandQueueCreate               | Create a command queue                    |  |  |  |  |

| zeCommandListCreate                | Create a command list                     |  |  |  |  |

| zeCommandQueueExecuteCommandLists  | Execute command list in command queue     |  |  |  |  |

| zeCommandQueueSynchronize          | Synchronize host and device               |  |  |  |  |

#### Table 1. Level Zero APIs for Device, Context, and Queue

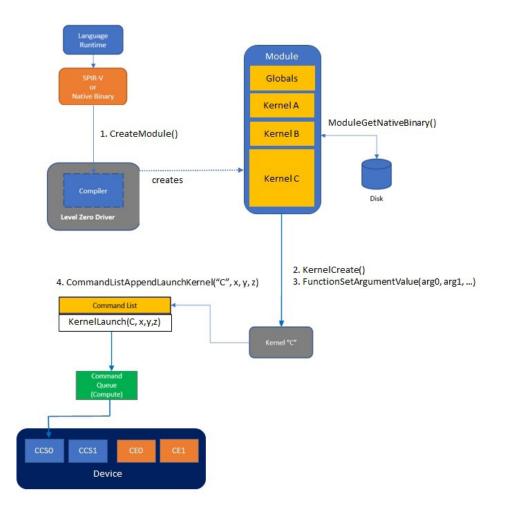

Figure 3. High-level flow: command lists, queues, module, and kernel execution on a device

| APIs for Synchronization, Modules, and Kernels | Short description                                |

|------------------------------------------------|--------------------------------------------------|

| zeEventPoolCreate                              | Create event pool                                |

| zeCommandListAppendLaunchKernel                | Appends the kernel, its arguments, signals to a  |

|                                                | command list.                                    |

| zeEventHostSynchronize                         | Wait on event to complete                        |

| zeModuleCreate                                 | Creates a module by compiling IL code or load of |

|                                                | a native binary                                  |

| zeKernelCreate                                 | Reference a kernel within a module               |

| zeKernelSetArgumentValue                       | Setup arguments for kernel launch                |

#### Table 2. Level Zero APIs for synchronization and kernel-related functions

Listing 1 shows the main program that has driver and device discovery. Listing 2 shows kernel execution in function RunTest.

```

// Driver code (main)

int main(int argc, char *argv[])

{

zeInit(ZE INIT FLAG GPU ONLY);

ze driver handle t driverHandle;

zeDriverGet(&driverCount, &driverHandle);

uint32 t deviceCount = 1;

ze device handle t device;

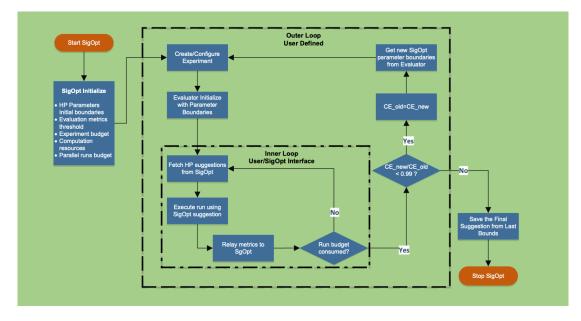

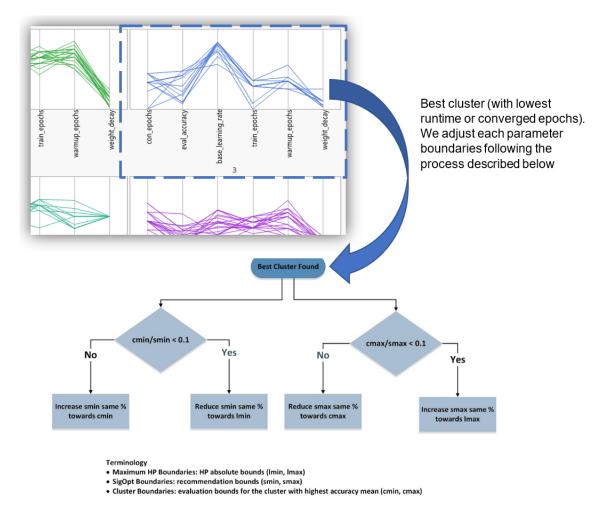

zeDeviceGet(driverHandle, &deviceCount, &device);