#### AIPC Landscape

## Al Client Workload Trends

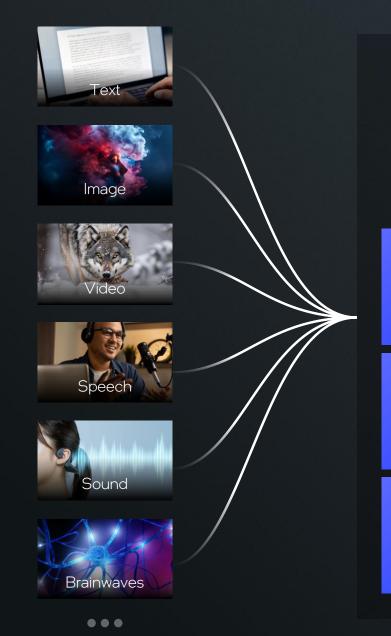

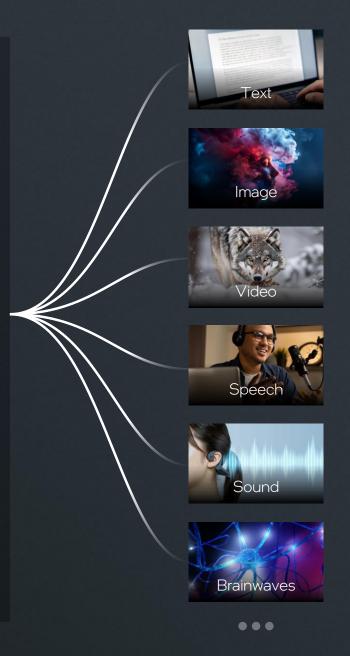

#### Growing in diversity

From background blurring to gen Al

#### App & OS integration

from features in apps to OS co-pilots

#### **Multi Modal**

Transformers and diffusion

#### AIPC Trends

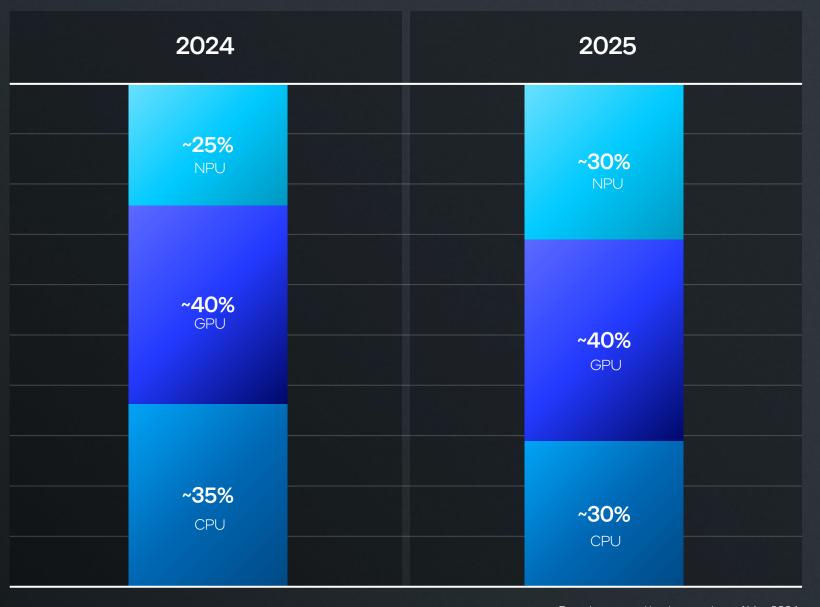

## Al Engine Adoption

Multi-engine adoption

Macro ISV trend

GPU role significant

In ISV feature plans through '25

Multiple performant engines

Are best fit for enabling ISV efforts

Based on internal Intel research as of May 2024.

## Unmatched Al Compute

With our Multi-Engine approach

Up to

120

platform TOPS

#### **GPU**

Creator & gamer Al

#### **NPU**

Al assistants & gen Al

#### **CPU**

Light "embedded" Al

Lunar Lake

## GPU Al Engine

Xe2

GPU architecture

XMX

X<sup>e</sup> Matrix Extensions 67

peak TOPs

All tops are Int8 on high end SKU, will vary based on SKU

Lunar Lake

## CPU Al Engine

P-core & E-core

CPU architecture

VNNI & AVX

Al instructions

5

peak TOPs

All tops are Int8 on high end SKU, will vary based on SKU

TECH . tour. TW

## Lunar Lake NPU Deepdive

Darren Crews

Sr Principal Engineer, NPU Lead Architect

Lunar Lake

## NPU Al Engine

NPU4 2x

Architecture

Power efficiency 48

Peak TOPs

All tops are Int8 on high end SKU, will vary based on SKU

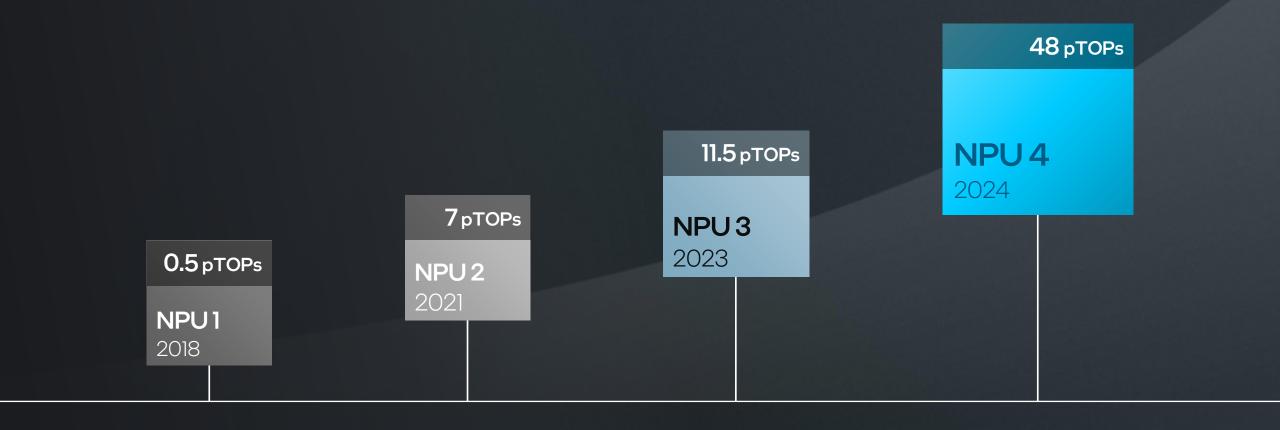

## Continuous NPU Improvements

Across 4 generations of IP

**NPU 4** 2024

#### **Proven foundations**

based on three prior generations

#### Higher compute capacity

to support growing number of use cases

#### Increased efficiency

to support longer battery life

## Scaling the NPU

Increase number of engines

Increase frequency

Improve architecture

NPU4

NPU3

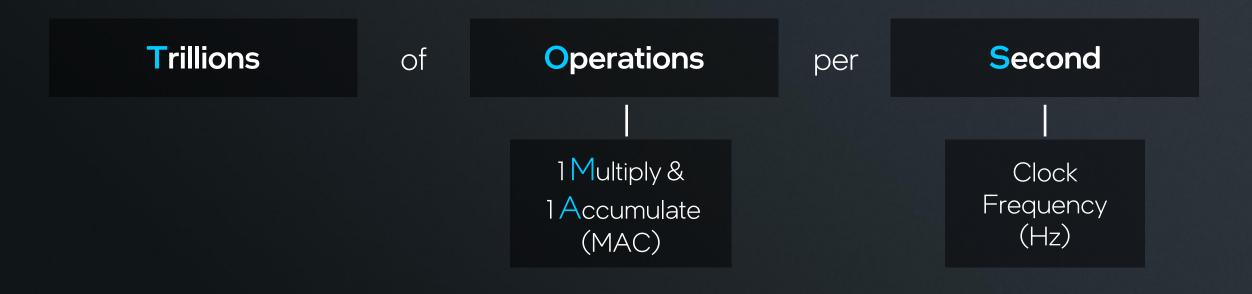

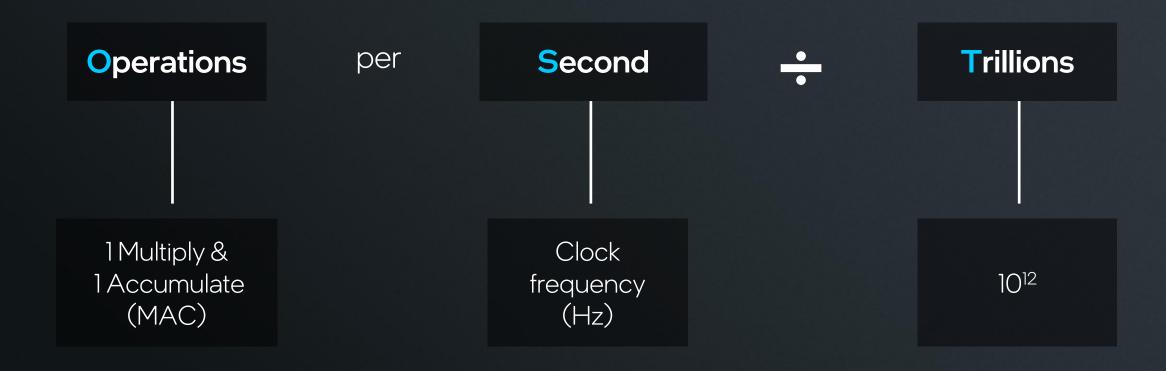

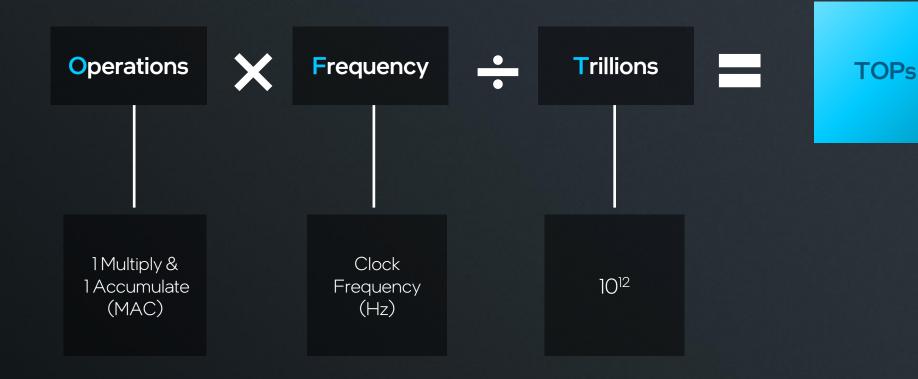

## What is a TOP?

## How Many Al TOPS?

## How Many Al TOPS?

# How Many Al TOPS in Meteor Lake's NPU?

# How Many Al TOPS in Meteor Lake's NPU?

#### Operation Types Overview Scalar Vector Matrix Complexity Ν $N^2$ Conditional SoftMax Convolution Example functions Looping Activation functions Matrix multiplication Occurrence in Al Very high Very high Low

#### Operation Types Overview Scalar Vector Matrix Complexity $N^2$ Ν Conditional SoftMax Convolution Example functions Looping Activation functions Occurrence in Al Very high Very high Low

**TOPs**

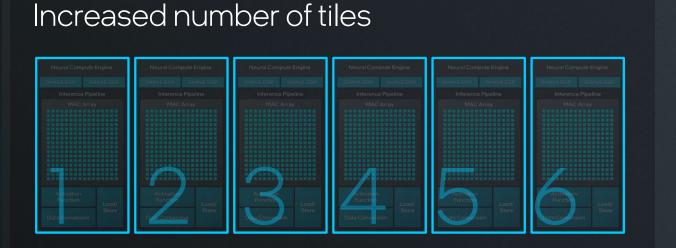

## Scaling the NPU

Increase number of engines

Increase frequency

Improve architecture

NPU4

NPU3

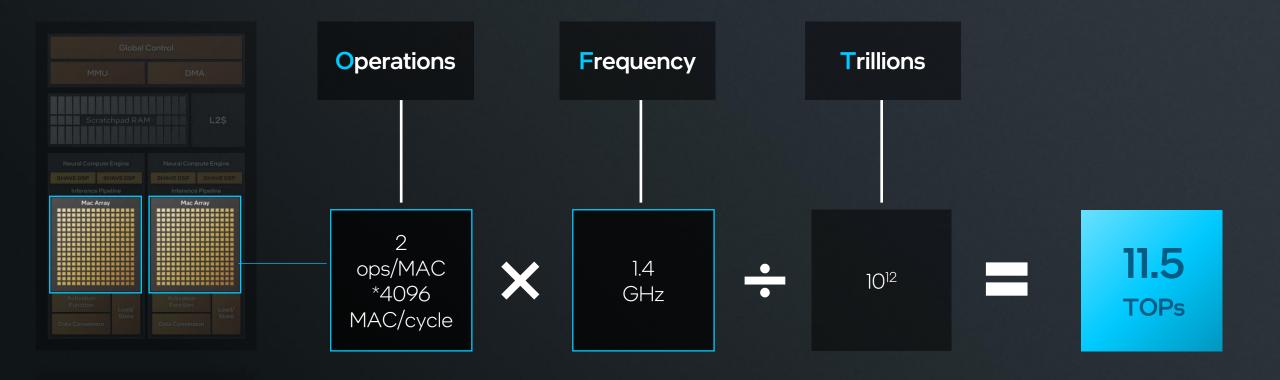

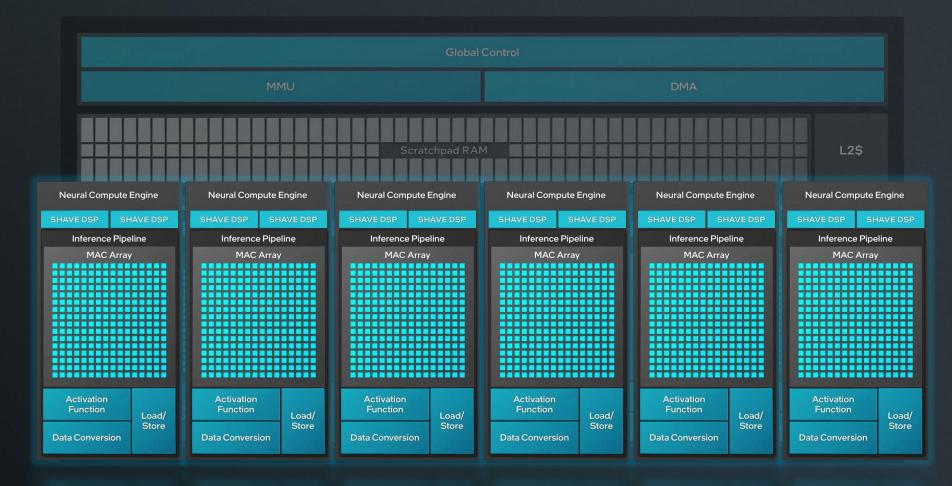

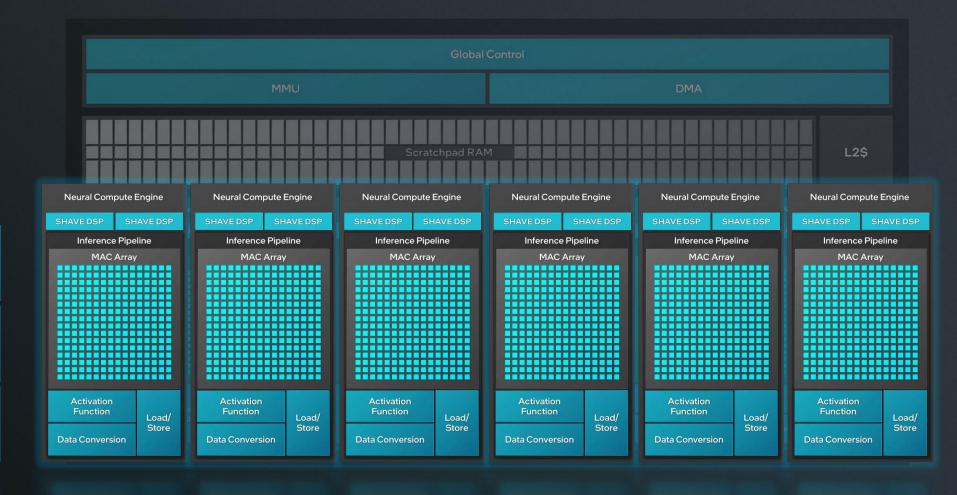

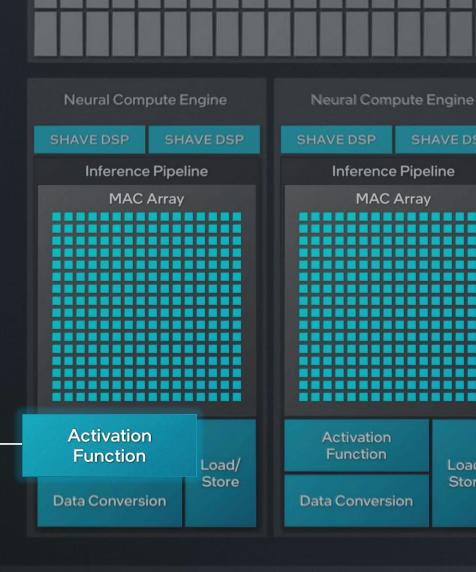

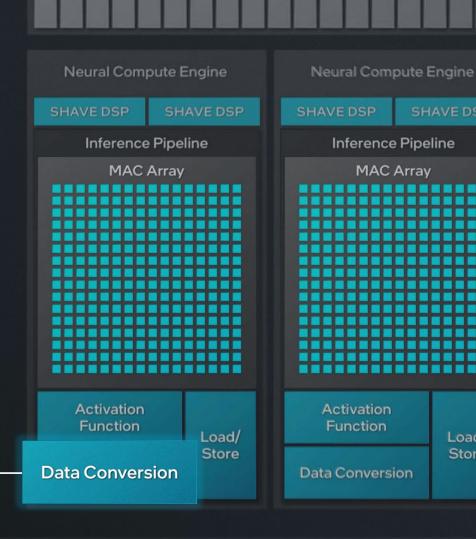

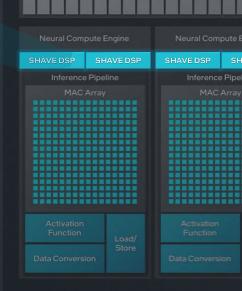

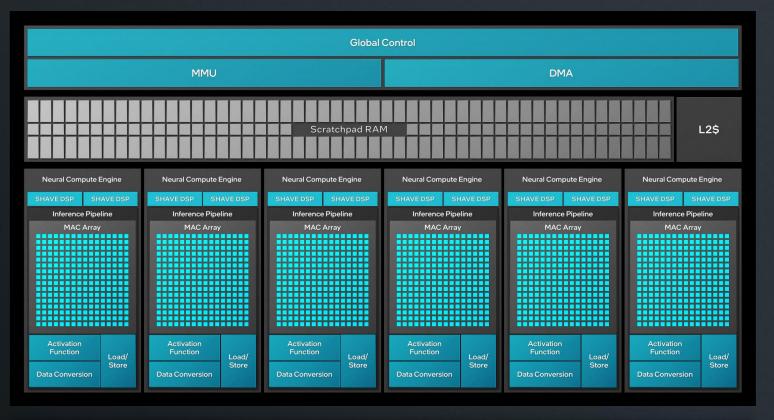

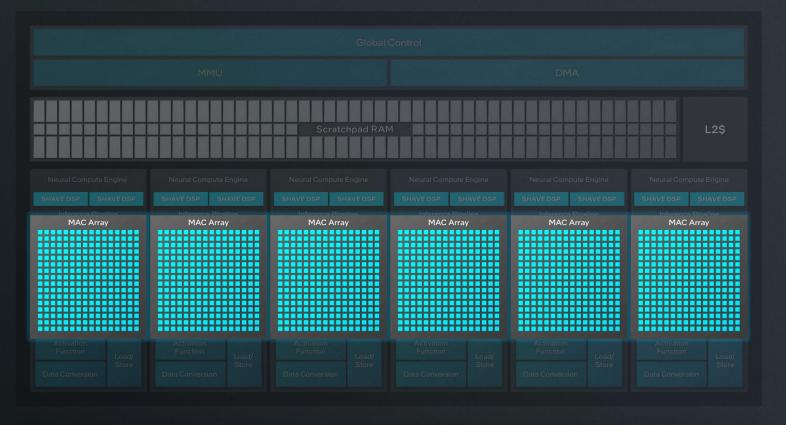

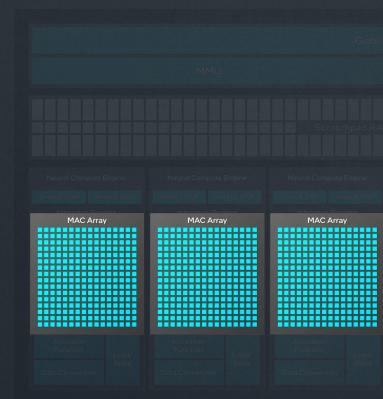

4K MACs 2 NCEs

NPU 4

12K MACs

6 NCEs

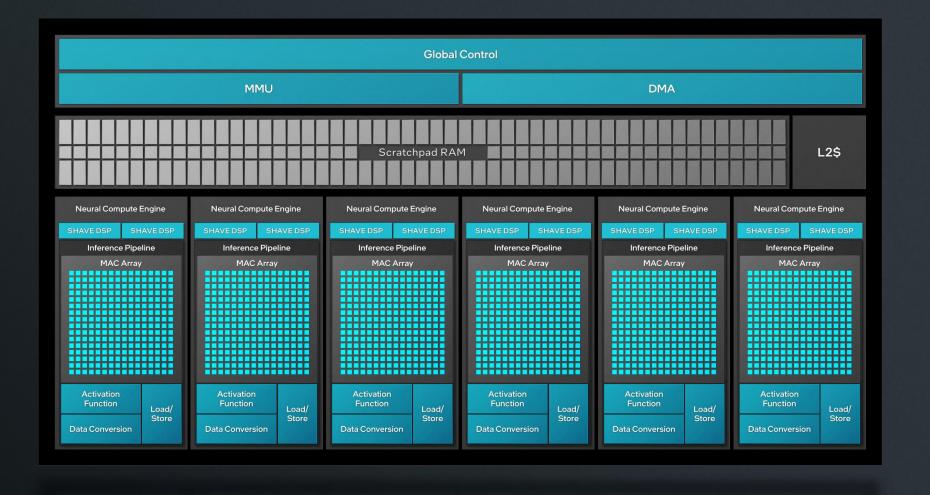

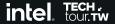

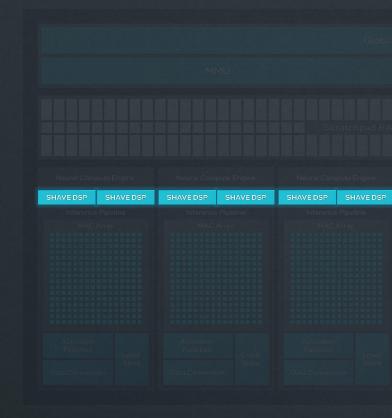

Global Control MMU DMA L2\$ Scratchpad RAM Neural Compute Engine Neural Compute Engine SHAVE DSP SHAVE DSP SHAVE DSP SHAVE DSP Inference Pipeline Inference Pipeline Mac Array Mac Array Mac Array Mac Array Load/

## Scaling the NPU

Increase number of engines

Increase frequency

Improve architecture

NPU4

NPU3

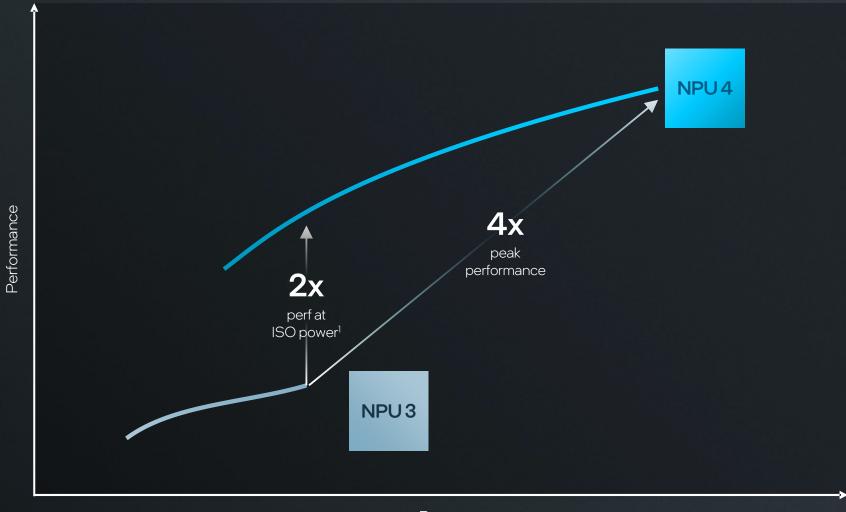

# Increased Efficiency & Increased Performance

Increased clock

New node

Architecture improvements

Power

## Scaling the NPU

Increase number of engines

Increase frequency

Improve architecture

NPU4

NPU3

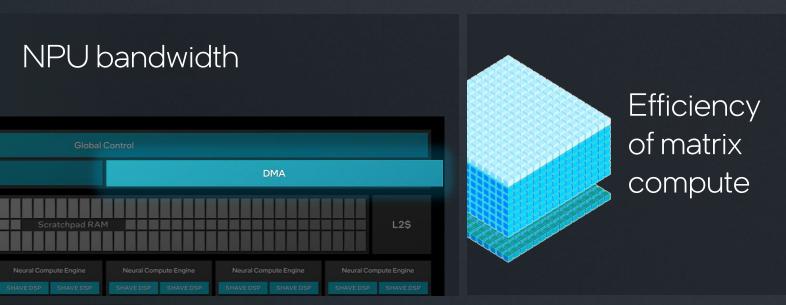

# NPU4 Architecture improvements

Architecture

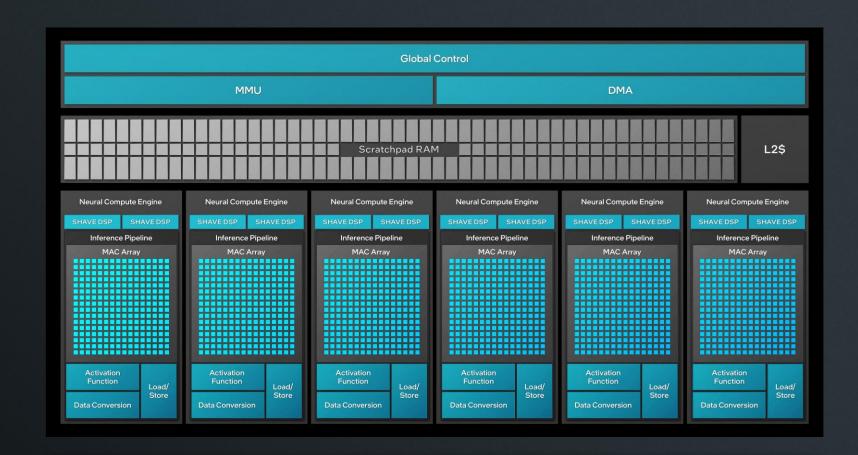

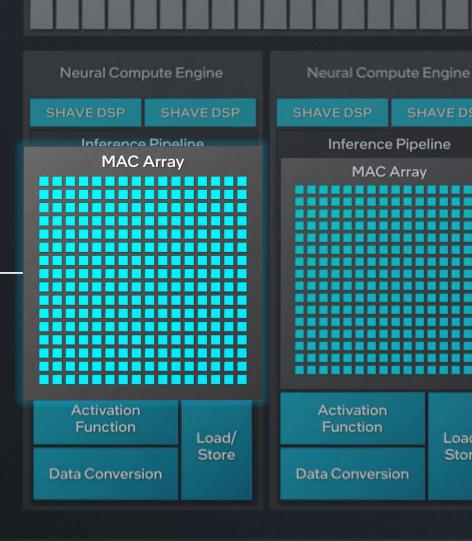

## NPU4 Architecture

## overview

Global control & MMU

## NPU4 Architecture

Architecture overview

Global control & MMU

DMA & scratchpad RAM

Architecture

Global control & MMU

DMA & scratchpad RAM

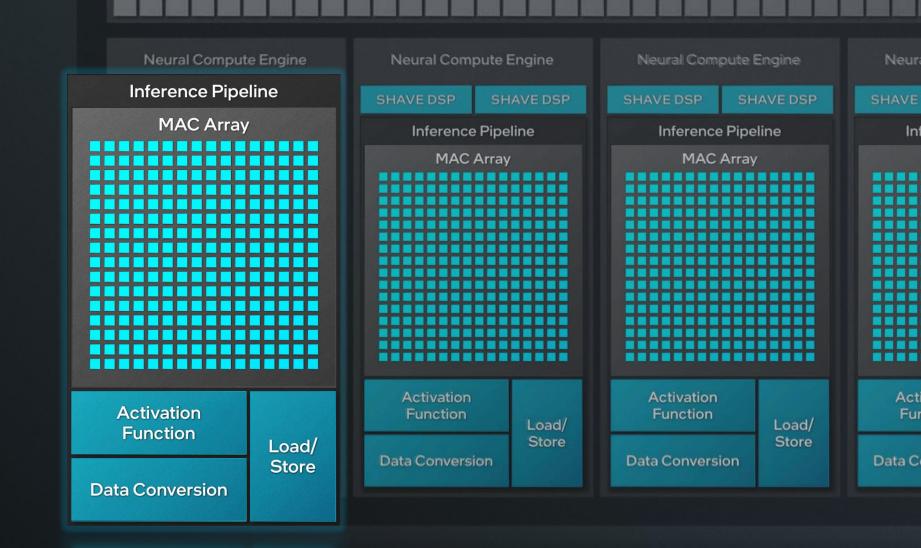

Neural compute engines

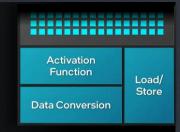

Neural compute engine

Specialized engines

Matrix + Vector

Inference pipeline

MAC arrays + fixed function

Programmable DSPs

Inference pipeline

Efficient matrix multiplication

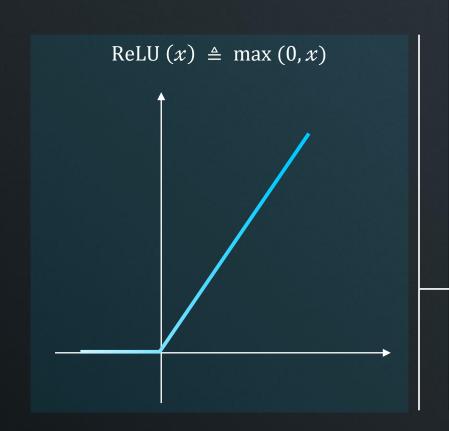

Activation function support

Data conversion and re-layout support

Scratchpad RAM

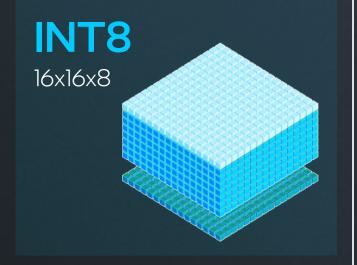

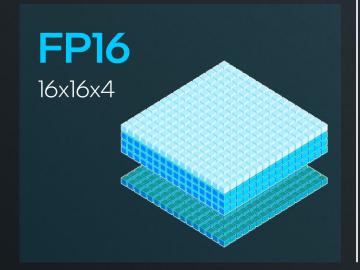

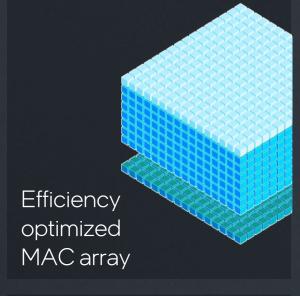

## NPU4 MAC array

Matrix multiplication & convolution

2048 MAC/cycle int8 1024 MAC/cycle FP16

Up to 2x<sup>1</sup> efficiency driving better perf/watt

Activation functions

Multiple functions

Supported

**FP** precision

Support

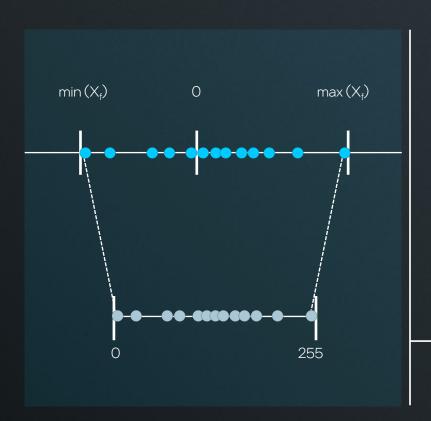

#### Data conversion

**Datatype conversion**

**Fused operations**

Output data re-layout

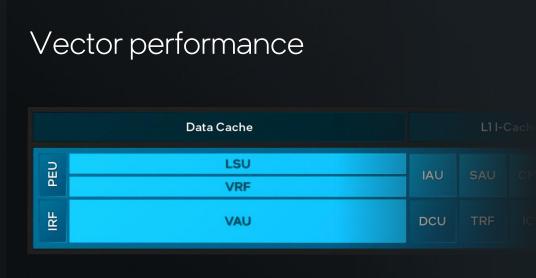

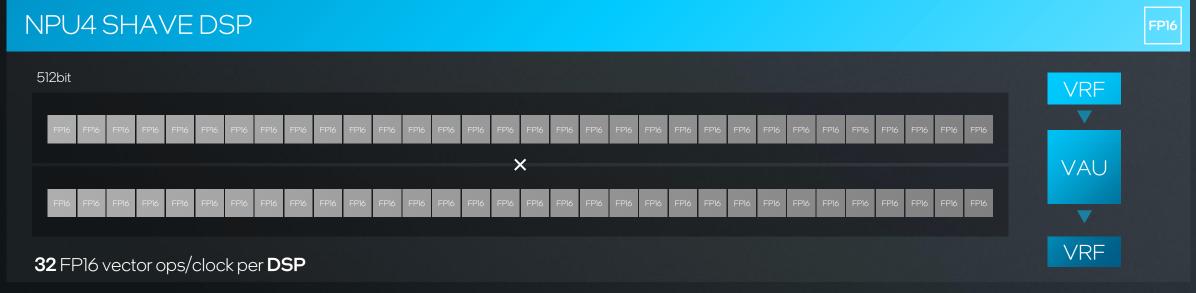

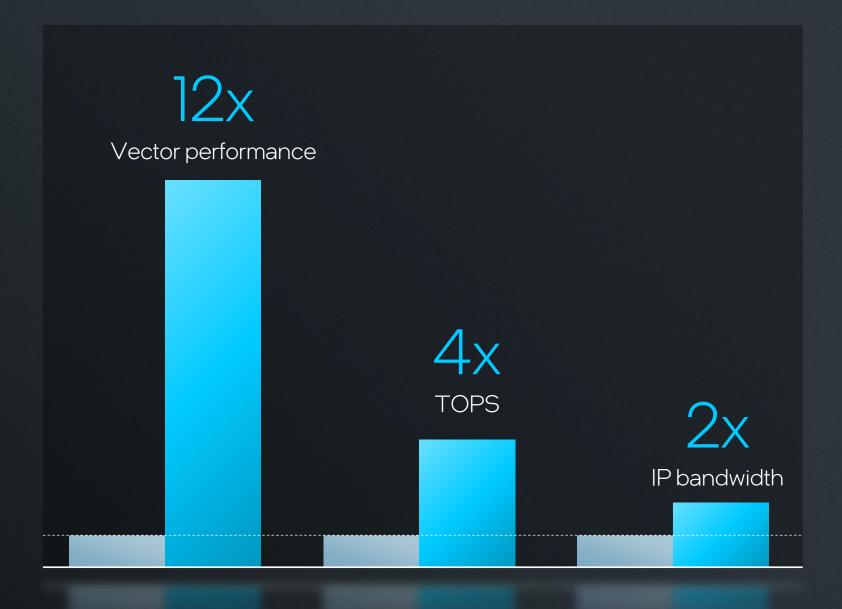

## NPU 4 SHAVE DSP

### Upgraded SHAVE DSP

4x vector compute

### 12x overall vector perf

improves transformer /LLM performance

**512-bit**Vector register file size

4x

Performance

Vector unit

4x

Bandwidth

to and from

SHAVE DSP

## SHAVE DSP Vector increase

## NPU4 DMA engine

#### DMA Scratchpad RAM L2S Inference Pipeline Inference Pipeline Inference Pipeline Inference Pipeline Inference Pipeline Inference Pipeline ---------------------------------

#### 2x DMA bandwidth

improves network performance especially LLMs

#### **New functions**

Embedding tokenization

## intel<sub>®</sub> NPU4

Performance

Intel - NPU 4

Intel - NPU 3

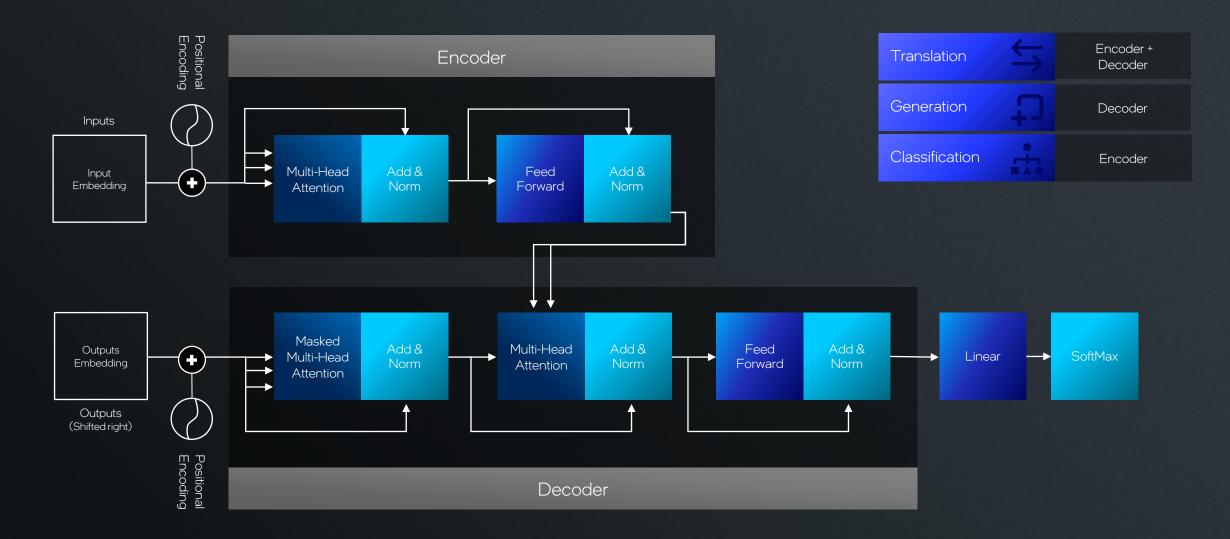

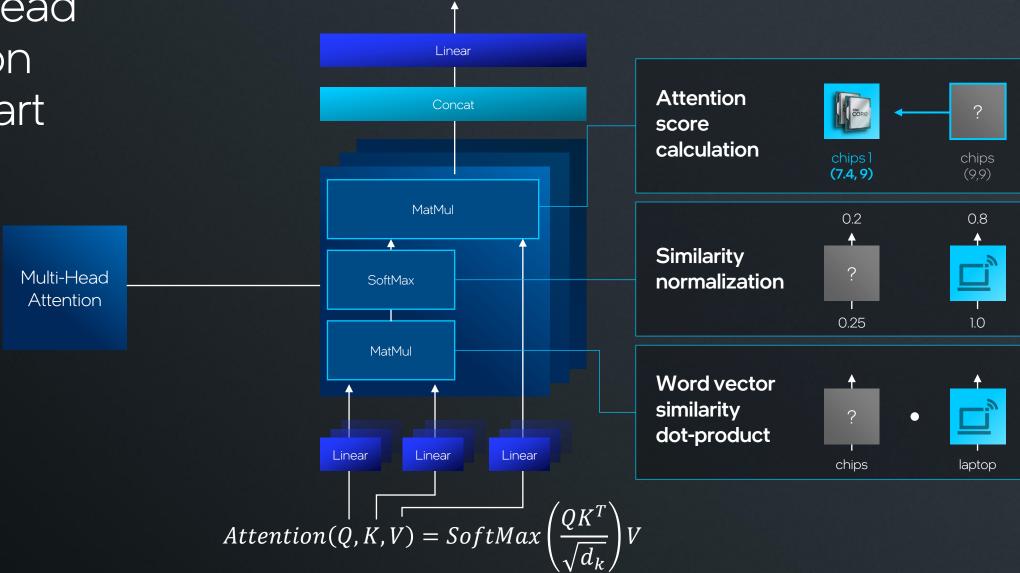

## Transformer Use Cases

Translation

Generation

Classification

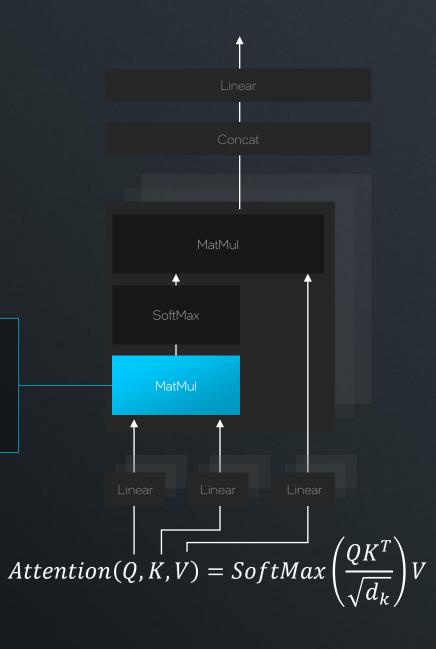

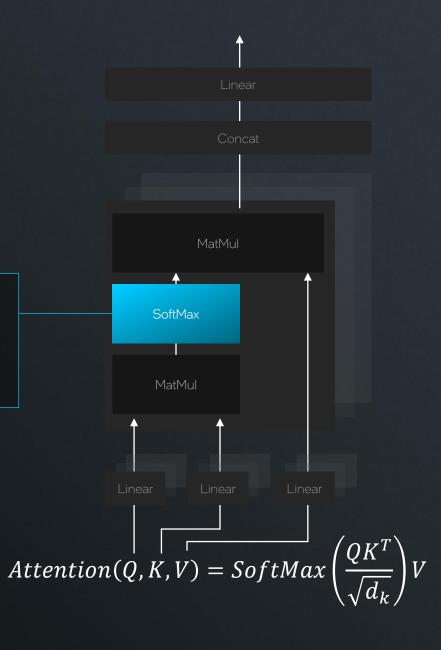

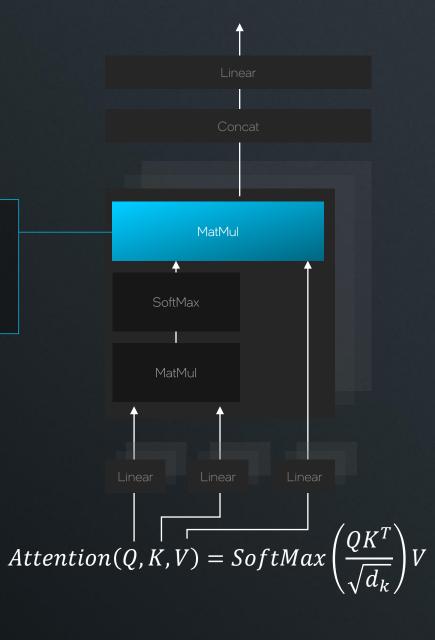

## Transformer Model Architecture

### Transformer Architecture on Intel's NPU

## Transformer Architecture on Intel's NPU

### Transformer Architecture on Intel's NPU

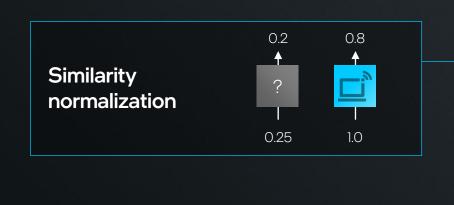

Word vector similarity dot-product

Attention score calculation

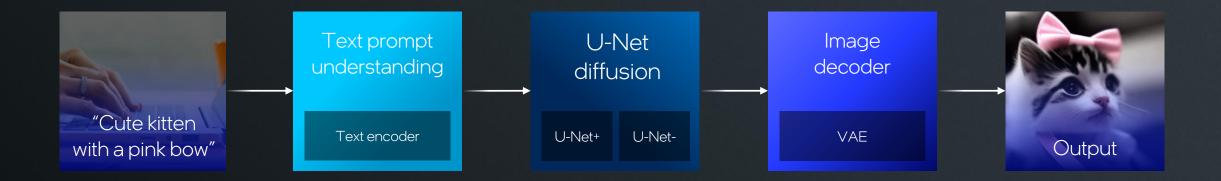

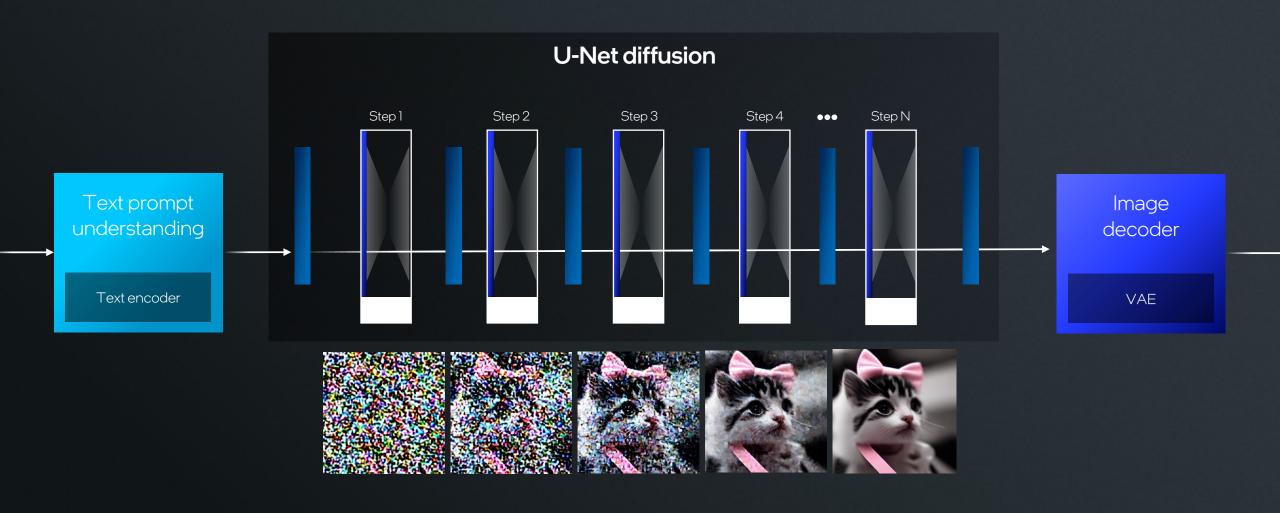

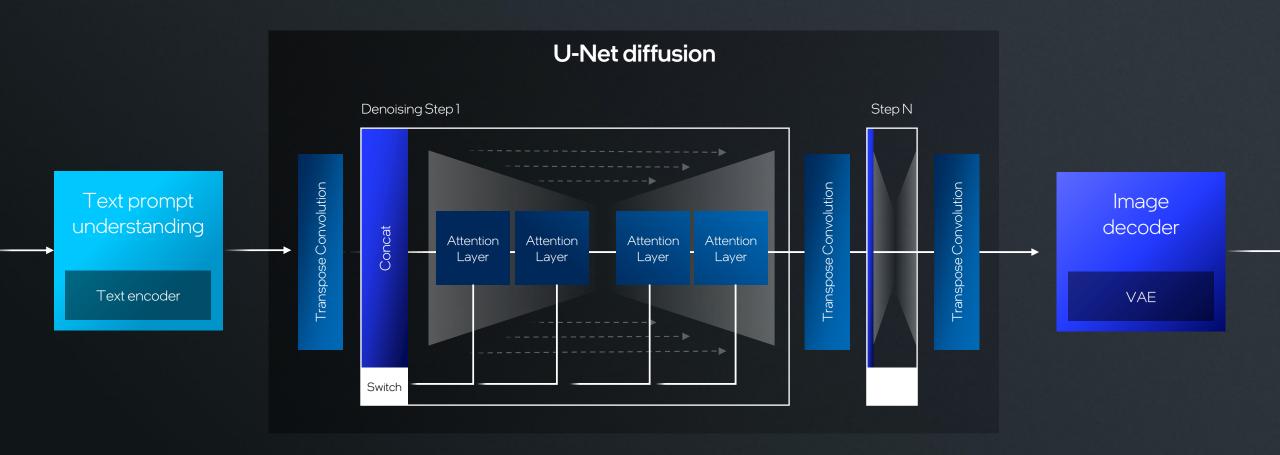

#### Stable Diffusion Architecture

#### Stable Diffusion Architecture

#### Stable Diffusion Architecture

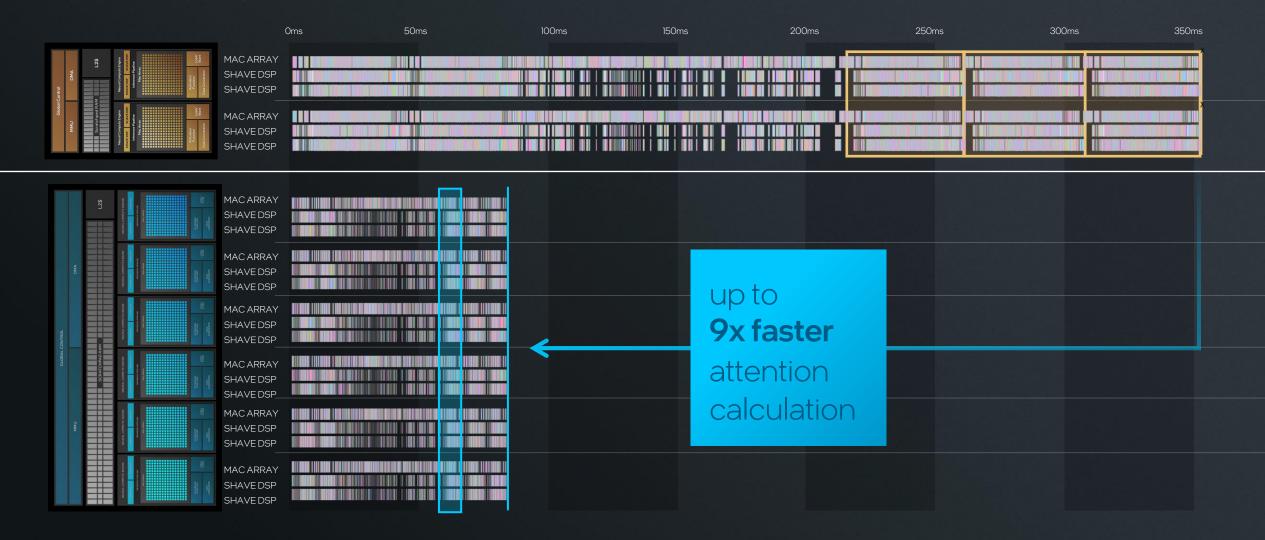

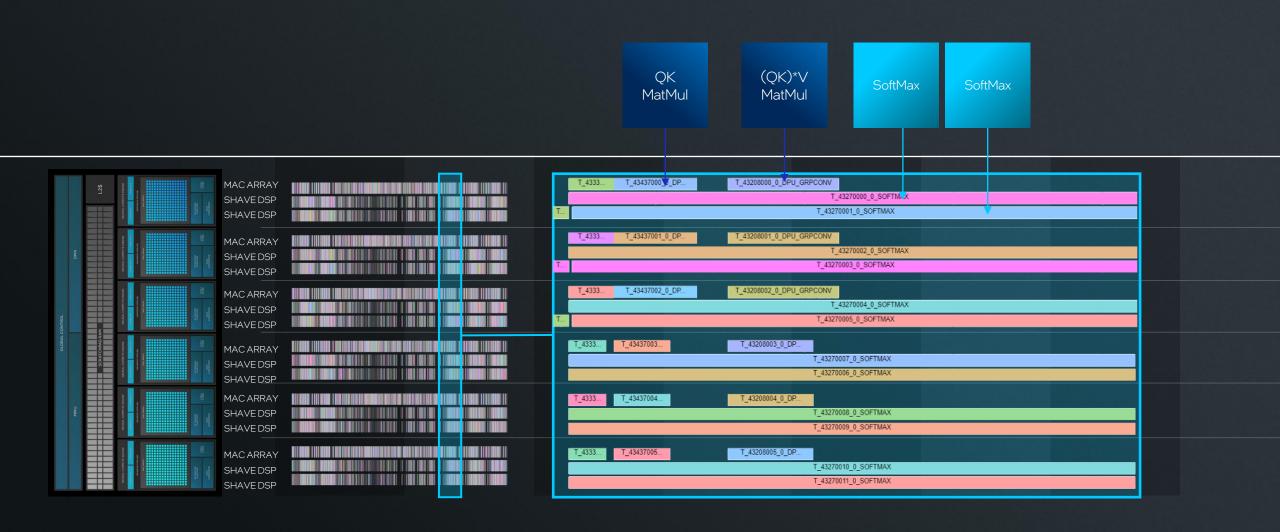

### Accelerating Multi-Head Attention

Performance on U-Net

### Accelerating Multi-Head Attention

Performance on U-Net

#### Stable Diffusion

#### Demo

|                                  | Text prompt understanding | U-Net<br>diffusion | lmage<br>decoder |        |

|----------------------------------|---------------------------|--------------------|------------------|--------|

| "Cute kitten<br>with a pink bow" | Text encoder              | U-Net+ U-Net-      | VAE              | Output |

| Meteor Lake                      | CPU                       | NPU                | GPU              |        |

| Lunar Lake                       | NPU                       | NPU                | GPU              |        |

| Data Type                        | FP16                      | INT8               | FP16             |        |

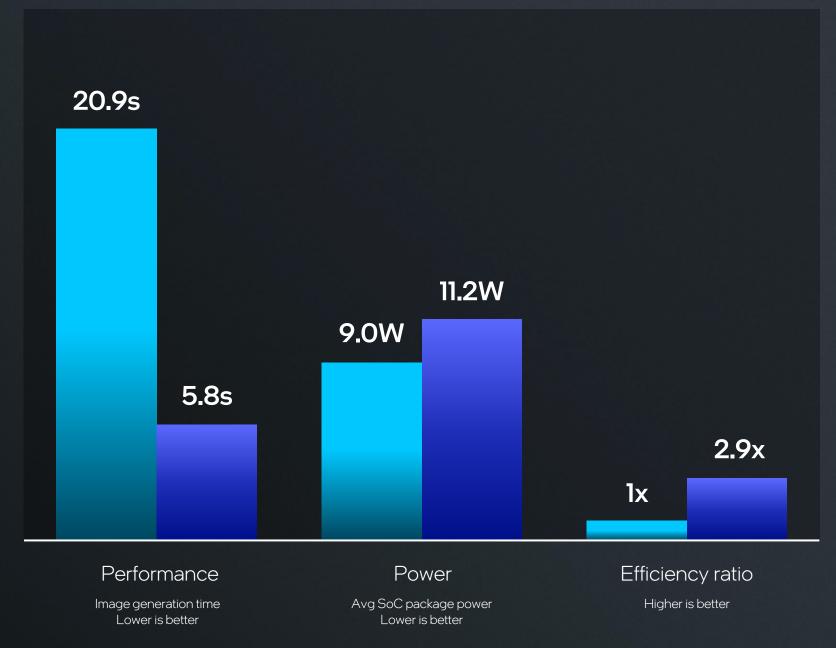

## Stable Diffusion v1.5 20 Iterations

#### 42 Inferences

Text Encoder (1)

- + U-Net+ (20)

- + U-Net-(20)

- +VAE Decoder(1)

- Meteor Lake

- Lunar Lake

## Next Gen NPU 4

Largest integrated and dedicated Al accelerator for the AIPC

2 Enhanced SHAVE DSPs

Accelerating LLM & transformer operations

Native activation function & data conversion support

TOPS

DMA

Embedding tokenization used for LLMs

6 Neural compute engines

TECH: tour.TW

## Thank You

#### Notices & Disclaimers

The preceding presentation contains product features that are currently under development. Information shown through the presentation is based on current expectations and subject to change without notice.

Results that are based on pre-production systems and components as well as results that have been estimated or simulated using an Intel Reference Platform (an internal example new system), internal Intel analysis or architecture simulation or modeling are provided to you for informational purposes only. Results may vary based on future changes to any systems, components, specifications or configurations.

Performance varies by use, configuration and other factors. Learn more at www.intel.com/PerformanceIndex.

Al features may require software purchase, subscription or enablement by a software or platform provider, or may have specific configuration or compatibility requirements. Details at www.intel.com/AIPC.

No product or component can be absolutely secure. Intel technologies may require enabled hardware, software or service activation.

All product plans and roadmaps are subject to change without notice.

Performance hybrid architecture combines two core microarchitectures, Performance-cores (P-cores) and Efficient-cores (E-cores), on a single processor die first introduced on 12th Gen Intel® Core ™ processors do not have performance hybrid architecture, only P-cores or E-cores, and may have the same cache size. See ark.intel.com for SKU details, including cache size and core frequency.

Built-in Intel® Arc™ GPU only available on select Intel® Core™ Ultra processor-powered systems; OEM enablement required.

Some images may have been altered or simulated and are for illustrative purposes only.

Intel does not control or audit third-party data. You should consult other sources to evaluate accuracy.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

#### APPENDIX

| Claim # & Statement                                                      | Slide # & Title/Details                                                                                                                                                                                                                                                                              |  |  |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                                                                        | SLIDE 22: Increased Efficiency & Increased Performance                                                                                                                                                                                                                                               |  |  |

| 2x performance at ISO power vs.<br>Meteor Lake                           | Testing by Intel as of January 2024. Based on VPU-EM simulation. Power data is generated from the simulation tool based on power data that has been extracted from circuit simulation tools. This simulation, which is a ~100% utilization int8 network, is expected to correlate well with silicon. |  |  |

| 4x peak performance                                                      | 4x peak performance is based on TOPS increase from MTL (11 TOPS) to LNL (48 TOPS).                                                                                                                                                                                                                   |  |  |

|                                                                          | SLIDE 34: NPU4 Shave DSP                                                                                                                                                                                                                                                                             |  |  |

| 4x Vector compute                                                        | Based on 4x vector width increase vs. NPU3 . NPU3 has 8 FP16 Vector ops/clock, NPU4 has 32                                                                                                                                                                                                           |  |  |

| 12x overall vector performance                                           | Vector performance = 3x tiles and 4x the vector width (vs. NPU3 )                                                                                                                                                                                                                                    |  |  |

|                                                                          | SLIDE 38: NPU 4 Performance                                                                                                                                                                                                                                                                          |  |  |

| 12x vector performance                                                   | Vector performance = 3x tiles and 4x the vector width (vs. NPU3 )                                                                                                                                                                                                                                    |  |  |

| 4x TOPS                                                                  | TOPS calculation is # of tiles * fmax frequency * ops clock<br>Meteor Lake is up to 11.5 TOPS, Lunar Lake is up to 48 TOPS;<br>Meteor Lake TOPS = (2 tiles * 1.4GHz * 4096 ops/clock)/1000<br>Lunar Lake TOPS = (6 tiles * 1.95GHz * 4096 ops/clock)/1000                                            |  |  |

| 2x IP bandwidth                                                          | IP Bandwidth: Meteor Lake is 64GB/s; Lunar Lake is 136 GB/s.                                                                                                                                                                                                                                         |  |  |

|                                                                          | SLIDE 55: Stable Diffusion v1.5                                                                                                                                                                                                                                                                      |  |  |

| Lunar Lake vs. Meteor Lake<br>performance, power and<br>efficiency ratio | Testing by Intel as of May 2024. Data based on Lunar Lake reference validation platform vs. Intel® Core™ Ultra 7 155H 32GB LPDDR5-6400Mhz (Meteor Lake). Calculated using open source GIMP with NPU plug in. Text Encoder, & Unet +/- are running on the NPU. VAE is running on the built-in GPU.    |  |  |

#