# 5<sup>th</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor XCC (Codename Emerald Rapids) Uncore Performance

**Monitoring Guide**

August 2024

**Revision 001**

Reference Number: 817509

## Notice: This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

Intel technologies may require enabled hardware, software or service activation.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Performance results are based on testing as of dates shown in configurations and may not reflect all publicly available updates. See backup for configuration details. No product or component can be absolutely secure.

Performance varies by use, configuration, and other factors. Learn more on the Performance Index site.

Your costs and results may vary.

2

"Conflict-free" refers to products, suppliers, supply chains, smelters, and refiners that, based on our due diligence, do not contain or source tantalum, tin, tungsten or gold (referred to as "conflict minerals" by the U.S. Securities and Exchange Commission) that directly or indirectly finance or benefit armed groups in the Democratic Republic of the Congo or adjoining countries.

All product plans and roadmaps are subject to change without notice.

Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not "commercial" names and not intended to function as trademarks.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Results have been estimated or simulated.

Intel does not control or audit third-party data. You should consult other sources to evaluate accuracy.

Intel contributes to the development of benchmarks by participating in, sponsoring, and/or contributing technical support to various benchmarking groups, including the BenchmarkXPRT Development Community administered by Principled Technologies.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visiting the Intel Resource and Document Center.

© 2024 Intel Corporation. Intel, the Intel logo, Xeon, the Xeon logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

# **Contents**

| 1 | Intro | oduction                                                                                  | 8   |

|---|-------|-------------------------------------------------------------------------------------------|-----|

|   | 1.1   | Introduction                                                                              | 8   |

|   | 1.2   | Section References                                                                        | 10  |

|   | 1.3   | Uncore PMON Overview                                                                      | 10  |

|   |       | 1.3.1 A Simple Hierarchy                                                                  | 10  |

|   |       | 1.3.2 Global PMON State                                                                   |     |

|   | 1.4   | Unit Level PMON State                                                                     |     |

|   | 1.5   | Uncore PMON - Typical Counter Control Logic                                               |     |

|   | 1.6   | Uncore PMON - Typical Counter Logic                                                       |     |

|   | 1.7   | 5 <sup>th</sup> Gen Intel <sup>®</sup> Xeon <sup>®</sup> Scalable Processor's Uncore PMON | 18  |

|   |       | 1.7.1 Querying Number of CHAs                                                             | 19  |

|   |       | 1.7.2 Querying Number of Intel® UPI Links                                                 |     |

|   | 1.8   | Addressing Uncore PMON State                                                              |     |

|   |       | 1.8.1 Uncore Performance Monitoring State in MSR Space                                    | 20  |

|   |       | 1.8.2 Uncore Performance Monitoring State in PCICFG space                                 |     |

|   | 1.9   | Intro to Discovery - Self Describing HW                                                   |     |

|   |       | 1.9.1 Global Discovery                                                                    |     |

|   |       | 1.9.2 Unit Discovery                                                                      |     |

|   | 1.10  | Some Guidance for SW                                                                      |     |

|   |       | 1.10.1 On Finding PMON Discovery and Reading It                                           | 29  |

|   |       | 1.10.2 On Finding the Package's Bus Number for Uncore PMON Registers in PCICF             |     |

|   |       | Space                                                                                     | 32  |

|   |       | 1.10.3 On Resolving Addresses for Uncore PMON Registers in MMIO Space                     | 34  |

|   |       | 1.10.4 Setting up a Monitoring Session                                                    | 35  |

|   |       | 1.10.5 Reading the Sample Interval                                                        | 36  |

|   |       | 1.10.6 Enabling a New Sample Interval from Frozen Counters                                | 37  |

| 2 | 5th G | Gen Intel <sup>®</sup> Xeon <sup>®</sup> Scalable Processor Uncore Performance Monitoring | 38  |

| _ | 2.1   | Mesh Performance Monitoring                                                               |     |

|   | 2.1   | 2.1.1 Mesh Performance Monitoring Events                                                  |     |

|   |       | 2.1.2 CMS Box Events Ordered By Code                                                      |     |

|   |       | 2.1.2 CMS Box Performance Monitor Event List                                              |     |

|   | 2.2   | Caching/Home Agent (CHA) Performance Monitoring                                           |     |

|   | ۷.۷   | 2.2.1 CHA Performance Monitoring Overview                                                 |     |

|   |       | 2.2.2 Additional CHA Performance Monitoring                                               |     |

|   |       | 2.2.3 CHA Performance Monitoring Events                                                   |     |

|   |       | 2.2.4 CHA Box Events Ordered By Code                                                      |     |

|   |       | 2.2.5 CHA Box Common Metrics (Derived Events)                                             |     |

|   |       | 2.2.6 CHA Box Performance Monitor Event List                                              |     |

|   | 2.3   | Memory Controller (iMC) Performance Monitoring                                            |     |

|   | 2.3   | 2.3.1 Functional Overview                                                                 |     |

|   |       | 2.3.2 iMC Performance Monitoring Overview                                                 |     |

|   |       | 2.3.2 IMC Performance Monitoring Overview                                                 |     |

|   |       | <i>,</i>                                                                                  |     |

|   |       | 2.3.4 iMC Box Common Metrics (Derived Events)                                             |     |

|   | 2 4   | IIO Performance Monitoring                                                                |     |

|   | 2.4   |                                                                                           |     |

|   |       | 2.4.1 IIO Performance Monitoring Overview                                                 |     |

|   |       | 2.4.2 Additional IIO Performance Monitoring                                               |     |

|   |       | 2.4.3 IIO Performance Monitoring Events                                                   |     |

|   |       | 2.4.4 IIO Box Events Ordered By Code                                                      | 165 |

|      | 2.4.5 IIO Box Performance Monitor Event List            |       |

|------|---------------------------------------------------------|-------|

| 2.5  | IIO Ring Port (IRP) Performance Monitoring              |       |

|      | 2.5.1 IRP Performance Monitoring Overview               |       |

|      | 2.5.2 IRP Performance Monitoring Events                 |       |

|      | 2.5.3 IRP Box Events Ordered By Code                    |       |

|      | 2.5.4 IRP Box Performance Monitor Event List            |       |

| 2.6  | Intel® UPI Link Layer Performance Monitoring            |       |

|      | 2.6.1 Intel® UPI Performance Monitoring Overview        |       |

|      | 2.6.2 Additional Intel® UPI Performance Monitoring      |       |

|      | 2.6.3 Intel® UPI LL Performance Monitoring Events       |       |

|      | 2.6.4 Intel® UPI LL Box Events Ordered By Code          | 193   |

|      | 2.6.5 Intel® UPI LL Box Common Metrics (Derived Events) |       |

|      | 2.6.6 Intel® UPI LL Box Performance Monitor Event List  | 195   |

| 2.7  | M2M Performance Monitoring                              |       |

|      | 2.7.1 M2M Performance Monitoring Overview               | 208   |

|      | 2.7.2 Additional M2M Performance Monitoring             | 208   |

|      | 2.7.3 M2M Performance Monitoring Events                 |       |

|      | 2.7.4 M2M Box Events Ordered By Code                    |       |

|      | 2.7.5 M2M Box Performance Monitor Event List            | 213   |

| 2.8  | M2PCIe* Performance Monitoring                          | 273   |

|      | 2.8.1 M2PCIe* Performance Monitoring Overview           |       |

|      | 2.8.2 M2PCIe* Performance Monitoring Events             |       |

|      | 2.8.3 M2PCIE Box Events Ordered By Code                 | 274   |

|      | 2.8.4 M2PCIE Box Performance Monitor Event List         | 275   |

| 2.9  | M3UPI Performance Monitoring                            |       |

|      | 2.9.1 M3UPI Performance Monitoring Overview             |       |

|      | 2.9.2 M3UPI Box Events Ordered By Code                  | 292   |

|      | 2.9.3 M3UPI Box Performance Monitor Event List          |       |

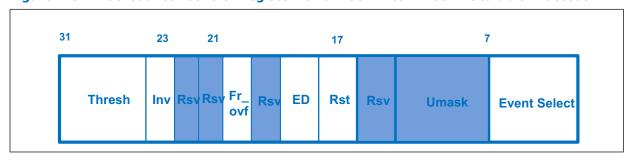

| 2.10 | Power Control (PCU) Performance Monitoring              |       |

|      | 2.10.1 PCU Performance Monitoring Overview              |       |

|      | 2.10.2 Additional PCU Performance Monitoring            |       |

|      | 2.10.3 PCU Performance Monitoring Events                |       |

|      | 2.10.4 PCU Box Events Ordered By Code                   |       |

|      | 2.10.5 PCU Box Common Metrics (Derived Events)          |       |

|      | 2.10.6 PCU Box Performance Monitor Event List           |       |

| 2.11 | MDF Performance Monitoring                              |       |

|      | 2.11.1 MDF Performance Monitoring Overview              |       |

|      | 2.11.2 MDF Box Events Ordered By Code                   | 333   |

|      | 2.11.3 MDF Box Performance Monitor Event List           | 334   |

| 2.12 | Compute Express Link* Performance Monitoring            | 337   |

|      | 2.12.1 CXL Performance Monitoring Overview              |       |

|      | 2.12.2 CXL CM Box Events Ordered By Code                |       |

|      | 2.12.3 CXL CM Performance Monitor Event List            |       |

|      | 2.12.4 CXL DP Box Events Ordered By Code                |       |

|      | 2.12.5 CXL DP Performance Monitor Event List            | 342   |

| Refe | ence for PMON Filtering                                 | 344   |

| 3.1  | Packet Matching Reference(s)                            |       |

| J. 1 | 3.1.1 Reference for CHA Packet Matching                 |       |

|      | 3.1.2 Reference for Intel UPI LL Packet Matching        | 340   |

|      | 31112 Reference for inter-off LE rucket Mutaling        | J-7 J |

3

## **Figures**

| 1                                                        | $-1$ $-5^{	ext{th}}$ Gen Intel $^{	ext{@}}$ Xeon $^{	ext{@}}$ Scalable Processor XCC Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 9                                                                                          |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                                                          | -2 Uncore PMON Components and Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| _                                                        | -3 PMON Global Control Register for 5 <sup>th</sup> Gen Intel <sup>®</sup> Xeon <sup>®</sup> Scalable Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| 1                                                        | -4 PMON Global Status Register for 5 <sup>th</sup> Gen Intel <sup>®</sup> Xeon <sup>®</sup> Scalable Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| 1                                                        | -5 PMON Unit Control Register for 5 <sup>th</sup> Gen Intel <sup>®</sup> Xeon <sup>®</sup> Scalable Processor - Common to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

|                                                          | PMON Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

| 1                                                        | -6 PMON Unit Status Register for 5 <sup>th</sup> Gen Intel <sup>®</sup> Xeon <sup>®</sup> Scalable Processor - Format Comm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | on                                                                                           |

|                                                          | to all PMON Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 1                                                        | -7 PMON Counter Control Register for 5 <sup>th</sup> Gen Intel <sup>®</sup> Xeon <sup>®</sup> Scalable Processor - Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

|                                                          | common to all PMON Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 15                                                                                         |

| 1                                                        | -8 PMON Counter Register for $5^{	ext{th}}$ Gen Intel $^{	ext{	iny R}}$ Xeon $^{	ext{	iny R}}$ Scalable Processor - Common to all                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

|                                                          | PMON Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

|                                                          | -9 Discovery - An Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

|                                                          | -10 Discovery - Visual Guide for How SW Strides Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                              |

|                                                          | -11 Discovery - Global State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

|                                                          | -12 Discovery - Unit State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

|                                                          | -1 CHA Counter Control Register for 5 <sup>th</sup> Gen Intel <sup>®</sup> Xeon <sup>®</sup> Scalable Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

|                                                          | -2 UmaskExt Filter Details for TOR_INSERT/OCCUPANCY Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

|                                                          | -3 UmaskExt Filter Details for the LLC_LOOKUP Event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

| _                                                        | -4 CHA PMON Filter Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

|                                                          | -5 PMON Control Register for DCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

|                                                          | -6 IIO Counter Control Register for 5 <sup>th</sup> Gen Intel <sup>®</sup> Xeon <sup>®</sup> Scalable Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

|                                                          | -7 M2M PMON Opcode Filter Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 209                                                                                          |

| 2                                                        | -8 PCU Counter Control Register for 5 <sup>th</sup> Gen Intel <sup>®</sup> Xeon <sup>®</sup> Scalable Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | )<br>24                                                                                      |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| <b>Tabl</b>                                              | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| _                                                        | -1 U_MSR_PMON_GLOBAL_CTL Register - Field Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|                                                          | -2 U_MSR_PMON_GLOBAL_STATUS Register - Field Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|                                                          | -3 PMON_UNIT_CTL Register - Field Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

|                                                          | -4 PMON_UNIT_STATUS Register - Field Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| 1                                                        | L Bacolino * DMON CTLy Dogistor Field Dotinitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

|                                                          | · · · · · · = · · = · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

|                                                          | -6 Baseline *_PMON_CTRx Register – Field Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 17                                                                                         |

|                                                          | -6 Baseline *_PMON_CTRx Register – Field Definitions<br>-7 Per-Box Performance Monitoring Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 17<br>. 19                                                                                 |

|                                                          | -6 Baseline *_PMON_CTRx Register – Field Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 17<br>. 19<br>. 20                                                                         |

| 1                                                        | -6 Baseline *_PMON_CTRx Register – Field Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 17<br>. 19<br>. 20<br>. 20                                                                 |

| 1<br>1                                                   | -6 Baseline *_PMON_CTRx Register - Field Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 17<br>. 19<br>. 20<br>. 20<br>. 23                                                         |

| 1<br>1<br>1                                              | Baseline *_PMON_CTRx Register - Field Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 17<br>. 19<br>. 20<br>. 20<br>. 23                                                         |

| 1<br>1<br>1<br>1                                         | Baseline *_PMON_CTRx Register - Field Definitions Per-Box Performance Monitoring Capabilities Blobal Performance Monitoring Registers (MSR) Uncore Performance Monitoring Registers (MSR) Free-running IIO Bandwidth In Counters in MSR space Free-running IIO Bandwidth Out Counters in MSR space Uncore Performance Monitoring Registers (PCICFG)                                                                                                                                                                                                                                                             | . 17<br>. 19<br>. 20<br>. 20<br>. 23<br>. 24                                                 |

| 1<br>1<br>1<br>1                                         | Baseline *_PMON_CTRx Register - Field Definitions Per-Box Performance Monitoring Capabilities Blobal Performance Monitoring Registers (MSR) Uncore Performance Monitoring Registers (MSR) Free-running IIO Bandwidth In Counters in MSR space Uncore Performance Monitoring Registers in MSR space Uncore Performance Monitoring Registers (PCICFG) Blobal Discovery- Field Definitions                                                                                                                                                                                                                         | . 17<br>. 19<br>. 20<br>. 20<br>. 23<br>. 24<br>. 24                                         |

| 1<br>1<br>1<br>1<br>1                                    | Baseline *_PMON_CTRx Register - Field Definitions Per-Box Performance Monitoring Capabilities Blobal Performance Monitoring Registers (MSR) Uncore Performance Monitoring Registers (MSR) Free-running IIO Bandwidth In Counters in MSR space Uncore Performance Monitoring Registers in MSR space Uncore Performance Monitoring Registers (PCICFG) Blobal Discovery- Field Definitions Unit Discovery- Field Definitions                                                                                                                                                                                       | . 17<br>. 19<br>. 20<br>. 20<br>. 23<br>. 24<br>. 24<br>. 28                                 |

| 1<br>1<br>1<br>1<br>1<br>1<br>2                          | Baseline *_PMON_CTRx Register - Field Definitions Per-Box Performance Monitoring Capabilities  Global Performance Monitoring Registers (MSR)  Uncore Performance Monitoring Registers (MSR)  Free-running IIO Bandwidth In Counters in MSR space  Free-running IIO Bandwidth Out Counters in MSR space  Uncore Performance Monitoring Registers (PCICFG)  Global Discovery- Field Definitions  Unit Discovery- Field Definitions  Measured CMS Box Events                                                                                                                                                       | . 17<br>. 19<br>. 20<br>. 23<br>. 24<br>. 24<br>. 28<br>. 39                                 |

| 1<br>1<br>1<br>1<br>1<br>2<br>2                          | Baseline *_PMON_CTRx Register - Field Definitions Per-Box Performance Monitoring Capabilities  Global Performance Monitoring Registers (MSR)  Uncore Performance Monitoring Registers (MSR)  Free-running IIO Bandwidth In Counters in MSR space  I Free-running IIO Bandwidth Out Counters in MSR space  Uncore Performance Monitoring Registers (PCICFG)  Global Discovery- Field Definitions  Unit Discovery- Field Definitions  Measured CMS Box Events  Cn_MSR_PMON_CTL{3-0} Register - Field Definitions                                                                                                  | . 17<br>. 19<br>. 20<br>. 23<br>. 24<br>. 24<br>. 28<br>. 29<br>. 39                         |

| 1<br>1<br>1<br>1<br>1<br>2<br>2<br>2                     | Baseline *_PMON_CTRx Register - Field Definitions Per-Box Performance Monitoring Capabilities Blobal Performance Monitoring Registers (MSR) Uncore Performance Monitoring Registers (MSR) Free-running IIO Bandwidth In Counters in MSR space Free-running IIO Bandwidth Out Counters in MSR space Uncore Performance Monitoring Registers (PCICFG) Blobal Discovery- Field Definitions Unit Discovery- Field Definitions Measured CMS Box Events Cn_MSR_PMON_CTL{3-0} Register - Field Definitions UmaskExt Filter Details for TOR_INSERT/OCCUPANCY Events                                                     | . 17<br>. 19<br>. 20<br>. 23<br>. 24<br>. 24<br>. 28<br>. 29<br>. 39                         |

| 1<br>1<br>1<br>1<br>1<br>2<br>2<br>2<br>2                | Baseline *_PMON_CTRx Register - Field Definitions Per-Box Performance Monitoring Capabilities Biological Performance Monitoring Registers (MSR) Uncore Performance Monitoring Registers (MSR) Free-running IIO Bandwidth In Counters in MSR space If ree-running IIO Bandwidth Out Counters in MSR space Uncore Performance Monitoring Registers (PCICFG) Global Discovery- Field Definitions Unit Discovery- Field Definitions Measured CMS Box Events Cn_MSR_PMON_CTL{3-0} Register - Field Definitions UmaskExt Filter Details for TOR_INSERT/OCCUPANCY Events UmaskExt Filter Details for LLC_LOOKUP Events | . 17<br>. 19<br>. 20<br>. 20<br>. 23<br>. 24<br>. 24<br>. 28<br>. 29<br>. 39<br>. 81<br>. 82 |

| 1<br>1<br>1<br>1<br>1<br>2<br>2<br>2<br>2<br>2           | Baseline *_PMON_CTRx Register - Field Definitions Per-Box Performance Monitoring Capabilities Biobal Performance Monitoring Registers (MSR) Uncore Performance Monitoring Registers (MSR) Free-running IIO Bandwidth In Counters in MSR space Uncore Performance Monitoring Registers (PCICFG) Biobal Discovery- Field Definitions Unit Discovery- Field Definitions Measured CMS Box Events Cn_MSR_PMON_CTL{3-0} Register - Field Definitions UmaskExt Filter Details for TOR_INSERT/OCCUPANCY Events UmaskExt Filter Details for LLC_LOOKUP Events Cn_MSR_PMON_BOX_FILTER Register - Field Definitions        | . 17<br>. 19<br>. 20<br>. 23<br>. 24<br>. 28<br>. 29<br>. 39<br>. 81<br>. 82<br>. 83         |

| 1<br>1<br>1<br>1<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | Baseline *_PMON_CTRx Register - Field Definitions Per-Box Performance Monitoring Capabilities Biological Performance Monitoring Registers (MSR) Uncore Performance Monitoring Registers (MSR) Free-running IIO Bandwidth In Counters in MSR space If ree-running IIO Bandwidth Out Counters in MSR space Uncore Performance Monitoring Registers (PCICFG) Global Discovery- Field Definitions Unit Discovery- Field Definitions Measured CMS Box Events Cn_MSR_PMON_CTL{3-0} Register - Field Definitions UmaskExt Filter Details for TOR_INSERT/OCCUPANCY Events UmaskExt Filter Details for LLC_LOOKUP Events | . 17<br>. 19<br>. 20<br>. 23<br>. 24<br>. 24<br>. 28<br>. 29<br>. 39<br>. 81<br>. 82<br>. 83 |

| 2-129 | MC_CHy_PCI_PMON_FIXED_CTL Register - Field Definitions                            | 131  |

|-------|-----------------------------------------------------------------------------------|------|

| 2-130 | MC_CHy_PCI_PMON_CTR{FIXED,3-0} Register - Field Definitions                       | 131  |

| 2-131 | MC_MMIO_PMON_FRCTR_DCLK Register - Field Definitions                              | 132  |

| 2-132 | MC_MMIO_PMON_FRCTR_WPQ_ACTIVE Register - Field Definitions                        | 132  |

| 2-133 | MC_MMIO_PMON_FRCTR_RPQ_ACTIVE Register - Field Definitions                        | 132  |

| 2-134 | Directly Measured iMC Box Events                                                  | 132  |

| 2-135 | Commonly Calculated From IMC Box Events                                           | 134  |

| 2-184 | IIOn_MSR_PMON_CTL{3-0} Register - Field Definitions                               | 164  |

| 2-185 | IIO_MSR_PMON_FRCTR_IOCLK Register - Field Definitions                             | 164  |

| 2-186 | IIO_MSR_PMON_FRCTR_BW_IN_P{0-7} Register - Field Definitions                      | 164  |

| 2-187 | IIO_MSR_PMON_FRCTR_BW_OUT_P{0-7} Register - Field Definitions                     | 165  |

| 2-188 | Directly Measured IIO Box Events                                                  | 165  |

| 2-205 | Directly Measured IRP Box Events                                                  | 183  |

| 2-212 | UPI_RATE_STATUS Register - Field Definitions                                      | 193  |

|       | U_Ly_PCI_PMON_LINK_IDLE Register - Field Definitions                              |      |

| 2-214 | U_Ly_PCI_PMON_LINK_LLR Register - Field Definitions                               | 193  |

| 2-215 | Directly Measured Intel® UPI LL Box Events                                        | 193  |

| 2-216 | Metrics Commonly Calculated From Intel® UPI LL Box Events                         | 195  |

| 2-231 | Additional M2M Performance Monitoring Registers (PCICFG)                          | 208  |

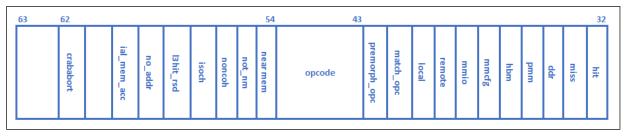

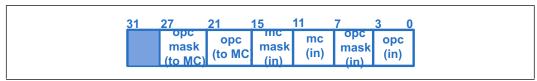

| 2-232 | M2Mn_PCI_PMON_OPCODE_MM Register - Field Definitions                              | 209  |

| 2-233 | M2Mn_PCI_PMON_ADDR{MASK,MATCH}0 Register - Field Definitions                      | 210  |

| 2-234 | M2Mn_PCI_PMON_ADDR{MASK,MATCH}1 Register - Field Definitions                      | 210  |

|       | Directly Measured M2M Box Events                                                  |      |

| 2-333 | Directly Measured M2PCIE Box Events                                               | 274  |

| 2-367 | Directly Measured M3UPI Box Events                                                | 292  |

|       | PCU_MSR_PMON_BOX_FILTER Register - Field Definitions                              |      |

| 2-420 | PCU Configuration Examples                                                        | 325  |

| 2-421 | Directly Measured PCU Box Events                                                  | 326  |

|       | Metrics Commonly Calculated From PCU Box Events                                   |      |

| 2-423 | Directly Measured MDF Box Events                                                  | 334  |

| 2-429 | Directly Measured CXL CM Box Events                                               | 337  |

| 2-439 | Directly Measured CXL DP Box Events                                               |      |

| 3-1   | Opcode Match by IDI Packet Type (Relevant to IRQ) for Cn_MSR_PMON_BOX_FILTER. 344 | .opo |

| 3-2   | Opcode Match by IDI Packet Type (Relevant to ISMQ) for Cn_MSR_PMON_BOX_FILTER.opc |      |

| 3-3   | Opcode Match by IDI Packet Type (Relevant to IPQ) for Cn_MSR_PMON_BOX_FILTER. 347 | .opo |

| 3-4   | Opcode Match by IDI Packet Type (relevant to RRQ) for Cn_MSR_PMON_BOX_FILTER. 348 | .opo |

| 3-5   | Opcode Match by IDI Packet Type (Relevant to WBQ) for Cn_MSR_PMON_BOX_FILTER.opc  | 348  |

| 3-6   | Intel® UPI Interconnect Packet Message Classes                                    |      |

| 3-7   | UPI Opcode Match by Message Class                                                 |      |

| 3-8   | UPI Opcodes (Alphabetical Listing)                                                |      |

# **Revision History**

| Revision<br>Number | Description      | Date        |

|--------------------|------------------|-------------|

| 001                | Initial Release. | August 2024 |

8

## 1 Introduction

#### 1.1 Introduction

'Uncore' roughly equates to logic outside the CPU cores but residing on the same die. Traffic (for example, data reads) generated by threads executing on CPU cores or IO devices may be operated on by logic in the uncore. Logic responsible for managing coherency, managing access to the DIMMs, managing power distribution and sleep states, and so forth.

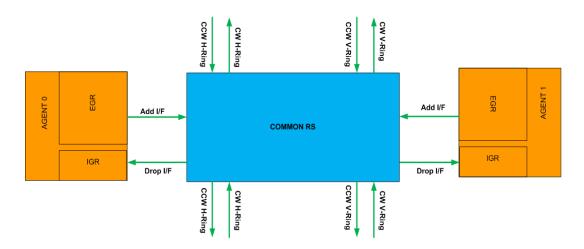

The uncore sub-system of the next generation Intel<sup>®</sup> Xeon<sup>®</sup> Server Processor is shown in Figure 1-1. The uncore sub-system consists of a variety of components, many assigned to the aforementioned responsibilities, ranging from the CHA cache/home agent to the Power Controller Unit (PCU) and Integrated Memory Controller (IMC), to name a few. Most of these components provide similar performance monitoring capabilities.

1x16/2x8/ 1x16/2x8/ 1x16/2x8/ 4x4/8x2 4x4/8x2 4x4/8x2 1x24 1x24 **EMR** PCIe Gen4 / PCIe Gen4 / PCIe Gen4 / 20GT 20GT XCC Gen5 Gen5 Gen5 **PMON** Blocks

Gbl Ctrl

Shadow

FR Ctrs M2IOSF D МЗИРІ PCIe ŲРІ **T**UPI (FxB) (FxB) (FxB) LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA Core Core Core Core Core Core Core LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA Core Core Core Core Core Core Core LLC/CHA LLC/CHA 2x DDR5 LLC/CHA LLC/CHA 2xDDR5 5600 MC MC MC 2 5600 ◀ Core Core Core Core DDRT2 DDRT2 LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA Core Core Core Core Core Core Core LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA Core Core Core Core Core Core Core MDFI MDFI MDFI **I** DFI MDFI MDFI LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA Core Core Core Core Core Core Core LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA Core Core Core Core Core Core Core 2x DDR5 2xDDR5 LLC/CHA MC MC LLC/CHA 5600 MC 2 LLC/CHA LLC/CHA 5600 DDRT2 Core Core Core Core DDRT2 LLC/CHA LLC/CHA LLC/CHÆ LLC/CHA LLC/CHA LLC/CHA LLC/CHA Core Core Core Core Core Core Core LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA LLC/CHA Core Core Core Core Core Core Core PCle PCle UPI UPI (FxB) (FxB) (FxB) 1x8 Gen3/Gen4 1x16/2x8/ 1x24 20GT 1x24 20GT 1x16/2x8/ DMI 4x4/8x2 4x4/8x2 1x8/2x4/4x2 PCle Gen4 / PCIe Gen4 / PCle Gen4 on Gen5 Gen5 non legacy socket

Figure 1-1. 5<sup>th</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor XCC Block Diagram

Before going in to the details of 5<sup>th</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor's uncore PMON, the following sections will provide:

- A general overview of Uncore PMON operation and the state provided SW to manage its operation.

- Functionality common to individual units with the common logic to support the functionality.

- A summary of 5<sup>th</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor uncore performance monitoring capabilities.

- Addressing all 5<sup>th</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor uncore performance monitoring state.

- Introduction to new discovery mechanism.

- Some guidance to SW including how to manage a monitoring session, find the base address to the page of Discovery and find the base addresses for PMON registers addressed in PCICFG or MMIO space.

#### 1.2 Section References

The following sections provide a breakdown of the performance monitoring capabilities for each box.

- Section 2.1, "Mesh Performance Monitoring".

- Section 2.2, "Caching/Home Agent (CHA) Performance Monitoring".

- Section 2.3, "Memory Controller (iMC) Performance Monitoring".

- Section 2.4, "IIO Performance Monitoring".

- Section 2.5, "IIO Ring Port (IRP) Performance Monitoring".

- Section 2.6, "Intel® UPI Link Layer Performance Monitoring".

- Section 2.7, "M2M Performance Monitoring".

- Section 2.8, "M2PCIe\* Performance Monitoring".

- Section 2.9, "M3UPI Performance Monitoring".

- Section 2.10, "Power Control (PCU) Performance Monitoring".

- Section 2.11, "MDF Performance Monitoring".

- Section 2.12, "Compute Express Link\* Performance Monitoring".

#### 1.3 Uncore PMON Overview

#### 1.3.1 A Simple Hierarchy

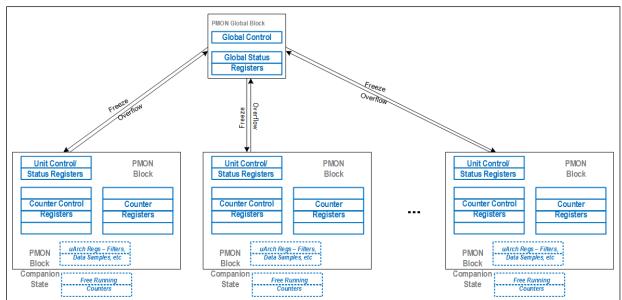

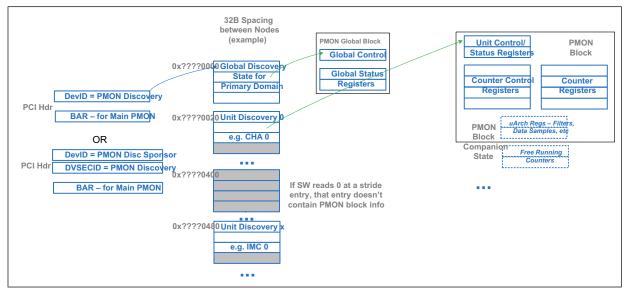

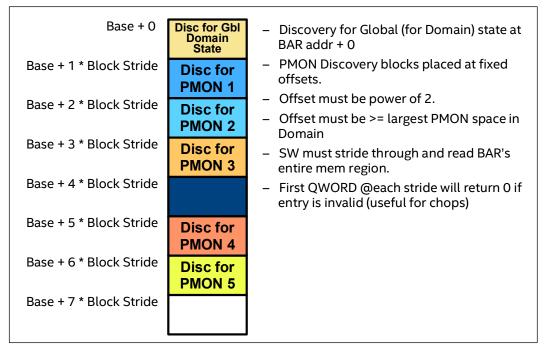

Uncore performance monitoring is managed through a very simple hierarchy. There are some number of Performance Monitoring (or **`PMON**') units governed by a global control.

Each PMON block contains a set of counters with paired control registers. Each unit provides a set of events for the SW to select from. The SW can ask the HW to collect an event by specifying what to count in a counter's control register. The SW can then periodically read the collected value from the paired counter.

Some units offer an expanded event set that require additional counter control bits. (for example, CHA, IIO, and Intel<sup>®</sup> Ultra Path Interconnect (Intel<sup>®</sup> UPI)).

Some units offer the ability to further refine, or 'filter', the monitored events through additional counter control registers.

Figure 1-2. Uncore PMON Components and Hierarchy

Note:

Uncore performance monitors represent a per-socket resource not meant to be affected by context switches and thread migration performed by the OS. It is recommended that the monitoring software agent establish a fixed affinity binding to prevent event count cross-talk across uncore PMON collected from different sockets.

To manage the large number of counter registers distributed across so many units and collect event data efficiently, each block has a modest amount of control/status governed by a similar global control/status.

The SW can directly synchronize actions across counters (for example, to start/stop/reset counting) within each PMON block or across all PMON blocks through this control state.

The SW can indirectly synchronize actions across counters (for example, stop counting) in all the PMON blocks by telling the HW what to do when a counter overflows. The SW can set a counter to overflow, after a set number of events have been captured, by preseeding the counter. For each counter, the SW can then choose whether to notify the global PMON control that a counter has overflowed.

12

Upon receipt of an overflow, the global control will assert the global freeze signal. Once the global freeze has been detected, each box will disable (or 'freeze') all of its counters. In the process of generating a global freeze, SW can configure the global control to send a PMI signal to the core executing the monitoring software.

The following sections will detail the basic control state provided to SW to control performance monitoring in the uncore.

#### 1.3.2 Global PMON State

#### 1.3.2.1 Global PMON Global Control/Status Registers

The following registers represent state governing all PMUs in the uncore, both to exert global control and collect unit-level information.

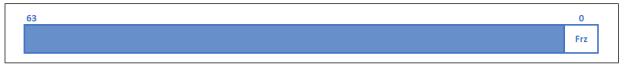

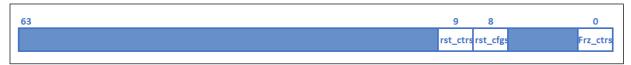

U\_MSR\_PMON\_GLOBAL\_CTL contains bits that can stop (.frz\_all) all the uncore counters.

Figure 1-3. PMON Global Control Register for 5<sup>th</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor

Table 1-1. U\_MSR\_PMON\_GLOBAL\_CTL Register - Field Definitions

| Field   | Bits | Attr | HW<br>Reset<br>Val | Description                             |  |

|---------|------|------|--------------------|-----------------------------------------|--|

| rsv     | 60:1 | RV   | 0                  | Reserved                                |  |

| frz_all | 0    | WO   | 0                  | Freeze all uncore performance monitors. |  |

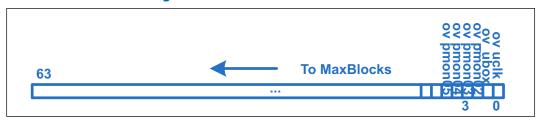

If an overflow is detected in any of the uncore's PMON registers, it will be summarized in one or more U\_MSR\_PMON\_GLOBAL\_STATUS registers. These registers accumulate overflows sent to it from uncore boxes with PMON blocks. To reset these overflow bits, a user must set the corresponding bits in U\_MSR\_PMON\_GLOBAL\_STATUS to 1, which will act to clear them.

Figure 1-4. PMON Global Status Register for 5<sup>th</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor

Table 1-2. U\_MSR\_PMON\_GLOBAL\_STATUS Register - Field Definitions

| Field                         | Bits                        | Attr | HW<br>Reset<br>Val | Description                                                                                                                        |

|-------------------------------|-----------------------------|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|

| rsv                           | 63:Max RV 0 Reserved Blocks |      | Reserved           |                                                                                                                                    |

| ov_pmonX                      | MaxBlo<br>cks-1:4           | RW1C | 0                  | Overflow detected in PMON register from Block with "Global Status Position" of "MaxBlocks-1" as reported through Global Discovery. |

| ov_pmonx-1: MaxBlo RV cks-2:4 |                             | RW1C | 0                  | Overflow detected in PMON register(s) from Blocks with a Global Status Position between MaxBlocks-1 and 3                          |

| ov_pmon03                     | 3                           | RW1C | 0                  | Overflow detected in PMON register from Block with "Global Status Position" of 3                                                   |

| ov_pmon02                     | 2                           | RW1C | 0                  | Overflow detected in PMON register from Block with "Global Status Position" of 2                                                   |

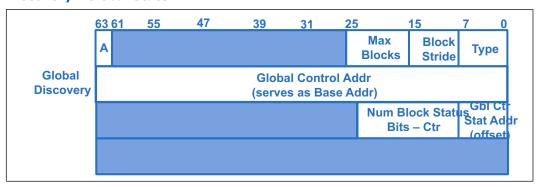

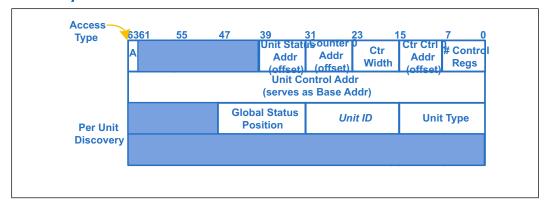

The mapping of Global Status bits in the Global Status register(s) to PMON blocks will be provided through the new PMON discovery mechanism. The status bits correspond to overflow's detected from PMON Block's IDed through discovery. Discovery for each PMON block will report its "Global Status Position" (that is, which bit in the global status register records its overflows).

For instance, the SW may discover a PMON block of Unit Type = CHA, Unit ID 5 has a Global Status Position of 5.

#### 1.4 Unit Level PMON State

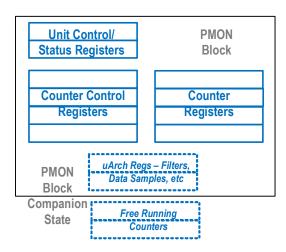

Each PMON block in the uncore is composed of the following state:

- A Unit Control register to aid software sample collection.

- Status registers to record when a counter within the Block overflows.

- A set of data registers

- A set of control registers, each paired to a data register, to allow the SW to specify what event should be captured.

- Additional micro-architectural specific state designed to enhance performance monitoring collection within a block. For example, event or traffic filters.

- Some free running counters, although not subject to the PMON hierarchy, may be included in this document with the unit they are associated with.

Every PMON block in the system is governed by a modest amount of unit-level control. Each bit intended to assist the SW in more efficiently managing the PMON state within the block. Reset bits help reduce the time the SW needs to setup a new sample.

#### Note:

14

If the PMON registers within the unit are shared among different users, either those users should leave this register untouched or they should agree on the user allowed to affect the unit level control state.

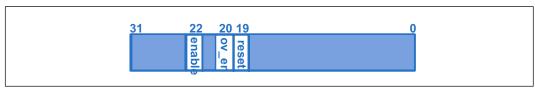

Figure 1-5. PMON Unit Control Register for 5<sup>th</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor - Common to all PMON Blocks

Table 1-3. PMON\_UNIT\_CTL Register - Field Definitions

| Field    | Bits | Attr | HW<br>Reset<br>Val | Description                                                                      |  |

|----------|------|------|--------------------|----------------------------------------------------------------------------------|--|

| rst_ctrs | 9    | WO   | 0                  | Reset Counters. When set to 1, the Counter Registers will be reset to 0.         |  |

| rst_ctrl | 8    | WO   | 0                  | Reset Control.  When set to 1, the Counter Control Registers will be reset to 0. |  |

| rsv      | 7:1  | RV   | 0                  | Reserved                                                                         |  |

| frz      | 0    | WO   | 0                  | Freeze.  If set to 1 the counters in this box will be frozen.                    |  |

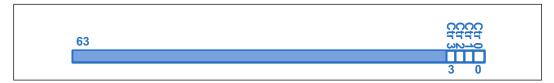

Figure 1-6. PMON Unit Status Register for 5<sup>th</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor - Format Common to all PMON Blocks

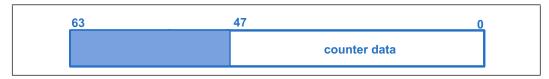

If an overflow is detected from one of the unit's PMON registers, the corresponding bit in the *PMON\_UNIT\_STATUS.ov* field will be set. To reset these overflow bits, a user must write a value of '1' to them (which will clear the bits). There are typically four counters per PMON block. But that number may vary. As of the 5<sup>th</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor, the number of paired counter/counter control registers is reported through the unit discovery associated with each PMON block. The Unit Status register will contain "NumControlRegs" valid bits.

Note:

You can also check Table 1-7, "Per-Box Performance Monitoring Capabilities" or the section detailing each unit's functionality for the number counters it supports.

Table 1-4. PMON\_UNIT\_STATUS Register - Field Definitions

| Field | Bits                           | Attr | HW<br>Reset<br>Val | Description                                                                                                                                                                                                                                                                                                     |

|-------|--------------------------------|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rsv   | 31:4                           | RV   | 0                  | Reserved                                                                                                                                                                                                                                                                                                        |

| ov    | NumC<br>ontrol<br>Regs-<br>1:0 | RW1C | 0                  | If an overflow is detected from the corresponding PMON_CTR register, its overflow bit will be set.  Note: Write of `1' will clear the bit.  Although four is very common, the number of overflow bits can vary by PMON block. The number can be discovered in the NumControlRegs field of the unit's discovery. |

#### 1.4.0.1 Unit PMON state - Counter/Control Pairs

The following table defines the layout for the standard performance monitor control registers. Their main task is to select the event to be monitored by their respective data counter (.ev\_sel, .umask). Additional control bits are provided to shape the incoming events (for example, .invert, .edge\_det, .thresh) as well as provide additional functionality for monitoring software (.rst).

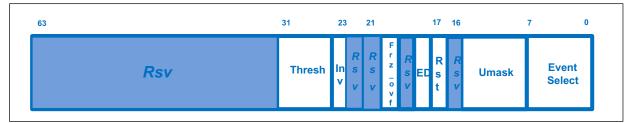

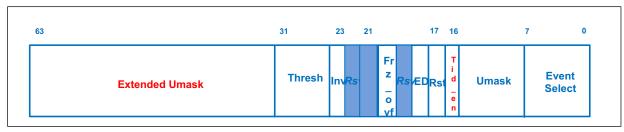

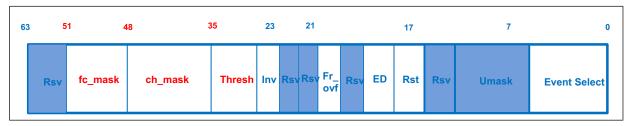

Figure 1-7. PMON Counter Control Register for 5<sup>th</sup> Gen Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor - Fields common to all PMON Blocks

Note:

Per Unit considerations - refer to each unit's section for more detail on:

- Certain units may make use of additional bits in these counter control registers.

- The width of the Thresh field is dependent on a unit's 'widest' event (that is, the event that can increment the most per cycle, typically measuring per-cycle occupancy of a large queue).

- Several unit counter control registers are still 32b, some 64b. All are addressable as 64b registers.

An overview of the counter control logic is in the next section.

16

Table 1-5. Baseline \*\_PMON\_CTLx Register - Field Definitions

| Field        | Bits                                                     | Attr | HW<br>Reset<br>Val                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|--------------|----------------------------------------------------------|------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| rsv          | 63:32                                                    | RV   | 0                                                          | Reserved -<br>Only relevant to unit's that use 64b control registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| thresh       | 31:24                                                    | RW   | 0                                                          | Threshold is used, along with the invert bit, to compare against the counter's incoming increment value. That is, the value that will be added to the counter.  For events that increment by more than 1 per cycle, if the threshold is set to a value greater than 1, the data register will accumulate instances in which the event increment is ≥ threshold.  For example, say you have an event to accumulate the occupancy of a 64-entry queue every cycle. By setting the threshold value to 60, the data register would count the number of cycles the queue's occupancy was ≥ 60. |  |

| invert(inv)  | 23                                                       | RW   | 0                                                          | Invert comparison against Threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|              |                                                          |      |                                                            | 0 - Comparison will be 'is event increment >= threshold?' 1 - Comparison is inverted - 'is event increment < threshold?'                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|              |                                                          |      |                                                            | For example, for a 64-entry queue, if the SW wanted to know how many cycles the queue had fewer than four entries, the SW should set the threshold to 4 and set the invert bit to 1.                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|              |                                                          |      |                                                            | <b>Note:</b> .invert is in series following .thresh. Due to this, the .thresh field must be set to a non-0 value. For events that increment by no more than 1 per cycle, set .thresh to 0x1.                                                                                                                                                                                                                                                                                                                                                                                              |  |

|              |                                                          |      |                                                            | Also, if .edge_det is set to 1, the counter will increment when a 1 to 0 transition (that is, falling edge) is detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| rsv          | 22:21                                                    | RV   | 0                                                          | Reserved. SW must write to 0 else behavior is undefined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| frz_ovf      | 20                                                       | RW/V | 0                                                          | Freeze on overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |