# 4th Gen Intel<sup>®</sup> Xeon<sup>®</sup> Processor Scalable Family, Codename Sapphire Rapids

**Data Sheet Volume 1**

Rev. 1.0

August 2024

Doc. No.: 814093, Rev.: 1.0

**Note:** This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

This document contains information on products, services and/or processes in development.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit http://www.intel.com/design/literature.htm.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel does not control or audit third-party benchmark data or the web sites referenced in this document. You should visit the referenced web site and confirm whether referenced data are accurate.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

Intel, the Intel logo, and Xeon are trademarks of Intel Corporation or its subsidiaries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2024, Intel Corporation. All rights reserved.

## **Contents**

August 2024

Doc. No.: 814093, Rev.: 1.0

| Revision History  Products this Document Applies To                                                                                                                                                     |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.0 Introduction                                                                                                                                                                                        | q  |

| 1.1 Structure and Scope                                                                                                                                                                                 |    |

| 1.2 Related Publications.                                                                                                                                                                               |    |

| 1.3 Terminology                                                                                                                                                                                         |    |

| 5.                                                                                                                                                                                                      |    |

| 2.0 Overview, Features, and Topologies                                                                                                                                                                  | 16 |

| 2.1 4th Gen Intel <sup>®</sup> Xeon <sup>®</sup> Processor Scalable Family, Codename Sapphire Rapids/5th<br>Gen Intel <sup>®</sup> Xeon <sup>®</sup> Processor Scalable Family, Codename Emerald Rapids |    |

| Processor Features and Topologies                                                                                                                                                                       | 17 |

| 2.1.1 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire                                                                                                                                 |    |

| Rapids and 5th Gen Intel® Xeon® Processor Scalable Family, Codename                                                                                                                                     |    |

| Emerald Rapids Processor Overview                                                                                                                                                                       |    |

| 2.2 Workstation Features and Topologies                                                                                                                                                                 | 23 |

| 3.0 Core Functional Description                                                                                                                                                                         | 26 |

| ·                                                                                                                                                                                                       |    |

| 4.0 PCI Express* Modules Functional Description                                                                                                                                                         |    |

| 4.1 Direct Media Interface 3 (DMI3)                                                                                                                                                                     |    |

| 4.2 Intel Data Streaming Accelerator Technology                                                                                                                                                         |    |

| 4.4 Intel® Virtualization Technology (Intel® VT) for Directed I/O (Intel® VT-d)                                                                                                                         |    |

| 4.5 Volume Management Device (VMD)                                                                                                                                                                      |    |

| 4.6 IIO Power Management                                                                                                                                                                                |    |

| 4.7 IIO Interrupts                                                                                                                                                                                      |    |

| 4.8 PCI Express Hot-Plug/Removal Support                                                                                                                                                                |    |

| 4.8.1 Hot-Plug SMBus Controller Segment Support                                                                                                                                                         | 37 |

| 4.8.2 Standard PCI Express Hot-plug Interface                                                                                                                                                           |    |

| 4.8.3 Storage PCI Express Hot-plug Interface                                                                                                                                                            |    |

| 4.8.4 Surprise Hot-Plug                                                                                                                                                                                 |    |

| 4.9 Non-transparent Bridge                                                                                                                                                                              |    |

| 4.9.1 NTB Features Supported                                                                                                                                                                            |    |

| 4.10 Compute Express Link (CXL)                                                                                                                                                                         |    |

| 4.10.1 CXL.io                                                                                                                                                                                           |    |

| 4.10.3 System Architecture                                                                                                                                                                              |    |

| 4.10.4 CXL.cache                                                                                                                                                                                        |    |

| 4.11 PCIe Precision Time Measurement (PTM)                                                                                                                                                              |    |

| 4.12 Timed-GPIO (TGPIO)                                                                                                                                                                                 |    |

| 5.0 Intel Ultra Path Interconnect Version 2.0 (Intel UPI 2.0) Functional Description                                                                                                                    | 49 |

| 5.1 Link Power Management                                                                                                                                                                               |    |

| 6.0 Integrated Memory Controller (IMC) Functional Description                                                                                                                                           |    |

| 6.1 Memory Power Features                                                                                                                                                                               |    |

| 6.1.1 DDR5 Power Optimization Features                                                                                                                                                                  |    |

| 7.0 Intel QuickAssist Technology (Intel QAT)                                   | 54 |

|--------------------------------------------------------------------------------|----|

| 7.1 Overview                                                                   |    |

| 7.2 Intel QuickAssist Technology Features                                      |    |

| 8.0 Power Controller Unit (PCU) Functional Description                         |    |

| 8.1 PMax Detector                                                              |    |

| 8.2 Hardware-Controlled Performance States (HWP)                               |    |

| 8.3 Intel Speed Select Technology                                              |    |

| 8.3.1 Terminology                                                              |    |

| 8.4 Intel Speed Select Technology – Performance Profile                        |    |

| 8.4.1 Introduction                                                             |    |

| 8.4.2 Usage models                                                             |    |

| 8.4.3 Hardware Guided Scheduling                                               |    |

| 8.5 Intel Speed Select Technology - Base Frequency                             | 59 |

| 8.5.1 Intel SST-BF overview                                                    |    |

| 8.5.2 Changes over the Second Generation Intel Xeon Processor Scalable Family  |    |

| version of Intel SST-BF                                                        |    |

| 8.5.3 Intel SST-BF and Intel SST-PP Interactions                               | 60 |

| 8.5.4 Intel SST-BF and Intel SST-TF cross Interactions                         |    |

| 8.6 Intel Speed Select Technology - Turbo Frequency                            | 61 |

| 8.6.1 Introduction                                                             |    |

| 8.6.2 Architecture Implementation and Interfaces                               |    |

| 8.6.3 Intel SST-TF Table                                                       |    |

| 8.6.4 Software Interface                                                       |    |

| 8.7 Intel Speed Select Technology – Core Power                                 |    |

| 8.7.1 Introduction                                                             |    |

| 8.7.2 Overview                                                                 | 63 |

| 9.0 Reliability, Availability, and Serviceability (RAS) Functional Description | 64 |

| 10.0 Psys Close Loop Platform Power Management                                 | 67 |

| 10.1 Psys Benefits                                                             |    |

| Glossary                                                                       | 68 |

#### Figures—4th Gen Intel® Xeon® Processor Scalable Family. Codename Sapphire Rapids

# **Figures**

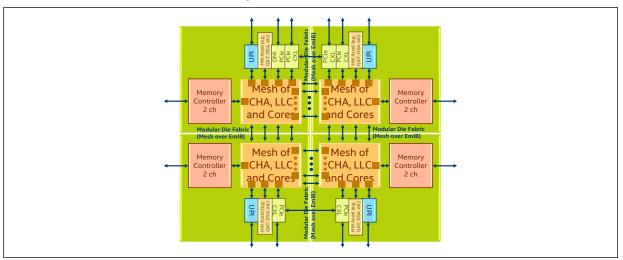

| 1  | 4th Gen Intel <sup>®</sup> Xeon <sup>®</sup> Processor Scalable Family, Codename Sapphire Rapids XCC |      |

|----|------------------------------------------------------------------------------------------------------|------|

|    | Architecture Example                                                                                 | 16   |

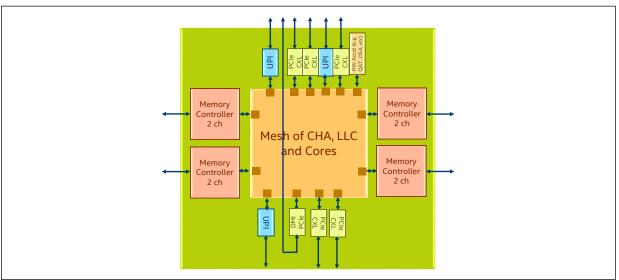

| 2  | 4th Gen Intel <sup>®</sup> Xeon <sup>®</sup> Processor Scalable Family, Codename Sapphire Rapids MCC |      |

|    | Architecture Example                                                                                 |      |

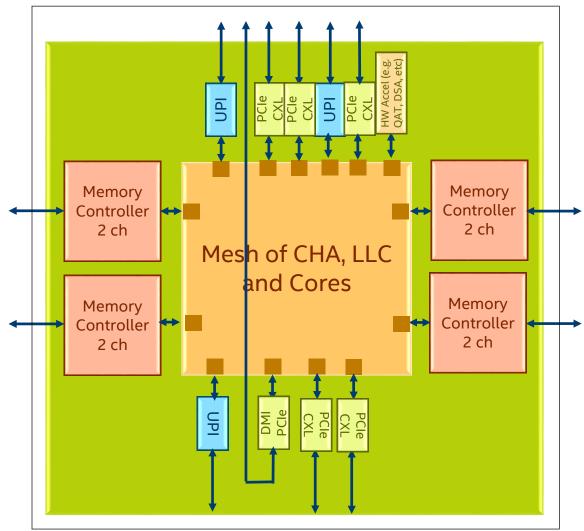

| 3  | 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids XCC                         |      |

| 4  | 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids MCC                         |      |

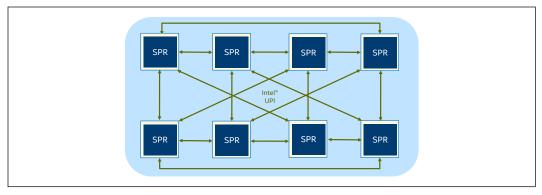

| 5  | 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids Server 850                  | . 21 |

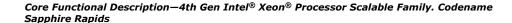

| 6  | PCI Express* Lane Partitioning                                                                       | . 28 |

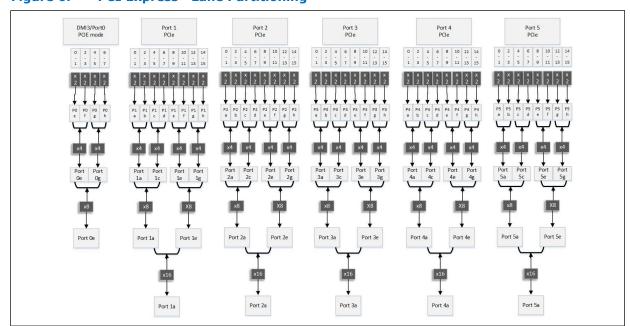

| 7  | TGPIO Example - Time-Aware GPIO Use                                                                  | . 48 |

| 8  | IMC Block Diagram for 8 DDR5 Channel Processor Type                                                  | . 51 |

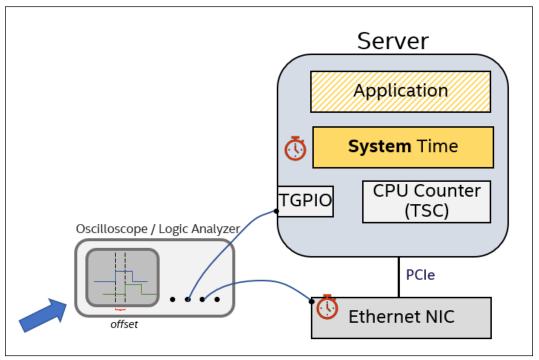

| 9  | One Server with Multiple Configurations                                                              | 58   |

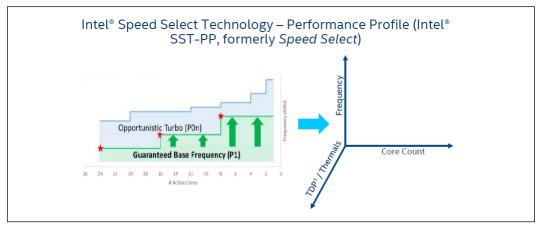

| 10 | Intel® SST-PP with Core Count, TDP/Thermal and Frequency                                             | 58   |

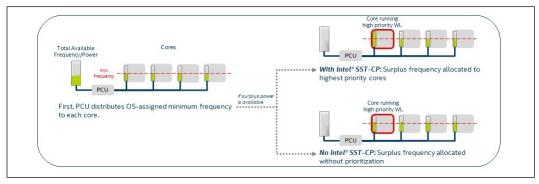

| 11 | CPU Frequency Budget Distribution                                                                    | 63   |

#### **Tables**

| 1  | Public Publications                                   | . 10 |

|----|-------------------------------------------------------|------|

| 2  | Server Features                                       | .19  |

| 3  | 2S Workstation Features                               | .23  |

| 4  | OS Initiated System States                            | . 35 |

| 5  | Standard PCI Express Hot-plug Interface               | . 38 |

| 6  | Storage PCI Express Hot-plug Interface                | . 39 |

| 7  | DDR5 Power Optimization Feature Summary               |      |

| 8  | Acronyms                                              |      |

| 9  | Intel® SST-BF and Intel® SST-TF Interoperation        |      |

| 10 | Intel® SST-BF and Intel® SST-TF Core Priority Setting |      |

|    | Standard RAS Feature List                             |      |

# **Revision History**

| Revision | Description     | Date        |

|----------|-----------------|-------------|

| 1.0      | Initial release | August 2024 |

4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids

August 2024 Data Sheet Volume 1

Doc. No.: 814093, Rev.: 1.0

# **Products this Document Applies To**

Eagle Stream platform with 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids processors and Intel® C740 Series Chipset PCH.

#### Introduction 1.0

This document provides functional descriptions of the 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids processor architecture.

#### NOTE

Features within this document may not be available on all platform segments, processor types, or processor SKUs.

4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids is the leadership wave 3 10-nm Intel® Xeon® multi-core server processor. The processor supports up to 52 bits of physical address space and 57 bits of virtual address space. Its design works for a platform that consists of at least one 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids processor and an Intel® C740 Series Chipset PCH. Including an Integrated Memory Controller (IMC) and an Integrated I/O (IIO) on a single silicon die in this family of processors.

The processor supports up to 80 lanes of PCI Express\* 5.0 links capable of 32 GT/s, and eight lanes of DMI. It features four IMC, each IMC supporting up to two channels of DDR5 DIMMs with up to two DIMMs per channel.

#### 1.1 Structure and Scope

The following lists summarize the structure and scope of each specification.

#### **Architecture Specification**

- Introduction

- Overview, Features, and Topologies

- Core Functional Description

- Integrated I/O and PCI Express Functional Description

- Intel® Ultra Path Interconnect Version 2.0 (Intel® UPI 2.0) Functional Description

- Integrated Memory Controller (IMC) Functional Description

- Intel® Quick Assist Technology (Intel® QAT)

- Power Controller Unit (PCU) Functional Description

- Reliability, Availability, Serviceability, and Manageability (RAS) Functional Description

#### **Register Specification**

- Configuration Process and Registers Overview

- Configuration Space Registers (CSR)

- Model Specific Registers (MSR)

#### **Electrical Specification**

August 2024 Data Sheet Volume 1 Doc. No.: 814093, Rev.: 1.0

- Introduction

- Electrical Specifications

- Processor Land Listing

- Processor Signal Descriptions

#### 1.2 Related Publications

See the following documents for additional information.

#### **Table 1. Public Publications**

| Document                                                                                                                                                                                                                                                                                                                | Document Number/Location                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Configuration and Power Interface Specification 4.0                                                                                                                                                                                                                                                            | http://www.acpi.info/                                                                                                                                  |

| PCI Local Bus Specification 3.0                                                                                                                                                                                                                                                                                         | http://www.pcisig.com/                                                                                                                                 |

| PCI Express Base Specification, Revision 5.0                                                                                                                                                                                                                                                                            | http://www.pcisig.com/                                                                                                                                 |

| PCI Express Base Specification, Revision 4.0                                                                                                                                                                                                                                                                            | http://www.pcisig.com/                                                                                                                                 |

| PCI Express Base Specification, Revision 3.0                                                                                                                                                                                                                                                                            | http://www.pcisig.com/                                                                                                                                 |

| PCI Express Base Specification, Revision 2.1                                                                                                                                                                                                                                                                            | http://www.pcisig.com/                                                                                                                                 |

| PCI Express Base Specification, Revision 1.1                                                                                                                                                                                                                                                                            | http://www.pcisig.com/                                                                                                                                 |

| PCIe* Gen 3 Connector High Speed Electrical Test Procedure                                                                                                                                                                                                                                                              | 325028-001 /http://www.intel.com/content/www/us/en/io/pci-express/pci-express-architecture-devnet-resources.html                                       |

| DDR5 SDRAM Specification and Register Specification                                                                                                                                                                                                                                                                     | http://www.jedec.org/                                                                                                                                  |

| Intel® 64 and IA-32 Architectures Software Developer's Manuals Volume 1: Basic Architecture Volume 2A: Instruction Set Reference, A-M Volume 2B: Instruction Set Reference, N-Z Volume 3A: System Programming Guide Volume 3B: System Programming Guide Intel® 64 and IA-32 Architectures Optimization Reference Manual | 325462 / http://www.intel.com/products/processor/manuals/index.htm                                                                                     |

| Intel® Virtualization Technology Specification for Directed I/O Architecture Specification                                                                                                                                                                                                                              | http://www.intel.com/content/www/us/en/intelligent-<br>systems/intel-technology/vt-directed-io-spec.html                                               |

| Intel® Trusted Execution Technology Software Development Guide                                                                                                                                                                                                                                                          | http://www.intel.com/technology/security/                                                                                                              |

| Intel® Data Streaming Accelerator Technology Specification                                                                                                                                                                                                                                                              | 341204-002 /<br>https://software.intel.com/content/www/us/en/develop/<br>articles/intel-data-streaming-accelerator-architecture-<br>specification.html |

| Intel 4th Gen Intel Xeon Processor Scalable Family (Code name Sapphire Rapids) Data Sheet Vol 2- Register                                                                                                                                                                                                               | TBD                                                                                                                                                    |

| Eagle Stream Platform Electrical Datasheet                                                                                                                                                                                                                                                                              | TBD                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                        |

# 1.3 Terminology

| Term                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ACS                                        | Access Control System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| ADI                                        | Assignable Device Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| AER                                        | Advanced Error Reporting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| AES                                        | Advanced Encryption Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| ARI                                        | Alternative Routing-ID Interpretation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| ASPM                                       | Active State Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| ATS                                        | Address Translation Services                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| BE                                         | Byte Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| ВМС                                        | Baseboard Management Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CA                                         | Coherency Agent. In some cases this is referred to as a Caching Agent though a CA is not actually required to have a cache. It is a term used for the internal logic providing mesh interface to LLC and Core. The CA is a functional unit in the CHA.                                                                                                                                                                                                                                                                  |  |

| CA                                         | Completer Abort (PCIe context)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| CAP                                        | CSR Access Proxy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| СНА                                        | The functional module that includes the CA (Coherency Agent) and HA (Home Agent).                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| CXPSMB                                     | Converged eXPress SMBus Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| DDR5                                       | Fifth generation Double Data Rate SDRAM Memory technology.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| DLLP                                       | Data Link Layer Packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| DMA                                        | Direct Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| DMI3                                       | Direct Media Interface Gen3 operating at PCI Express 3.0 speed.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| DTLB                                       | Data Translation Look-aside Buffer. Part of the processor core architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| DTS                                        | Digital Thermal Sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| ECC                                        | Error Correction Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Enhanced Intel®<br>SpeedStep<br>Technology | Allows the operating system to reduce power consumption when performance is not needed.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| ETR                                        | Eagle Tail Rings. Former naming conventions for WQM and WQM Rings                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Execute Disable Bit                        | The Execute Disable bit allows memory to be marked as executable or non-executable, when combined with a supporting operating system. If code attempts to run in non-executable memory the processor raises an error to the operating system. This feature can prevent some classes of viruses or worms that exploit buffer overrun vulnerabilities and can thus help improve the overall security of the system. See the Intel® 64 and IA-32 Architectures Software Developer's Manuals for more detailed information. |  |

| F0                                         | Function 0 - Intel® ME/Intel® QAT Cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| FC                                         | Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| FCC                                        | Flow Control Credits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| FLIT                                       | Flow Control Unit. The Intel® UPI Link layer's unit of transfer. A FLIT is made of multiple PHITS. A Flit is always a fixed amount of information (192 bits).                                                                                                                                                                                                                                                                                                                                                           |  |

| FLR                                        | Function Level Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                            | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids

August 2024 Data Sheet Volume 1

Doc. No.: 814093, Rev.: 1.0

| Term                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Functional<br>Operation                               | Refers to the normal operating conditions in which all processor specifications, including DC, AC, system bus, signal quality, mechanical, and thermal, are satisfied.                                                                                                                                                                                                                           |  |

| GSSE                                                  | Extension of the SSE/SSE2 (Streaming SIMD Extensions) floating point instruction set to 256b operands.                                                                                                                                                                                                                                                                                           |  |

| НА                                                    | A Home Agent (HA) orders read and write requests to a piece of coherent memory. The HA is implemented in the CHA logic.                                                                                                                                                                                                                                                                          |  |

| ICU                                                   | Instruction Cache Unit. Part of the processor core architecture.                                                                                                                                                                                                                                                                                                                                 |  |

| IFU                                                   | Instruction Fetch Unit. Part of the processor core.                                                                                                                                                                                                                                                                                                                                              |  |

| IIO                                                   | Integrated I/O Controller. An I/O controller that is integrated in the processor die. The IIO consists of the DMI3 module and PCIe modules.                                                                                                                                                                                                                                                      |  |

| IMC                                                   | Integrated Memory Controller. A Memory Controller that is integrated in the processor die.                                                                                                                                                                                                                                                                                                       |  |

| IMR                                                   | Isolated Memory Region. Part of the System Memory                                                                                                                                                                                                                                                                                                                                                |  |

| IMS                                                   | Interrupt Message Storage. Stores MSI-X vectors for Intel® Scalable IOV                                                                                                                                                                                                                                                                                                                          |  |

| Intel <sup>®</sup> AVX                                | Intel® Advanced Vector Extensions (Intel® AVX) promotes legacy 128-bit SIMD instruction sets that operate on XMM register set to use a "vector extension" (VEX) prefix and operates on 256-bit vector registers (YMM).                                                                                                                                                                           |  |

| Intel <sup>®</sup> AVX-512                            | The base of the 512-bit SIMD instruction extensions are referred to as Intel <sup>®</sup> AVX-512 foundation instructions. They include extensions of the Intel <sup>®</sup> AVX family of SIMD instructions but are encoded using a new encoding scheme with support for 512-bit vector registers, up to 32 vector registers in 64-bit mode, and conditional processing using opmask registers. |  |

| Intel <sup>®</sup> ME                                 | Intel® Management Engine. The processor uses Intel® ME 11 for 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids Workstation 1S, 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids Workstation 2S and 4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids HEDT.                                                                |  |

| Intel <sup>®</sup> QuickData<br>Technology            | Intel® QuickData Technology is a platform solution designed to maximize the throughput of server data traffic across a broader range of configurations and server environments to achieve faster, scalable, and more reliable I/O.                                                                                                                                                               |  |

| Intel® Ultra Path<br>Interconnect<br>(Intel® UPI2.0)  | A cache-coherent, link-based Interconnect specification for Intel® processors. Also known as Intel® UPI.                                                                                                                                                                                                                                                                                         |  |

| Intel® 64<br>Technology                               | 64-bit memory extensions to the IA-32 architecture. Further details on Intel® 64 architecture and programming model can be found at http://developer.intel.com/technology/intel64/.                                                                                                                                                                                                              |  |

| Intel <sup>®</sup> Scalable<br>IOV                    | Intel® Scalable I/O Virtualization                                                                                                                                                                                                                                                                                                                                                               |  |

| Intel® SPS FW                                         | Intel® Server Platform Services Firmware. The processor uses Intel® SPS FW in server configurations.                                                                                                                                                                                                                                                                                             |  |

| Intel® Turbo Boost<br>Technology                      |                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Intel® TXT                                            | Intel® Trusted Execution Technology                                                                                                                                                                                                                                                                                                                                                              |  |

| Intel® UPI 2.0                                        | Intel® Ultra Path Interconnect (Intel® UPI) Agent. An internal logic block providing interface between internal mesh and external Intel® UPI.                                                                                                                                                                                                                                                    |  |

| Intel®<br>Virtualization<br>Technology (Intel®<br>VT) | Processor Virtualization which when used in conjunction with Virtual Machine Monitor software enables multiple, robust independent software environments inside a single platform.                                                                                                                                                                                                               |  |

| Intel <sup>®</sup> VT-d                               | Intel® Virtualization Technology (Intel® VT) for Directed I/O. Intel® VT-d is a hardware assist, under system software (Virtual Machine Manager or OS) control, for enabling I/O device Virtualization. Intel® VT-d also brings robust security by providing protection from errant DMAs by using DMA remapping, a key feature of Intel® VT-d.                                                   |  |

|                                                       | continued                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Term                              | Description                                                                                                                                                                                                                  |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Integrated Heat<br>Spreader (IHS) | A component of the processor package used to enhance the thermal performance of the package. Component thermal solutions interface with the processor at the IHS surface.                                                    |  |

| IOMMU                             | I/O Memory Management Unit                                                                                                                                                                                                   |  |

| IOV                               | I/O Virtualization                                                                                                                                                                                                           |  |

| IOVM                              | I/O Virtual Machine                                                                                                                                                                                                          |  |

| IVR                               | Integrated Voltage Regulation (IVR): The processor supports several integrated voltage regulators.                                                                                                                           |  |

| KPT                               | Intel® Key Protection Technology                                                                                                                                                                                             |  |

| LLC                               | Last Level Cache                                                                                                                                                                                                             |  |

| LRDIMM                            | Load Reduced Dual In-line Memory Module                                                                                                                                                                                      |  |

| LRU                               | Least Recently Used. A term used in conjunction with cache allocation policy.                                                                                                                                                |  |

| M2M                               | Mesh to Memory. Logic in the IMC which interfaces the IMC to the mesh.                                                                                                                                                       |  |

| M2PCIe                            | The logic in the IIO modules which interface the modules to the mesh.                                                                                                                                                        |  |

| MESH                              | The on die interconnect which connects modules in the processor.                                                                                                                                                             |  |

| MLC                               | Mid Level Cache                                                                                                                                                                                                              |  |

| MPS                               | Maximum Payload Size                                                                                                                                                                                                         |  |

| MRdLk                             | Memory Read Lock                                                                                                                                                                                                             |  |

| MRRS                              | Maximum Read Request Size                                                                                                                                                                                                    |  |

| MSI                               | Message Signal Interrupt                                                                                                                                                                                                     |  |

| NCTF                              | Non-Critical to Function: NCTF locations are typically redundant ground or non-critical reserved, so the loss of the solder joint continuity at end of life conditions will not affect the overall product functionality.    |  |

| NID \ NodeID                      | Node ID (NID) or NodeID (NID). The processor implements up to 4- bits of NodeID (NID).                                                                                                                                       |  |

| Non-Posted<br>Request             | A non-posted request is a request which cannot be considered ordered (per PCI rules) until after the completion is received. Non-posted transactions include all reads and some writes (configuration writes).               |  |

| OOBMSM                            | Out-of-Band Management Service Module                                                                                                                                                                                        |  |

| Pcode                             | Pcode is microcode which is run on the dedicated microcontroller within the PCU.                                                                                                                                             |  |

| PCH                               | Platform Controller Hub. A chipset with centralized platform capabilities including the main I/O interfaces along with display connectivity, audio features, power management, manageability, security and storage features. |  |

| PCU                               | Power Control Unit.                                                                                                                                                                                                          |  |

| PCIe                              | PCI Express                                                                                                                                                                                                                  |  |

| PE                                | Processing Element: A processing element is a generic term indicating a CPU thread.                                                                                                                                          |  |

| PECI                              | Platform Environment Control Interface                                                                                                                                                                                       |  |

| PF                                | Physical Function (SR-IOV)                                                                                                                                                                                                   |  |

| Phit                              | The data transfer unit on Intel® UPI at the Physical layer is called a phit (physical unit). A Phit will be either 20 bits, or 8 bits depending on the number of active lanes.                                               |  |

| PME                               | Power Management Event                                                                                                                                                                                                       |  |

| Posted Request                    | A posted request is a request which can be considered ordered (per PCI rules) upon the issue of the request and therefore completions are unnecessary. Example of posted transaction are PCIe memory writes and messages     |  |

| Processor                         | Includes the 64-bit cores, uncore, I/Os and package                                                                                                                                                                          |  |

|                                   | continued                                                                                                                                                                                                                    |  |

4th Gen Intel® Xeon® Processor Scalable Family, Codename Sapphire Rapids

August 2024 Data Sheet Volume 1

Doc. No.: 814093, Rev.: 1.0

| Term               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Processor Core     | The term "processor core" refers to Si die itself which can contain multiple execution cores. Each execution core has an instruction cache and data cache and MLC cache. All execution cores share the L3 cache.                                                                                                                                                                                                                                                                                                                    |  |

| Rank               | A unit of DRAM corresponding four to eight devices in parallel, ignoring ECC. These devices are usually, but not always, mounted on a single side of a DDR5 DIMM.                                                                                                                                                                                                                                                                                                                                                                   |  |

| RC                 | Root Complex. Consists of a host bridge, PCIe port (root ports) and one or more RC integrated endpoints                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| RCEC               | Root Complex Event Collector, collects errors from PCIe RCiEPs, as defined in PCI Express Base Specification                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| RCiEP              | Root Complex Integrated Endpoint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| RCRB               | Root Complex Register Block as defined in PCI Express Base Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| RDIMM \ LRDIMM     | Registered Dual In-line Memory Module \ Load Reduced DIMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| RID                | Ring ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| RLT                | Rate Limiter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| RP                 | Root Port. A PCIe port on a root complex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| RTID               | Request Transaction IDs are credits issued by the CHA to track outstanding transaction, and the RTIDs allocated to a CHA are topology dependent.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| S3M                | Secure Startup Services Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| SCI                | System Control Interrupt. Used in ACPI protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| SKU                | Stock Keeping Unit (SKU) is a subset of a processor type with specific features, electrical, power and thermal specifications. Not all features are supported on all SKUs. A SKU is based on specific use condition assumption.                                                                                                                                                                                                                                                                                                     |  |

| SoC                | System on Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| SR-IOV             | Single Root IO Virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SSE                | Intel® Streaming SIMD Extensions (Intel® SSE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SMBus              | System Management Bus. A two-wire interface through which simple system and power management related devices can communicate with the rest of the system.                                                                                                                                                                                                                                                                                                                                                                           |  |

| SDU                | SMM Driver Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Storage Conditions | A non-operational state. The processor may be installed in a platform, in a tray, or loose. Processors may be sealed in packaging or exposed to free air. Under these conditions, processor landings should not be connected to any supply voltages, have any I/Os biased or receive any clocks. Upon exposure to "free air" (that is, unsealed packaging or a device removed from packaging material) the processor must be handled in accordance with moisture sensitivity labeling (MSL) as indicated on the packaging material. |  |