# **High Reliability Design Guidance**

White Paper

November 2023

-

Document Number: 792652-1.0

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit <a href="http://www.intel.com/design/literature.htm">www.intel.com/design/literature.htm</a>.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No product or component can be absolutely secure. Check with your system manufacturer or retailer or learn more at <u>intel.com</u>.

No product or component can be absolutely secure.

Intel, the Intel logo, are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

© Intel Corporation

# Contents

| 1.0 |     | Introduction                                           | 8  |

|-----|-----|--------------------------------------------------------|----|

|     | 1.1 | Terminologies                                          | 8  |

|     | 1.2 | Reference Documents                                    |    |

| 2.0 |     | Overview                                               |    |

|     | 2.1 | Reliability Definition and Index                       | 11 |

|     |     | 2.1.1 Failure Rates                                    |    |

|     |     | 2.1.2 MTBF                                             |    |

|     |     | 2.1.3 MTTR                                             | 12 |

|     |     | 2.1.4 Availability                                     | 13 |

|     | 2.2 | Bathtub Curve                                          | 13 |

|     | 2.3 | Design for Reliability Concept                         | 14 |

|     | 2.4 | System Reliability Validation                          | 16 |

|     | 2.5 | MTBF Prediction Methodology                            | 17 |

|     |     | 2.5.1 Flow of Reliability Prediction                   | 17 |

|     |     | 2.5.2 Steady State Failure Rate Prediction for Devices |    |

|     |     | 2.5.3 Failure Rate Prediction for Units                |    |

| 3.0 |     | Derating for Electronic Component                      | 21 |

|     | 3.1 | Components Derating Standards                          | 21 |

|     | 3.2 | Derating Level                                         |    |

|     | 3.3 | Example of Derating Design                             |    |

|     | 3.4 | Component Selection Criteria                           | 25 |

| 4.0 |     | Power Rails Monitoring                                 |    |

| 5.0 |     | Critical Signals Monitoring                            | 27 |

| 6.0 |     | Thermal Design and Monitoring                          |    |

|     | 6.1 | General Principles of Thermal Design                   |    |

|     | 6.2 | System Thermal Monitoring                              |    |

| 7.0 |     | Dual SPI Boot Flash Introduction                       |    |

|     | 7.1 | Value Provided by the Dual SPI Boot Flash Solution     |    |

|     | 7.2 | Dual Boot Flash Solution                               |    |

|     |     | 7.2.1 Hardware Architecture                            |    |

|     |     | 7.2.2 Software                                         |    |

|     | 7.3 | Dual Boot Flash Solution Working Flow                  |    |

| 8.0 |     | RTC Reset and Global Reset                             |    |

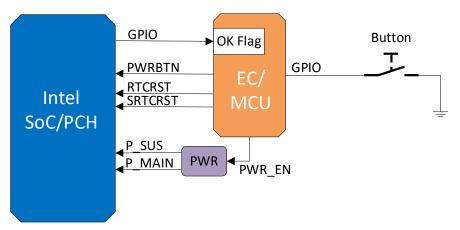

|     | 8.1 | Reset Hardware Diagram                                 |    |

|     |     | 8.1.1 EC/MCU Functions                                 |    |

|     |     | 8.1.2 Operation Process                                |    |

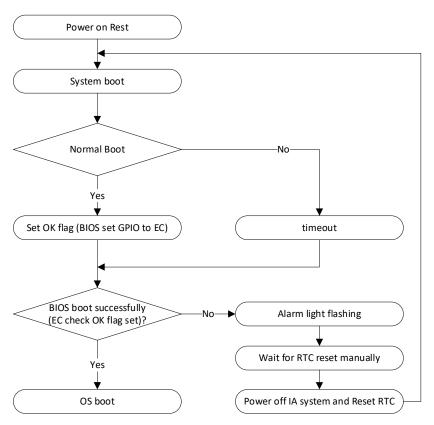

|     | 8.2 | Reset Working Flow                                     |    |

| 9.0  |      | Protection for Surprise Power Down                |    |  |  |  |

|------|------|---------------------------------------------------|----|--|--|--|

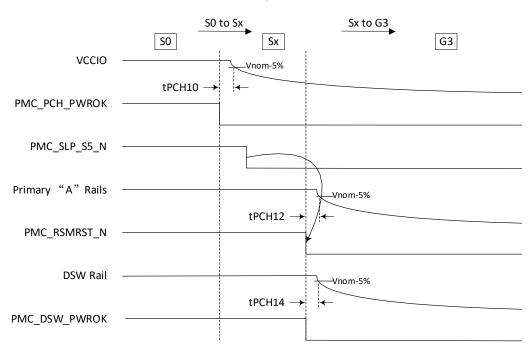

|      | 9.1  | Graceful Power Loss Requirement                   |    |  |  |  |

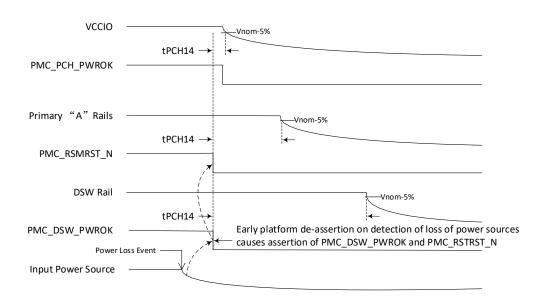

|      | 9.2  | Emergency (Surprise) Power Loss Requirement       |    |  |  |  |

|      | 9.3  | Emergency (Surprise) Power Loss Implement Example |    |  |  |  |

|      | 9.4  | EoM (End of Manufacturing)                        |    |  |  |  |

|      |      | 9.4.1 EoM Importance                              |    |  |  |  |

|      |      | 9.4.2 EoM Performs                                | 41 |  |  |  |

|      |      | 9.4.3 EoM Flow                                    | 41 |  |  |  |

| 10.0 |      | Memory Reliability and Availability               | 42 |  |  |  |

|      | 10.1 | Memory Reliability                                | 42 |  |  |  |

|      |      | 10.1.1 Memory Reliability Introduction            |    |  |  |  |

|      |      | 10.1.2 Memory Reliability Solution                |    |  |  |  |

|      | 10.2 | Memory Availability                               |    |  |  |  |

|      |      | 10.2.1 Memory Availability Introduction           |    |  |  |  |

|      |      | 10.2.2 Memory Availability Solution               |    |  |  |  |

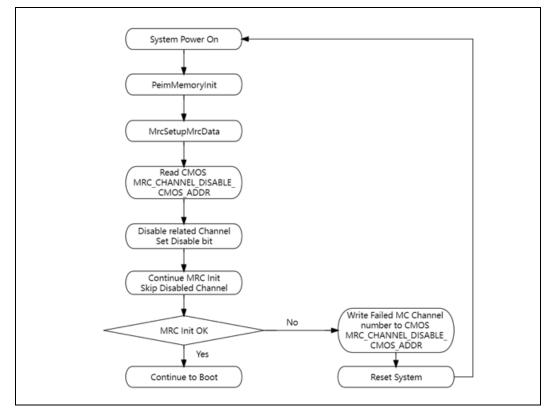

|      |      | 10.2.3 Memory Availability Workflow               |    |  |  |  |

|      | 10.3 | Conclusion                                        |    |  |  |  |

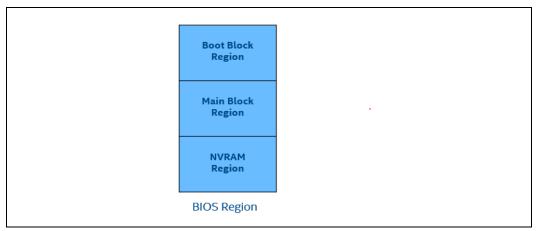

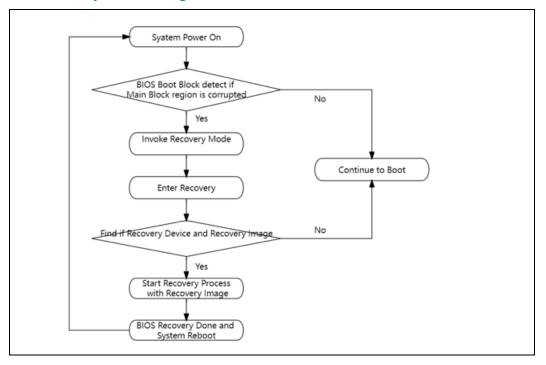

| 11.0 |      | BIOS Recovery                                     | 45 |  |  |  |

|      | 11.1 | BIOS Recovery Introduction                        |    |  |  |  |

|      | 11.2 | BIOS Recovery Solution                            |    |  |  |  |

|      |      | 11.2.1 Hardware Architecture                      |    |  |  |  |

|      |      | 11.2.2 Software                                   |    |  |  |  |

|      | 11.3 | BIOS Recovery Workflow                            | 47 |  |  |  |

|      | 11.4 | Conclusion                                        | 47 |  |  |  |

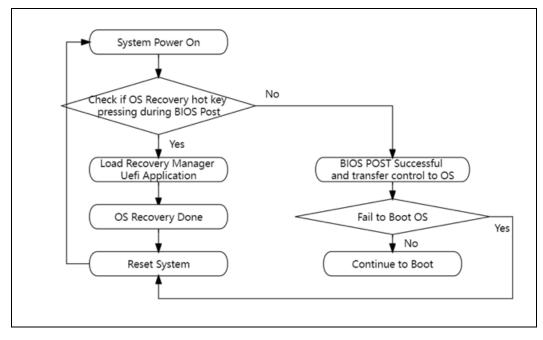

| 12.0 |      | OS Recovery                                       |    |  |  |  |

|      | 12.1 | OS Recovery Introduction                          |    |  |  |  |

|      | 12.2 | OS Recovery Solution                              |    |  |  |  |

|      |      | 12.2.1 The Advantage of OS Recovery Solution      |    |  |  |  |

|      |      | 12.2.2 The Disadvantage of OS Recovery Solution   |    |  |  |  |

|      |      | 12.2.3 Hardware Architecture                      |    |  |  |  |

|      |      | 12.2.4 Software                                   |    |  |  |  |

|      | 12.3 | OS Recovery Workflow                              |    |  |  |  |

| 13.0 |      | USB Recovery                                      | 50 |  |  |  |

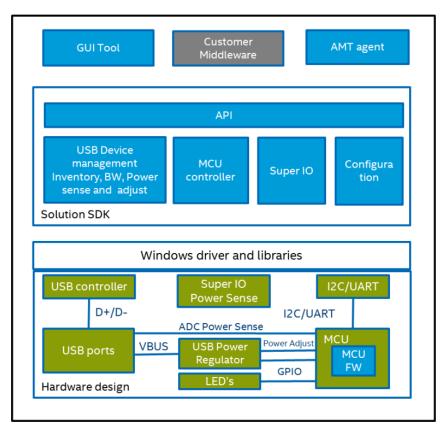

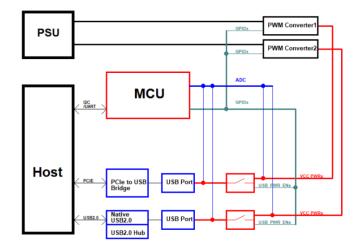

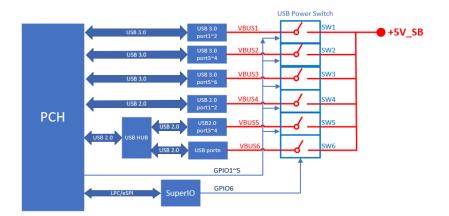

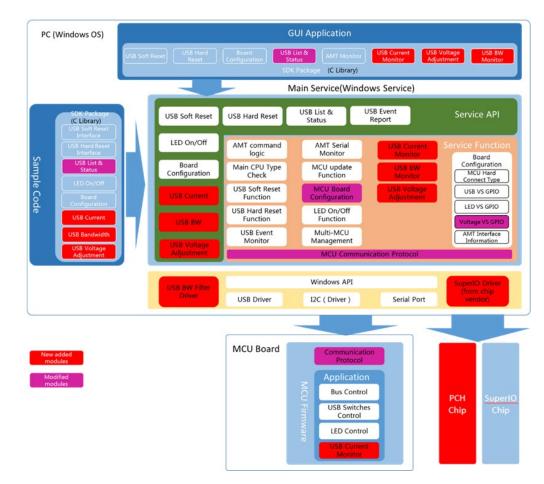

|      | 13.1 | System Design Overview                            |    |  |  |  |

|      | 13.2 | Hardware Reference Design                         | 51 |  |  |  |

|      | 13.3 | Software Design Architecture                      |    |  |  |  |

|      | 13.4 | Technical Collaterals for Reference Design        | 53 |  |  |  |

| 14.0 |      | Electromagnetic Compatibility                     |    |  |  |  |

|      | 14.1 | PCB Layout and Routing                            | 55 |  |  |  |

|      | 14.2 | 2 ESD Protection Design                           |    |  |  |  |

| 15.0 |      | Stack-up and PCB Consideration | 58 |

|------|------|--------------------------------|----|

|      | 15.1 | PCB Stack-up Guidance          |    |

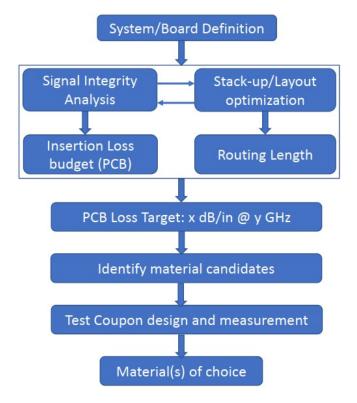

|      | 15.2 | PCB Material Guidance          | 58 |

| 16.0 |      | Solder Joint Reliability       | 60 |

# **Figures**

| Figure 1.  | Bathtub Curve                                      | 13 |

|------------|----------------------------------------------------|----|

| Figure 2.  | How To Do Reliability Design                       | 15 |

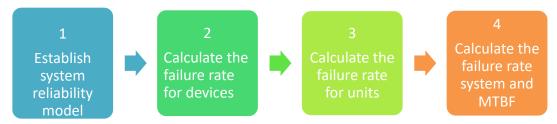

| Figure 3.  | Reliability Prediction Diagram                     | 18 |

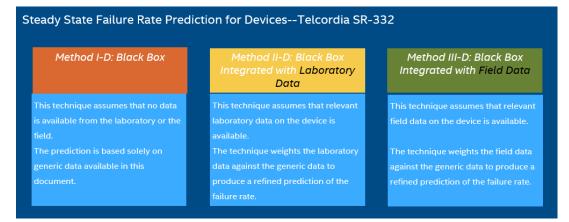

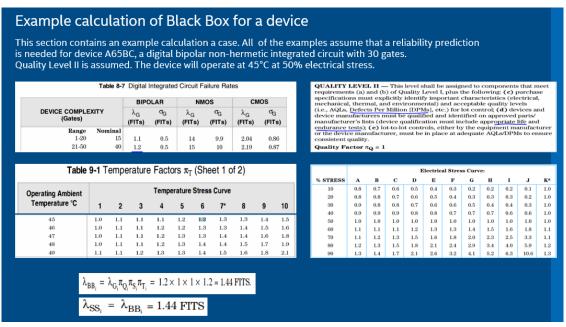

| Figure 4.  | Failure Rate Prediction Method                     | 19 |

| Figure 5.  | Example Calculation of Black Box                   | 19 |

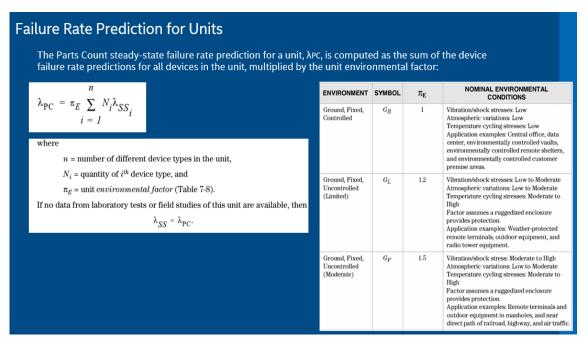

| Figure 6.  | Failure Rate Prediction                            | 20 |

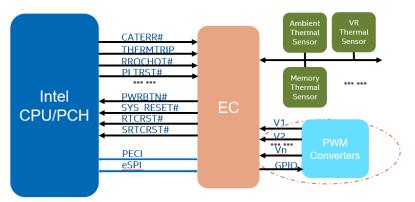

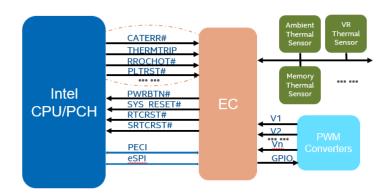

| Figure 7.  | Power Rails Monitoring                             | 26 |

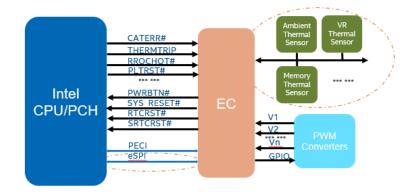

| Figure 8.  | Critical Signals Monitoring                        | 27 |

| Figure 9.  | System Thermal Monitoring                          | 29 |

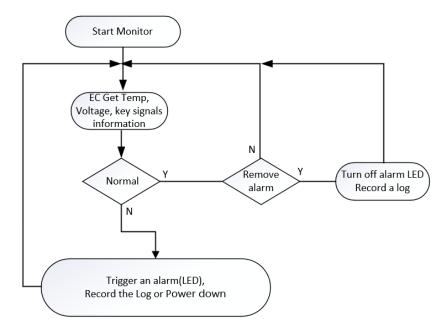

| Figure 10. | Monitoring Flow                                    | 30 |

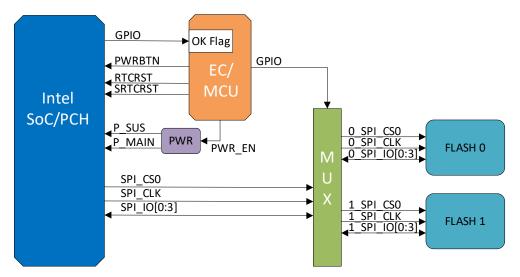

| Figure 11. | Hardware Architecture                              | 32 |

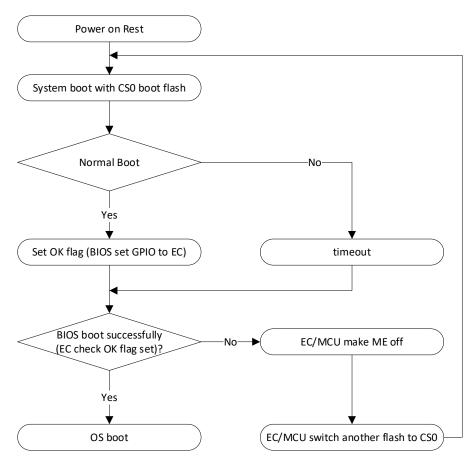

| Figure 12. | System Boot Flow                                   | 33 |

| Figure 13. | Reset Hardware Diagram                             | 35 |

| Figure 14. | Reset Working Flow                                 | 36 |

| Figure 15. | PMC_DSW_PWROK Requirement for Graceful Power Loss  | 38 |

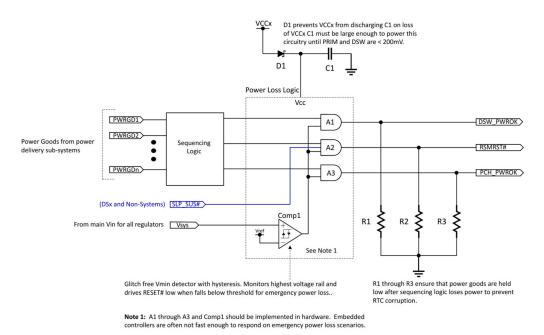

| Figure 16. | PMC_DSW_PWROK Requirement for Emergency Power Loss | 39 |

| Figure 17. | Emergency Power Loss - PWROK Requirement           | 40 |

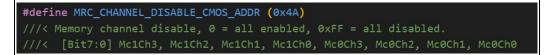

| Figure 18. | MRC CHANNEL DISABLE CMOS Defined Figure            | 43 |

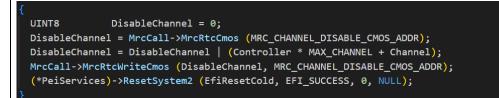

| Figure 19. | Record Failed MC/Channel to CMOS Figure            | 43 |

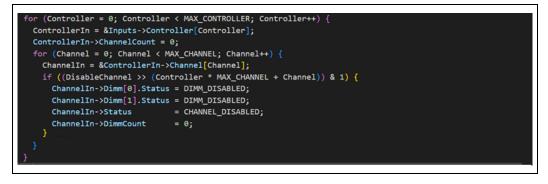

| Figure 20. | MRC Read Disabled Channel from CMOS Figure         | 43 |

| Figure 21. | MRC Skip the Channel Before MRC Training Figure    |    |

| Figure 22. | Memory Availability Workflow Figure                | 44 |

| Figure 23. | BIOS Region Layout Figure                          | 45 |

| Figure 24. | BIOS Recovery Workflow Figure                      | 47 |

| Figure 25. | OS Recovery Workflow Figure                        | 49 |

| Figure 26. | Intel KPMU Concept Overview                        | 50 |

| Figure 27. | KPMU1.5 HW Reference Design Block Diagram          | 51 |

| Figure 28. | KPMU2.0 HW Reference Design Block Diagram          |    |

| Figure 29. | Intel KPMU SW Architecture                         | 52 |

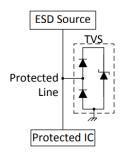

| Figure 30. | ESD Protection Concept                             |    |

| Figure 31. | PCB Materials Select Flow                          |    |

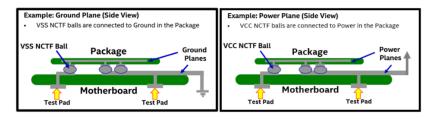

| Figure 32. | NCTF Solder Joint Connection Examples              |    |

| Figure 33. | NCTF Pins for TGL-UP3                              | 61 |

# Tables

| Table 1. | Terminologies                 | 8  |

|----------|-------------------------------|----|

| Table 2. | Reference Documents           |    |

| Table 3. | Reliability Standards         |    |

|          | Derating Level and Comparison |    |

| Table 5. | Derating Degree               | 23 |

| Table 6. | Derating Degree (cont.)       | 24 |

# **Revision History**

| Date          | Revision | Description      |

|---------------|----------|------------------|

| November 2023 | 1.0      | Initial release. |

§

# 1.0 Introduction

This document provides the general information and methods to design for reliability of electronic products to OEM/ODM partners, not cover like RAS (Reliability, Availability and Serviceability) features in Intel Xeon CPU. You may learn about What is Reliability, how is it Measured and How to design high reliability electronic products. Specifically, for below mentioned reliability items.

- Reliability index: failure rate, MTBF, MTTR and Availability

- Bathtub Curve

- Design for reliability Concept

- System Reliability Validation

- MTBF Prediction

- Component derating

- Power rails monitoring

- Critical signals monitoring

- Thermal monitoring

- Dual SPI BIOS flash

- RTC reset and Global reset

- Protection for surprise power down

- Memory reliability and availability

- BIOS recovery

- OS recovery

- USB recovery

- EMS and EMI

- Stack-up and PCB consideration

- Solder Joint Reliability

### **1.1** Terminologies

The following listed terminologies are used in the document.

#### Table 1. Terminologies

| Term                                             | Description |  |  |

|--------------------------------------------------|-------------|--|--|

| MTBF Mean Time Between Failures                  |             |  |  |

| MTTR Mean Time To Repair                         |             |  |  |

| HALT Highly Accelerated Life Testing             |             |  |  |

| DFR Design for Reliability                       |             |  |  |

| UART Universal Asynchronous Receiver/Transmitter |             |  |  |

| BIOS Basic Input Output System                   |             |  |  |

#### Introduction

| FileEnvectories of the systemECEmbedded controllerTMSDGThermal/Mechanical Specification and Design GuidePECIPlatform Environment Control InterfaceSPISerial Peripheral InterfaceMUXMultiplexerRTCReal Time ClockG3Global System State 3. RTC battery power only.GPIOGeneral Purpose Input/Output12CInter-Integrated CircuitVRVoltage RegulatorACAlternating CurrentDCDirect CurrentEoMEnd of ManufacturingTrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel* Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMSElectromagnetic CompatibilityEMSElectromagnetic CompatibilityEMSElectromagnetic CompatibilityEMSElectromagnetic Advantage ServiceTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNOr-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemSSDSolid State Disk               | MCU   | Microcontroller Unit                                   |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------|--|--|--|--|

| TMSDGThermal/Mechanical Specification and Design GuidePECIPlatform Environment Control InterfaceSPISerial Peripheral InterfaceMLManageability EngineMUXMultiplexerRTCReal Time ClockG3Global System State 3. RTC battery power only.GPIOGeneral Purpose Input/OutputI2CInter-Integrated CircuitVRVoltage RegulatorACAlternating CurrentDCDirect CurrentEoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel* Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMIElectromagnetic CompatibilityEMSElectromagnetic CompatibilityEMSElectromagnetic AlchargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File S                                 |       |                                                        |  |  |  |  |

| PECIPlatform Environment Control InterfaceSPISerial Peripheral InterfaceMEManageability EngineMUXMultiplexerRTCReal Time ClockG3Global System State 3. RTC battery power only.GPI0General Purpose Input/OutputI2CInter-Integrated CircuitVRVoltage RegulatorACAlternating CurrentDCDirect CurrentEoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-SKPMUIntel® Klosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMIElectromagnetic CompatibilityEMIElectromagnetic InterferenceESDElectromagnetic InterferenceESDElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayLGALand Grid ArrayLGALand Grid ArrayLGALand Grid ArrayIMSManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS Vendor <trr>FAT<!--</td--><td></td><td colspan="4"></td></trr> |       |                                                        |  |  |  |  |

| SPISerial Peripheral InterfaceMEManageability EngineMUXMultiplexerRTCReal Time ClockG3Global System State 3. RTC battery power only.GPIOGeneral Purpose Input/OutputI2CInter-Integrated CircuitVRVoltage RegulatorACAlternating CurrentDCDirect CurrentEoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-SAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMIElectromagnetic InterferenceESDElectromagnetic InterferenceESDElectromagnetic SusceptibilityEMABall Grid ArrayLGALand Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                    |       |                                                        |  |  |  |  |

| MEManageability EngineMUXMultiplexerRTCReal Time ClockG3Global System State 3. RTC battery power only.GPIOGeneral Purpose Input/OutputI2CInter-Integrated CircuitVRVoltage RegulatorACAlternating CurrentDCDirect CurrentEoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMIElectromagnetic SusceptibilityEMSElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayLGALand Grid ArrayLGALand Grid ArrayLGAManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                               |       |                                                        |  |  |  |  |

| MUXMultiplexerRTCReal Time ClockG3Global System State 3. RTC battery power only.GPIOGeneral Purpose Input/OutputI2CInter-Integrated CircuitVRVoltage RegulatorACAlternating CurrentDCDirect CurrentEoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMIElectromagnetic InterferenceESDElectromagnetic InterferenceESDElectromagnetic InterferenceESDElectromagnetic InterferenceESDElectromagnetic InterferenceESDElectromagnetic InterferenceESDElectromagnetic InterferenceESDElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation Table <td></td> <td></td>                     |       |                                                        |  |  |  |  |

| RTCReal Time ClockG3Global System State 3. RTC battery power only.GPIOGeneral Purpose Input/OutputI2CInter-Integrated CircuitVRVoltage RegulatorACAlternating CurrentDCDirect CurrentEoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMIElectromagnetic InterferenceESDElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                           |       |                                                        |  |  |  |  |

| GPIOGeneral Purpose Input/OutputI2CInter-Integrated CircuitVRVoltage RegulatorACAlternating CurrentDCDirect CurrentEoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-SAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMLElectromagnetic CompatibilityEMIElectromagnetic SusceptibilityEMIElectromagnetic GupressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                            | RTC   |                                                        |  |  |  |  |

| GPIOGeneral Purpose Input/OutputI2CInter-Integrated CircuitVRVoltage RegulatorACAlternating CurrentDCDirect CurrentEoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-SAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMLElectromagnetic CompatibilityEMIElectromagnetic SusceptibilityEMIElectromagnetic GupressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                            | G3    | Global System State 3. RTC battery power only.         |  |  |  |  |

| VRVoltage RegulatorACAlternating CurrentDCDirect CurrentEoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel* Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMLElectromagnetic CompatibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                       | GPIO  |                                                        |  |  |  |  |

| ACAlternating CurrentDCDirect CurrentEoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMIElectromagnetic SusceptibilityEMIElectronagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                       | 12C   | Inter-Integrated Circuit                               |  |  |  |  |

| DCDirect CurrentEoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                             | VR    | Voltage Regulator                                      |  |  |  |  |

| EoMEnd of ManufacturingTXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel* Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                             | AC    | Alternating Current                                    |  |  |  |  |

| TXETrusted Execution EngineIPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMSElectromagnetic SusceptibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                 | DC    | Direct Current                                         |  |  |  |  |

| IPIntellectual PropertyEHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMSElectromagnetic SusceptibilityEMSElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                              | EoM   | End of Manufacturing                                   |  |  |  |  |

| EHLElkhart LakeADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMSElectromagnetic SusceptibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayLGALand Grid ArraySJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TXE   | Trusted Execution Engine                               |  |  |  |  |

| ADL-NAlder Lake-NADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMSElectromagnetic SusceptibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                  | IP    | Intellectual Property                                  |  |  |  |  |

| ADL-SAlder Lake-SKPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMSElectromagnetic SusceptibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EHL   | Elkhart Lake                                           |  |  |  |  |

| KPMUIntel® Kiosk Peripheral Management UtilityHWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMSElectromagnetic SusceptibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ADL-N | Alder Lake-N                                           |  |  |  |  |

| HWHardwareSWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMSElectromagnetic SusceptibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ADL-S | Alder Lake-S                                           |  |  |  |  |

| SWSoftwareUSBUniversal Serial BusEMCElectromagnetic CompatibilityEMSElectromagnetic SusceptibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | KPMU  | Intel <sup>®</sup> Kiosk Peripheral Management Utility |  |  |  |  |

| USBUniversal Serial BusEMCElectromagnetic CompatibilityEMSElectromagnetic SusceptibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | HW    |                                                        |  |  |  |  |

| EMCElectromagnetic CompatibilityEMSElectromagnetic SusceptibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SW    | Software                                               |  |  |  |  |

| EMSElectromagnetic SusceptibilityEMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | USB   |                                                        |  |  |  |  |

| EMIElectromagnetic InterferenceESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EMC   | Electromagnetic Compatibility                          |  |  |  |  |

| ESDElectrostatic dischargeTVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                                                        |  |  |  |  |

| TVSTransient Voltage SuppressionPCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | Electromagnetic Interference                           |  |  |  |  |

| PCBPrint Cricut BoardBGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                                                        |  |  |  |  |

| BGABall Grid ArrayLGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                                                        |  |  |  |  |

| LGALand Grid ArrayMASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | Print Cricut Board                                     |  |  |  |  |

| MASManufacturing Advantage ServiceTMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                                                        |  |  |  |  |

| TMDGThermal Mechanical Design GuideNCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LGA   |                                                        |  |  |  |  |

| NCTFNon-Critical to FunctionSJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |                                                        |  |  |  |  |

| SJSolder JointMRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |                                                        |  |  |  |  |

| MRCMemory Reference CodeIBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |                                                        |  |  |  |  |

| IBVIndependence BIOS VendorFATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                                                        |  |  |  |  |

| FATFile Allocation TableNTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                                                        |  |  |  |  |

| NTFSNew Technology File SystemEXTExtended file systemSSDSolid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |                                                        |  |  |  |  |

| EXT     Extended file system       SSD     Solid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | File Allocation Table                                  |  |  |  |  |

| SSD Solid State Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                                                        |  |  |  |  |

| PEI Pre-EFI Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SSD   | Solid State Disk                                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PEI   | Pre-EFI Initialization                                 |  |  |  |  |

| UEFI | Unified Extensible Firmware Interface |

|------|---------------------------------------|

| POST | Power On Self Test                    |

### **1.2** Reference Documents

The reference documents is listed in the table below.

#### Table 2. Reference Documents

| Title and Link                                                                   | Location or ID |

|----------------------------------------------------------------------------------|----------------|

| Telcordia SR-332: 2016 Reliability Prediction Procedure for                      |                |

| Electronic Equipment                                                             |                |

| GJB/Z 35-93: Derating criteria for electrical, electronic and                    |                |

| electromechanical parts                                                          |                |

| MIL-HDBK-217F: Reliability prediction of electronic                              |                |

| equipment                                                                        |                |

| c3000 dual spi boot flash solution and poc wp                                    | 601001         |

| Elkhart Lake Platform Design Guide                                               | 599710         |

| Alder Lake N Platform Design Guide                                               | 646929         |

| Alder Lake S Platform Design Guide                                               | 619508         |

| Intel® Kiosk Peripheral Management (Intel® KPM) Utility -                        | 740544         |

| Overview                                                                         |                |

| Intel <sup>®</sup> Kiosk Peripheral Management Utility 2.0 Design Guide          | 735952         |

| (KPMU 2.0)                                                                       |                |

| Intel® Kiosk Peripheral Management Utility Version 1.5 Design<br>Guide           | 646176         |

| Alder Lake, Raptor Lake and Raptor Lake-S Refresh Platform                       | 619907         |

| Thermal and Mechanical Design Guide                                              |                |

| Manufacturing with the Intel <sup>®</sup> Desktop Processor Family for Socket V0 | 630369         |

| Including: Alder Lake-S, Raptor Lake-S, Raptor Lake-S                            |                |

| Refresh, and PCH                                                                 |                |

| Manufacturing with the Intel® Mobile Platform Code Named                         | 636157         |

| Alder Lake                                                                       |                |

| In-Band ECC (IBECC) for the Intel Atom® x6000E series, and                       | 621436         |

| Intel® Pentium® and Celeron® N and J Series Processors for                       |                |

| IoT Applications - Technical Advisory                                            |                |

**NOTE:** Other names and brands may be claimed as the property of others. Contact third party representatives for further support.

# 2.0 Overview

Why should a company commit resources for developing high reliability products? The answer is warranty costs and customer satisfaction. Field failures are very costly. Clearly, to be profitable, a company's products must be reliable, and reliable products require a formal reliability process.

The complexities of today's technologies make Design for reliability (DFR)more significant and valuable. Three main reasons include: 1) Product differentiation: As electronic technologies reach maturity, there are fewer opportunities to set products apart from the competition through traditional metrics - like price and performance. 2) Reliability assurance: Advanced circuitry, complicated power requirements, new components, new material technologies make ensuring reliability increasingly difficult.3) Reliability requirements of the customers and application scenarios, such as traffic and industrial control. Design for reliability ensures that products and systems perform a specified function within a given environment for an expected lifecycle.

## 2.1 Reliability Definition and Index

Definition of reliability is "The probability of a product performing without failure a specified function under given conditions for a specified period of time." Reliability has sometimes been classified as "how quality changes over time." The difference between quality and reliability is that quality shows how well an object performs its proper function, while reliability shows how well this object maintains its original level of quality over time, through various conditions.

### 2.1.1 Failure Rates

The failure rate is the number of failures in a component or piece of equipment over a specified period.

Failure Rate =  $\frac{\text{Number of Failures}}{\text{Time}}$

It is a calculated value that provides a measure of reliability for a product. This value is normally expressed as failures per million hours but can also be expressed as a FIT (failures in time) rate or failures per billion hours. For example, if a component has a failure rate of two failures per million hours, then it is anticipated that the component fails two times in a million-hour period.

• can be defined as the anticipated number of times that an item fails in a specified period.

- This value is normally expressed as failures per million hours, but it can also be expressed as a FIT (failures in time) rate or failures per billion hours.

- A component manufacturer may sometimes provide a specified failure rate usually based on field or laboratory test data.

### 2.1.2 MTBF

MTBF (Mean Time Between Failures) stands for the average time between two failures of the repairable system, that is the ratio of the cumulative system operation time to the number of failures. This metric is used to measure the stability and reliability of a product. The higher the time between failures, the more reliable the system.

The formula to calculate Mean Time Between Failures is as follows:

$\mathsf{MTBF} = \frac{\text{Total uptime}}{\text{Number of failures}}$

1. Total uptime – The total amount of time that the system or components were operating correctly under normal conditions. Usually measured in hours.

2. Number of failures – The total number of times that the equipment broke down unexpectedly.

Here's an example for MTBF. If you have 100 electronic devices. Over the past year, they have broken down a total of 10 times. So MTBF for this equipment is: MTBF=100x365x24 hours/10=87600 hours (about 10 years)

### 2.1.3 MTTR

Mean Time to Repair (MTTR) is an important failure metric that measures the time it takes to fix failed equipment or systems. By tracking MTTR, organizations can see how well they are responding to unplanned maintenance events and identify areas for improvement.

$MTTR = \frac{Total \ corrective \ maintenance \ time}{Number \ of \ repairs}$ Here's an example for MTTR.

Let's say you have a piece of electrical equipment. Over the past year, it has broken down a total of 5 times. The time that each repair took was (in hours), 1 hours, 0.5 hours, 2 hours, 0.5 hours, and 2 hours respectively, making a total maintenance time of 6 hours. So MTTR for this equipment is: MTTR=6 hours/5=1.2 hours

#### Assumptions

In calculating MTTR, the following is generally assumed.

Repairs are carried out by suitably trained technicians.

Technicians have access to the resources they need to complete the repairs.

#### 2.1.4 Availability

Availability is related to reliability and is a measure of how much time a system is performing correctly, when it needs to be. MTBF can be used with MTTR to calculate availability for a system.

Availability =  $\frac{\text{MTBF}}{\text{MTBF}+\text{MTTR}}$

Here's an example for MTTR. If you have a piece of electrical equipment. MTBF=50000hours (about 5 and a half years), MTTR=1hours.So, Availability for this equipment is: Availability =50000/ (50000+1) =0.99998

### 2.2 Bathtub Curve

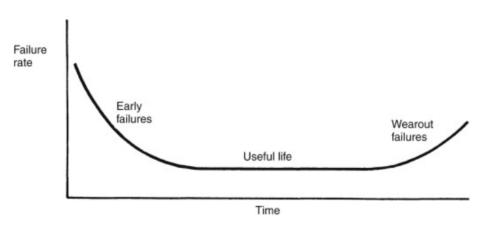

A bathtub curve visually shows the failure rate of a product by plotting their failure occurrences over time. It has three stages: early failures period, useful lifetime period, and wear-out period. The graph goes by the name of 'the bathtub curve' because of its characteristic shape. Note that the highest failure rates correspond to premature failure (early failures), and to end-of life wear out.

#### Figure 1. Bathtub Curve

#### • Early failure:

The first part of the curve describes early failures. At this stage a high number of failures is seen due to errors in design or manufacturing. The failure rate is decreasing, because the products which have defects and are therefore failing fast are removed

from the population. Early failure can be Reduced by strengthening quality management and environmental stress test.

#### • Useful life

The middle part of the curve describes the useful lifetime of a product. During this period the failure rate is constant. The failures seen are random failures, which can be caused for example due to random external stresses or mishandling of a product.

#### • Wear-out failures

The last part of the curve describes the wear out failures of a product. At this stage the failure rate is increasing, as the aging of components and materials is accelerating the occurrence of failures. At this stage the failures can be caused, for example due to corrosion, oxidation and so on.

The failure rate rule shown by the bathtub curve is not what the customers want. Therefore, it can be said that reliability work is to change the bathtub curve. In other words, the purpose of reliability work is to reduce early failures, extend Useful life and reduce failure rates. Through preventive monitoring and maintenance, ensure the failure rate at wear out period is reduced.

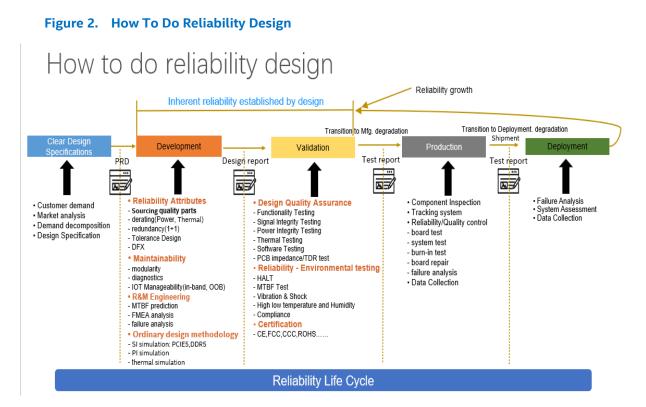

## 2.3 Design for Reliability Concept

The establishment of product reliability is system engineering. It is an actual process. Specifically, Design for Reliability (DFR) describes the entire set of tools that support product and process design (typically from early in the concept stage all the way through to product obsolescence) to ensure that customer expectations for reliability are fully met throughout the life of the product with low overall life-cycle costs. The life cycle of an electronic product is divided into five stages which include Define Design specification, Development, Validation, Production and Deployment. The inherent reliability of a product is established in design and validation stages. Some factors may be introduced into the production process to affect reliability. Therefore, the manufacturing process should ensure consistency as much as possible. Although we have done a lot to ensure the quality and reliability of the product is deployed in the actual working environment. Currently, we need to figure out the root cause. Then reflect and review the previous design and verify stages, and think about how to optimize the product, to further improve the reliability of the product.

#### Overview

#### Define Design Specification

The builder of product should clear and identify the customer demand in defining design specification stage. Maybe we need to do some market analysis and research. In short, a clear product specification is required in this phase.

#### Development

In the development of a product, it is important to ensure its reliability in the design stage, which enables the concept of reliability throughout the full life cycle of product design, operation, and maintenance. Some methods and measures should be adopted to ensure the reliability of products in the development phase. Common methods include derating design, redundancy design, tolerance design. MTBF prediction is also necessary in the design stage. With the progress of technology, the signal rate on the circuit board is faster and faster, such as PCIE5 and DDR5, to ensure signal integrity, some simulation work is necessary. Thermal factor is an important aspect that affects the reliability of the device, so the thermal design of the product is very important. The lower the device temperature, the better reliability of the device.

#### Validation

Validation is an important part in the product building process. Through test validation, we found some defects. Solving these defects and problems to ensure the reliability and quality of products. Validation tests usually include function test, signal integrity test, power integrity test, thermal test, software test, PCB TDR test and Compliance test. Some environmental stress validations are also necessary. For example, High or low

temperature and Humidity test, Vibration & Shock test, HALT (Highly Accelerated Life Testing) test, and so on.

#### Production

In the production and manufacturing process, it is critical to ensure the consistency of product delivery via a lot of test work. For example, board test, system test, burn-in test.

Generally, an electronic product has thousands of electronic components. To ensure the quality of these components, supply chain management is also very important.

#### Deployment

The actual deployment environment of the product is not equal to the lab test environment, so the product may still meet some problems in the deployment phase. We should collect data, analyze data, and then improve the previous design plan, test plan, and manufacturing plan to improve the reliability of products.

## 2.4 System Reliability Validation

As for Environmental adaptability, Environmental stress test and reliability validation, you could follow the standards below as a reference. Some test items are optional, not mandatory, such as MTBF identifying, HALT, Low air pressure test and so on. ODM/OEM can select the appropriate validation items according to the use condition of the products.

- The relevant standards of environmental stress are only a reference, not a basis/ judgement. You could spend some time understanding the test criterion.

- ODM/OEM could make a test plan for products, according to the use conditions of the products and standards listed pervious.

- Based on the experimental purpose, experimental principle, product characteristic and economy, consider the test stress.

- Selecting Environmental test items includes four aspects: test items choosing, test condition choosing, test procedure / step choosing and test sequence choosing.

For more validation information, please refer to 743956\_NEX\_IoT\_Customer\_Product\_Validation\_Handbook

|    | IEC/MIL                          | GB                       | Validation Items                              | Category    | Reference Notes                                                                                                                                                                                                      |

|----|----------------------------------|--------------------------|-----------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | IEC 60068-2-1                    | GB/T2423.1               | Low Temperature                               |             | Storage, Operating, Power up<br>Low Temperature-65~5°C;Duration 2/16/72/96h                                                                                                                                          |

| 2  | IEC 60068-2-2                    | GB/T2423.2               | High Temperature                              | Temperature | Storage, Operating, Power up<br>High Temperature:30~1000°C;Temperature change rate:3-5°C/min<br>Duration:2/16/72/96/168/240/1000h                                                                                    |

| 3  | IEC 60068-2-14<br>IEC 60068-2-78 | GB/T2423.22              | Thermal Cycling<br>Thermal Shock              |             | Temperature change rate 1-5°/min, Cycling times 2~10(maybe 1000 Cycling)<br>Shock: Temperature change rate 20-30°/min, Cycling times 5~10(1000 Cycling)                                                              |