# High Bandwidth Memory (HBM2) Interface Intel® FPGA IP User Guide

Updated for Intel® Quartus® Prime Design Suite: 20.1

IP Version: 19.4.0

UG-20031 | 2020.04.13 Latest document on the web: PDF | HTML

### **Contents**

| 1. Ab          | out the High Bandwidth Memory (HBM2) Interface Intel® FPGA IP                                                 | 4            |

|----------------|---------------------------------------------------------------------------------------------------------------|--------------|

|                | 1.1. Release Information                                                                                      | 4            |

| 2. Int         | troduction to High Bandwidth Memory                                                                           | 5            |

|                | 2.1. HBM2 in Intel Stratix 10 MX Devices                                                                      |              |

|                | 2.2. HBM2 DRAM Structure                                                                                      |              |

|                | 2.3. Intel Stratix 10 MX HBM2 Features                                                                        | _            |

|                | 2.4. Intel Stratix 10 MX HBM2 Controller Features                                                             | 7            |

| 3. Int         | tel Stratix 10 MX HBM2 Architecture                                                                           | 9            |

|                | 3.1. Intel Stratix 10 MX HBM2 Introduction                                                                    |              |

|                | 3.2. Intel Stratix 10 MX UIB Architecture                                                                     |              |

|                | 3.3. Intel Stratix 10 MX HBM2 Controller Architecture                                                         |              |

|                | 3.3.1. Intel Stratix 10 MX HBM2 Controller Details                                                            | . 13         |

| 4. Cre         | eating and Parameterizing the High Bandwidth Memory (HBM2) Interface Intel FPGA IP                            | . 17         |

|                | 4.1. Creating an Intel Quartus Prime Pro Edition Project for High Bandwidth Memory                            |              |

|                | (HBM2) Interface FPGA IP                                                                                      |              |

|                | 4.2. Parameterizing the High Bandwidth Memory (HBM2) Interface Intel FPGA IP                                  | .19          |

|                | FPGA IP                                                                                                       | . 19         |

|                | 4.2.2. Controller Parameters for High Bandwidth Memory (HBM2) Interface Intel FPGA IP                         |              |

|                | 4.2.3. Diagnostic Parameters for High Bandwidth Memory (HBM2) Interface Intel                                 |              |

|                | FPGA IP                                                                                                       | . 26         |

|                | 4.2.4. Example Designs Parameters for High Bandwidth Memory (HBM2)  Interface Intel FPGA IP                   | 20           |

|                | 4.3. Pin Planning for the High Bandwidth Memory (HBM2) Interface Intel FPGA IP                                | . 20<br>. 30 |

| F 6:-          | , , ,                                                                                                         |              |

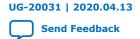

| <b>5. 5</b> 11 | mulating the High Bandwidth Memory (HBM2) Interface Intel FPGA IP                                             |              |

|                | 5.2. Simulating High Bandwidth Memory (HBM2) Interface Intel FPGA IP Example Design                           |              |

|                | ModelSim* and Questa*                                                                                         | 32           |

|                | 5.3. Simulating High Bandwidth Memory (HBM2) Interface Intel FPGA IP with Synopsys VCS*                       |              |

|                | 5.4. Simulating High Bandwidth Memory (HBM2) Interface Intel FPGA IP with Riviera-PRO*                        |              |

|                | 5.5. Simulating High Bandwidth Memory (HBM2) Interface Intel FPGA IP with Cadence NCSim*                      |              |

|                | 5.6. Simulating High Bandwidth Memory (HBM2) Interface Intel FPGA IP with Cadence Xcelium* Parallel Simulator |              |

|                | 5.7. Simulating High Bandwidth Memory (HBM2) Interface Intel FPGA IP for High Efficiency                      |              |

|                | 5.8. Simulating High Bandwidth Memory (HBM2) Interface IP Instantiated in Your Project                        |              |

| 6. Hid         | gh Bandwidth Memory (HBM2) Interface Intel FPGA IP Interface                                                  | . 37         |

|                | 6.1. High Bandwidth Memory (HBM2) Interface Intel FPGA IP High Level Block Diagram                            |              |

|                | 6.2. High Bandwidth Memory (HBM2) Interface Intel FPGA IP Controller Interface Signals                        |              |

|                | 6.2.1. Clock Signals                                                                                          | 38           |

### Contents

|      | 6.2.2. Reset Signals                                                              | 40 |

|------|-----------------------------------------------------------------------------------|----|

|      | 6.2.3. Calibration Status Signals                                                 | 42 |

|      | 6.2.4. Memory Interface Signals                                                   | 42 |

|      | 6.2.5. AXI User-interface Signals                                                 | 43 |

|      | 6.2.6. Sideband APB Interface                                                     | 49 |

|      | 6.3. User AXI Interface Timing                                                    | 50 |

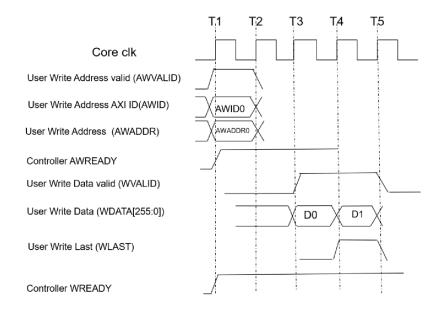

|      | 6.3.1. AXI Write Transaction                                                      | 52 |

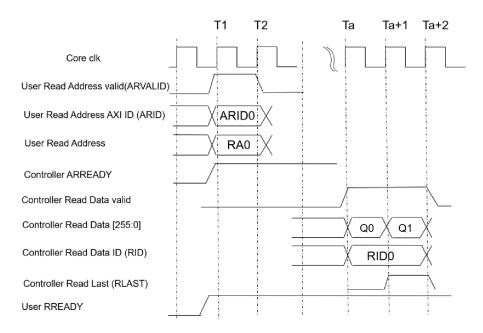

|      | 6.3.2. AXI Read Transaction                                                       | 53 |

|      | 6.3.3. Non-zero Latency Backpressure                                              | 54 |

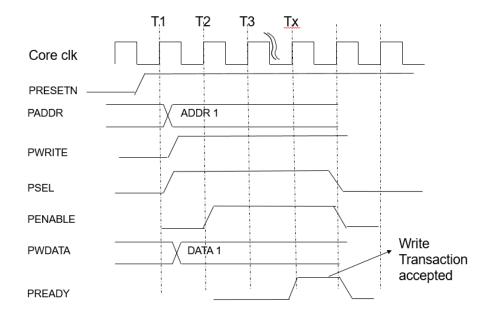

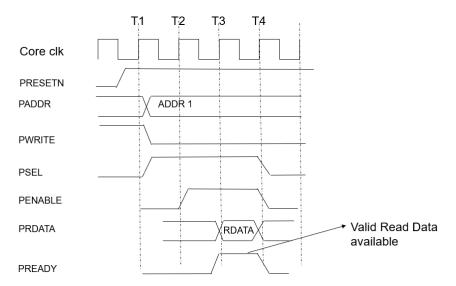

|      | 6.4. User APB Interface Timing                                                    |    |

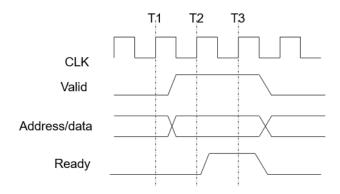

|      | 6.4.1. Advanced Peripheral Bus Protocol                                           | 56 |

|      | 6.4.2. APB Interface Timing                                                       | 57 |

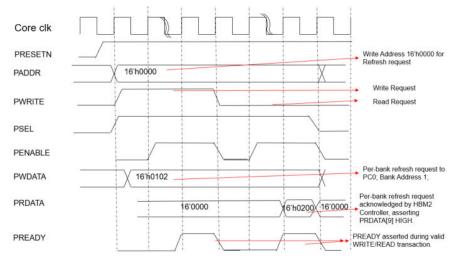

|      | 6.5. User-controlled Accesses to the HBM2 Controller                              | 58 |

|      | 6.5.1. User-controlled Refreshes                                                  |    |

|      | 6.5.2. Temperature and Calibration Status Readout                                 | 63 |

|      | 6.5.3. Power Down Status                                                          | 64 |

|      | 6.5.4. ECC Error Status                                                           | 64 |

|      | 6.5.5. User Interrupt                                                             |    |

|      | 6.5.6. ECC Error Correction and Detection                                         |    |

|      | 6.6. Soft AXI Switch                                                              |    |

|      | 6.6.1. AXI Switch Selection in HBM2 IP Catalog GUI                                | 71 |

| 7. I | High Bandwidth Memory (HBM2) Interface Intel FPGA IP Controller Performance       | 76 |

|      | 7.1. High Bandwidth Memory (HBM2) DRAM Bandwidth                                  |    |

|      | 7.2. High Bandwidth Memory (HBM2) Interface Intel FPGA IP HBM2 IP Efficiency      |    |

|      | 7.3. High Bandwidth Memory (HBM2) Interface Intel FPGA IP Latency                 |    |

|      | 7.4. High Bandwidth Memory (HBM2) Interface Intel FPGA IP Timing                  |    |

|      | 7.5. High Bandwidth Memory (HBM2) Interface Intel FPGA IP DRAM Temperature Readou |    |

| R. I | High Bandwidth Memory (HBM2) Interface Intel FPGA IP User Guide Archives          |    |

|      |                                                                                   | 00 |

| 9. I | Document Revision History for High Bandwidth Memory (HBM2) Interface Intel        |    |

|      | FPGA IP User Guide                                                                | 81 |

### 1. About the High Bandwidth Memory (HBM2) Interface Intel® FPGA IP

### 1.1. Release Information

IP versions are the same as the Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Suite software versions up to v19.1. From Intel Quartus Prime Design Suite software version 19.2 or later, IP cores have a new IP versioning scheme.

The IP versioning scheme (X.Y.Z) number changes from one software version to another. A change in:

- X indicates a major revision of the IP. If you update your Intel Quartus Prime software, you must regenerate the IP.

- Y indicates the IP includes new features. Regenerate your IP to include these new features.

- Z indicates the IP includes minor changes. Regenerate your IP to include these changes.

### Table 1. High Bandwidth Memory (HBM2) Interface Intel FPGA IP Core Current Release Information

| Item                        | Description |

|-----------------------------|-------------|

| IP Version                  | 19.4.0      |

| Intel Quartus Prime Version | 20.1        |

| Release Date                | 2020.04.13  |

### 2. Introduction to High Bandwidth Memory

High Bandwidth Memory (HBM) is a JEDEC specification (JESD-235) for a wide, high bandwidth memory device. The next generation of High Bandwidth Memory, HBM2, is defined in JEDEC specification JESD-235A. The HBM2 implementation in Intel Stratix® 10 MX devices complies with JESD-235A.

The High Bandwidth Memory DRAM is tightly coupled to the host die with a distributed interface. The interface is divided into independent channels, each completely independent of one another. Each channel interface maintains a 128-bit data bus, operating at DDR data rates.

### 2.1. HBM2 in Intel Stratix 10 MX Devices

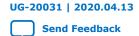

Intel Stratix 10 MX incorporates a high-performance FPGA fabric along with a HBM2 DRAM in a single package. Intel Stratix 10 MX devices support up to a maximum of two HBM2 interfaces.

Intel Stratix 10 MX incorporates Intel's Embedded Multi-Die Interconnect Bridge (EMIB) technology to implement a silicon bridge between HBM2 DRAM memory and the Universal Interface Block Subsystem (UIBSS), which contains the HBM2 controller (HBMC), physical-layer interface (PHY), and I/O ports to interface to the HBM2 stack.

As illustrated below, each Intel Stratix 10 MX device contains a single universal interface bus per HBM2 interface, supporting 8 independent channels.

The user interface to the HBM2 controller is maintained through the AXI4 protocol. Sixteen AXI interfaces are available in the user interface from each HBM2 controller, with one AXI interface available per HBM2 Pseudo Channel. HBM2 DRAM density of 4GB and 8GB are supported.

Figure 1. Intel Stratix 10 MX Device with UIB, EMIB, and HBM2 DRAM

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

### 2.2. HBM2 DRAM Structure

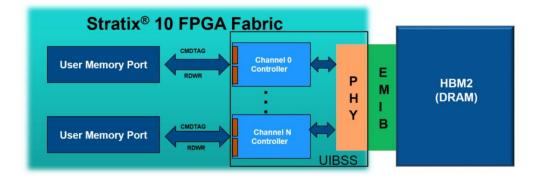

The HBM DRAM is optimized for high-bandwidth operation to a stack of multiple DRAM devices across several independent interfaces called channels. Each DRAM stack supports up to eight channels.

The following figure shows an example stack containing four DRAM dies, each die supporting two channels. Each die contributes additional capacity and additional channels to the stack, up to a maximum of eight channels per stack. Each channel provides access to an independent set of DRAM banks. Requests from one channel may not access data attached to a different channel.

Figure 2. High Bandwidth Memory Stack of Four DRAM Dies

### 2.3. Intel Stratix 10 MX HBM2 Features

Intel Stratix 10 MX FPGAs offer the following HBM2 features.

- Supports one to eight HBM2 channels per HBM2 interface in the Pseudo Channel mode.

- Each HBM2 channel supports a 128-bit DDR data bus, with optional ECC support.

- Pseudo Channel mode divides each channel into two individual 64-bit I/O pseudo-channels. The two pseudo-channels operate semi-independently; they share the channel's row and column command bus as well as CK and CKE inputs, but they decode and execute commands individually. Address BA4 directs commands to either pseudo-channel 0 (BA4 = 0) or pseudo-channel 1 (BA4 = 1), offering unique address space to each pseudo-channel. Pseudo Channel mode requires that the burst length for DRAM transactions is set to 4.

- Data referenced to strobes RDQS\_t / RDQS\_c and WDQS\_t / WDQS\_c, one strobe pair per 32 DQs.

UG-20031 | 2020.04.13

- Differential clock inputs (CK\_t / CK\_c). Unterminated data/address/cmd/clk interfaces.

- DDR commands entered on each positive CK\_t and CK\_c edge. Row Activate commands require two memory cycles; all other command are single-cycle commands.

- Supports command, write data and read data parity.

- Support for bank grouping.

- Support for data bus inversion.

- 64-bit data per pseudo-channel. Eight additional data bits are available per pseudo-channel; you can use these data bits for any of the following:

- ECC. The ECC scheme implemented is single-bit error correction with double-bit error detection (SECDEC). This includes 8 bits of ECC code (also known as syndrome).

- Data mask (DM). The data mask for masking write data per byte.

- Can be left unused.

- I/O voltage of 1.2V and DRAM core voltage of 1.2V.

### 2.4. Intel Stratix 10 MX HBM2 Controller Features

Intel Stratix 10 MX FPGAs offer the following controller features.

- User applications communicate with the HBMC using the AXI4 Protocol.

- There is one AXI4 interface per HBM2 Pseudo Channel. Each HBM2 interface supports a maximum of sixteen AXI4 interfaces to the sixteen Pseudo Channels.

- The user interface can operate at a frequency lower than the HBM2 interface frequency. The maximum supported HBM2 interface frequency depends on the FPGA device speed grade. The minimum frequency of the core clock is one quarter of the HBM2 interface frequency.

- Each AXI interface supports a 256-bit Write Data interface and a 256-bit Read Data interface.

- The controller offers 32B and 64B access granularity supporting burst length 4 (BL 4) and pseudo-BL 8 (two back to back BL4).

- The controller offers out-of-order command scheduling and read data reordering.

- The controller supports user-initiated Refresh commands, and access to the HBM2 channel status registers, through the side band Advanced Peripheral Bus (APB) interface.

- The controller supports data mask or error correction code (ECC). When you do not use data mask or ECC, you may use those bits as additional data bits.

### **Related Information**

Clock Signals on page 38

### 3. Intel Stratix 10 MX HBM2 Architecture

This chapter provides an overview of the Intel Stratix 10 MX HBM2 architecture.

### 3.1. Intel Stratix 10 MX HBM2 Introduction

Intel Stratix 10 MX devices use the Intel EMIB technology to interface to the HBM2 memory devices.

- The Intel Stratix 10 MX FPGAs offer up to two HBM2 interfaces.

- Each HBM2 device can have a device density of 4GB or 8GB, based on the FPGA chosen.

This system-in-package solution helps to achieve maximum bandwidth and low power consumption in a small footprint.

### 3.2. Intel Stratix 10 MX UIB Architecture

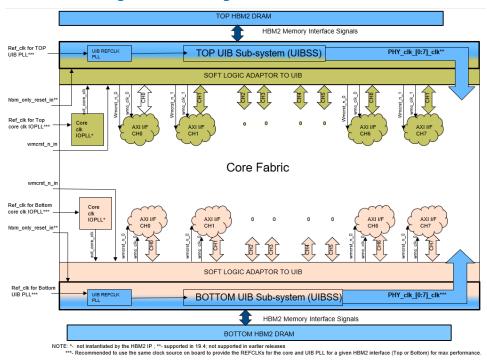

The Intel Stratix 10 MX device architecture includes the universal interface bus (UIB) subsystem (UIBSS) which contains the necessary logic to interface the FPGA core to the HBM2 DRAM.

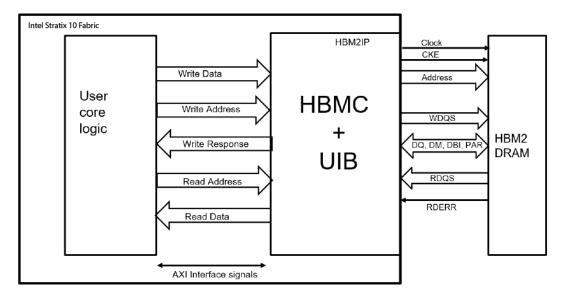

Each UIB subsystem includes the HBM2 hardened controller and the universal interface bus, consisting of the hardened physical interface and I/O logic needed to interface to each HBM2 DRAM device. The AMBA AXI4 protocol interfaces the core logic with the universal interface bus subsystem. An optional soft logic adapter implemented in the FPGA fabric helps to efficiently interface user logic to the hardened HBM2 controller.

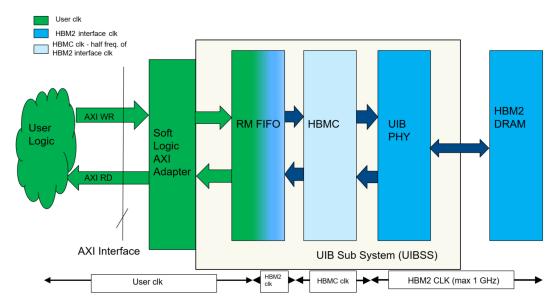

The following figure shows a high-level block diagram of the Intel Stratix 10 HBM2 universal interface bus subsystem. The UIB subsystem includes the following hardened logic:

- Rate-matching FIFOs that transfer logic from the user core clock to the HBM2 clock domain.

- HBM2 memory controller (HBMC).

- UIB PHY, including the UIB physical layer and I/O.

Figure 3. Block Diagram of Intel Stratix 10 MX HBM2 Implementation

The user core clock drives the logic highlighted in green, while the UIB clocks the logic highlighted in blue. The UIB clock also drives the HBM2 interface clock. User logic can run up to one-to-four times slower than the HBM2 interface.

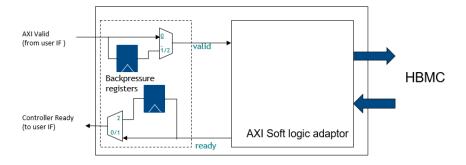

#### **Soft Logic AXI Adaptor**

The HBM2 IP also includes a soft logic adaptor implemented in FPGA core logic. The soft logic adaptor gates the user valid signals (write address valid, write data valid, and read address valid) with the corresponding pipelined ready signals from the HBM2 controller. The soft logic adapter also temporarily stores output from the HBM2 controller (AXI write response and AXI read data channels) when the AXI ready signal is absent. You can disable the temporary storage logic if user logic is always ready to accept output from the HBM2 controller through the parameter editor when generating the HBM2 IP.

### **HBM2 DRAM**

The following table lists the HBM2 signals that interface to the UIB. The UIB drives the HBM2 signals and decodes the received data from the HBM2. These signals cannot be accessed through the AXI4 User Interface.

**Table 2.** Summary of Per-channel Signals

| Signal Name            | Signal Width | Notes                                                               |

|------------------------|--------------|---------------------------------------------------------------------|

| Data                   | 128          | 128 bit bidirectional DQ per channel                                |

| Column command/address | 8            | 8-bit wide column address bits                                      |

| Row command/address    | 6            | 6-bit wide row address bits                                         |

| DBI                    | 16           | 1 DBI per 8 DQs                                                     |

| DM_CB                  | 16           | 1 DM per 8 DQs. You can use these pins for DM or ECC, but not both. |

| continued              |              |                                                                     |

| Signal Name | Signal Width | Notes                                                                                             |

|-------------|--------------|---------------------------------------------------------------------------------------------------|

| PAR         | 4            | 1 parity bit per 32 DQs                                                                           |

| DERR        | 4            | 1 data error bit per 32 DQs                                                                       |

| Strobes     | 16           | Separate strobes for read and write strobes. One differential pair per 32 DQs for read and write. |

| Clock       | 2            | Clocks address and command signals                                                                |

| CKE         | 1            | Clock enable                                                                                      |

| AERR        | 1            | Address error                                                                                     |

The following table lists the HBM2 signals that are common to all Pseudo Channels in each HBM2 interface. The HBM2 controller interfaces with the following signals; these signals are not available at the AXI4 user interface.

Table 3. Summary of Global HBM2 Signals

| Signal Name | Signal Width | Notes                            |

|-------------|--------------|----------------------------------|

| Reset       | 1            | Reset input                      |

| TEMP        | 3            | Temperature output from HBM2.    |

| Cattrip     | 1            | Catastrophic temperature sensor. |

The Intel Stratix 10 MX HBM2 IP supports only the Pseudo Channel mode of the HBM2 specification. Pseudo Channel mode includes the following features:

- Pseudo Channel mode divides a single HBM2 channel into two individual subchannels of 64 bit I/O.

- Both Pseudo Channels share the channel's row and column command bus, CK, and CKE inputs, but decode and execute commands individually.

- Pseudo Channel mode requires a burst length of 4.

- Address BA4 directs commands to either Pseudo Channel 0 (BA4 = 0) or Pseudo Channel 1 (BA4 = 1). The HBM2 controller handles the addressing requirements of the Pseudo Channels.

- Power-down and self-refresh are common to both Pseudo Channels, due to a shared CKE pin. Both Pseudo Channels also share the channel's mode registers.

#### **User AXI Interface**

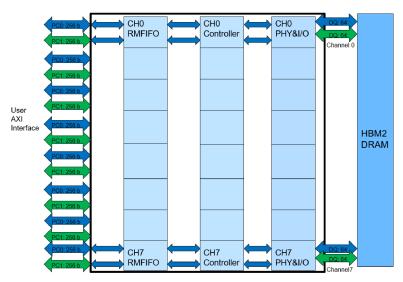

Each Intel Stratix 10 MX HBM2 interface supports a maximum of eight HBM2 channels. Each HBM2 channel has two AXI4 interfaces, one per Pseudo Channel. Each AXI4 interface includes a 256-bit wide Write and Read Data interface per Pseudo Channel. The following figure shows the flow of data from user logic to the HBM2 DRAM through the UIBSS, while selecting HBM2 channels 0 and 7.

Figure 4. Intel Stratix 10 MX HBM2 Interface Using HBM2 Channels 0 and 7 through the UIBSS

There is one AXI interface per Pseudo Channel. Each AXI interface supports a 256-bit wide Write Data interface and a 256-bit wide Read Data interface, to and from the HBM2 controller. The AXI4 protocol can handle concurrent writes and reads to the HBM2 controller. There is also a sideband user port per user channel pair, compliant to the Advanced Peripheral Bus (APB). The sideband provides access to user-controlled features such as refresh requests, ECC status, Power Down status, HBM2 temperature readout, calibration status, and User Interrupt.

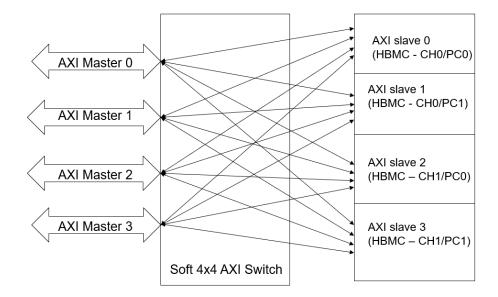

Beginning with the Intel Quartus Prime software version 20.1, the HBM2 IP supports a soft 4x4 AXI switch that provides each AXI master the ability to access the memory space of its corresponding two HBM2 Channels or four HBM2 Pseudo Channels (one HBM2 Channel = two HBM2 Pseudo Channels) in the HBM2 DRAM. For more details on the AXI switch, refer to Soft AXI Switch.

For information on the AXI protocol features supported by the Intel Stratix 10 HBM2 controller, refer to *High Bandwidth Memory (HBM2) Interface Intel FPGA IP Interface*.

#### **Related Information**

- Intel Stratix 10 MX HBM2 Controller Details on page 13

- High Bandwidth Memory (HBM2) Interface Intel FPGA IP Interface on page 37

### 3.3. Intel Stratix 10 MX HBM2 Controller Architecture

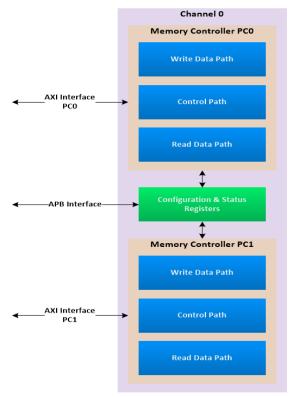

The hardened HBM2 controller provides a controller per Pseudo Channel.

Each controller consists of a write and read data path and the control logic that helps to translate user commands to the HBM2 memory. The HBM2 controller logic accounts for the HBM2 memory specification timing and schedules commands in an efficient manner. The following figure shows a block diagram of the HBM2 controller,

corresponding to channel 0. The HBM2 controller's user-logic interface follows the AXI4 protocol. You can find more information about the interface timing details in the *User AXI Interface Timing* section.

Figure 5. Intel Stratix 10 MX HBM2 Controller Block Diagram

#### 3.3.1. Intel Stratix 10 MX HBM2 Controller Details

This topic explains some of the high level HBM2 controller features.

#### **HBM2** burst transactions

The HBM2 controller supports only the Pseudo Channel mode of accessing the HBM2 device; consequently, it can only support BL4 transactions to the DRAM. For improving efficiency, it supports the pseudo-BL8 mode, which helps to provide two back-to-back BL4 data using a given start address, similar to a BL8 transaction.

Each BL4 transaction corresponds to 4\*64 bits or 32 bytes and a BL8 transaction corresponds to 64 bytes per Pseudo Channel. You can select the burst transaction mode (32 B vs 64B) through the parameter editor.

The user logic can interface to a maximum of 16 Pseudo Channels (16 AXI ports) per HBM2 interface. Each AXI port has a separate write and read interface, and can handle write and read requests concurrently at the same clock. Each write and read data interface per AXI port is 256 bits wide; that is, each AXI Write or Read Data transaction corresponds to data transfers corresponding to two HBM2 memory clock cycles.

#### **User interface vs HBM2 Interface Frequency**

The user interface runs at a frequency lower than the HBM2 interface; the maximum interface frequency depends on the chosen device speed grade and the FPGA core logic frequency. The rate-matching FIFOs within the UIB subsystem handle the data transfer between the two clock domains.

### **Command Priority**

You can set command priority for a write or read command request through the AXI interface, through the qos signal in the AXI write address channel, or in the AXI read address channel. The HBM2 controller supports normal and high priority levels. The system executes commands with the same priority level in a round-robin scheme.

#### Starvation limit

The controller tracks how long each command waits and leaves no command unserviced in the command queue for a long period of time. The controller ensures that it serves every command efficiently.

### **Command scheduling**

The HBM2 controller schedules the incoming commands to achieve maximum efficiency at the HBM2 interface. The HBM2 controller also follows the AXI ordering model of the AXI4 protocol specification.

#### Data re-ordering

The controller can reorder read data to match the order of the read requests.

### **Address ordering**

The HBM2 controller supports different address ordering schemes that you can select for best efficiency given your use case. The chosen addressing scheme determines the order of address configurations in the AXI write and read address buses, including row address, column address, bank address, and stack ID (applicable only to the 8H devices). The HBM2 controller remaps the logical address of the command to physical memory address.

#### **Thermal Control**

The HBM2 controller uses the TEMP and CATTRIP outputs from the HBM2 device to manage temperature variations in the HBM2 interface.

- Temperature compensated refresh (TEMP): The HBM2 DRAM provides temperature compensated refresh information to the controller through the TEMP[2:0] pins, which defines the proper refresh rate that the DRAM expects to maintain data integrity. Absolute temperature values for each encoding are vendor-specific. The encoding on the TEMP[2:0] pins reflects the required refresh rate for the hottest device in the stack. The TEMP data updates when the temperature exceeds vendor-specified threshold levels appropriate for each refresh rate.

- Catastrophic temperature sensor (CATTRIP): The CATTRIP sensor detects whether

the junction temperature of any die in the stack exceeds the catastrophic trip

threshold value CATTEMP. The device vendor programs the CATTEMP to a value

less than the temperature at which permanent damage to the HBM stack would

occur. The CATTEMP value is also the Absolute Max Junction temperature value as

specified in the Intel Stratix 10 data sheet for the family of devices that include

the HBM2 DRAM. You can find the Intel Stratix 10 data sheet at the following

location: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/

literature/hb/stratix-10/s10 datasheet.pdf.

If a junction temperature anywhere in the stack exceeds the CATTEMP value, the HBM stack drives the external CATTRIP pin to 1, indicating that catastrophic damage may occur. When the CATTRIP pin is at 1, the controller stops all traffic to HBM and stalls indefinitely. To resolve the overheating situation and return the CATTRIP value to 0, remove power from the device and allow sufficient time for the device to cool before again applying power.

• Thermal throttling: Thermal throttling is a controller safety feature that helps control thermal runaway if the HBM2 die overheats, preventing a catastrophic failure. You can specify the HBM2 device junction temperature at which the controller begins to throttle input commands, and the throttle ratio that determines the throttle frequency. The controller deasserts the AXI ready signals (awready, wready and arready) when it is actively throttling the input commands and data.

### **Refresh requests**

The HBM2 controller handles HBM2 memory refresh requirements and issues refresh requests at the optimal time, as specified by the JEDEC specification of the HBM2 DRAM. The controller automatically controls refresh rates based on the temperature setting of the memory through the TEMP vector that the memory provides. You can select the HBM2 controller refresh policy, based on the frequency of refresh requests. You can choose to issue refresh commands directly, through the sideband APB interface.

#### **Precharge policy**

The HBM2 controller issues precharge commands to the HBM2 memory based on the write/read transaction address. In addition, you can issue an auto-precharge command together with a write and read command, through the AXI write address port and AXI read address port.

There are two auto-precharge modes:

- HINT You can issue the auto-precharge request. The controller then decides when to issue the precharge command.

- FORCED You provide auto-precharge requests through the AXI interface and the precharge request executes.

#### Power down enable

To conserve power, the HBM2 controller can enter power-down mode when the bus is idle for a long time. You can select this option if required.

#### **ECC**

The HBM2 controller supports ECC. The ECC scheme implemented is single-bit error correction with double-bit error detection, with 64-bits of data and 8-bits of ECC code (also known as the syndrome).

### **HBM2** Controller features enabled by default

The HBM2 controller enables the following features by default:

- DBI The DBI option supports both write and read DBI, and optimizes SI/power consumption by restricting signal switching on the HBM2 DQ bus.

- Parity Supports command/address parity and DQ parity.

#### **Related Information**

- Clock Signals on page 38

- Intel Stratix 10 MX UIB Architecture on page 9

# 4. Creating and Parameterizing the High Bandwidth Memory (HBM2) Interface Intel FPGA IP

This chapter contains information on project creation, IP parameter descriptions, and pin planning for your High Bandwidth Memory (HBM2) Interface Intel FPGA IP.

### 4.1. Creating an Intel Quartus Prime Pro Edition Project for High Bandwidth Memory (HBM2) Interface FPGA IP

You can parameterize and generate the High Bandwidth Memory (HBM2) Interface Intel FPGA IP using the Intel Quartus Prime Pro Edition software.

- 1. Before generating the HBM2 IP, you must create a new project:

- a. Launch the Intel Quartus Prime Pro Edition software.

- b. Launch the New Project Wizard by clicking **File** ➤ **New Project Wizard**.

- Type a name for your project in the **Directory, Name, Top-Level Entity** field.

- d. In the **Project Type** section, select **Empty Project**.

- e. In the **Add Files** section, click **Next**.

- f. In the Family, Device, and Board Settings section, select Stratix 10 MX as the device family.

- g. Under Available Devices, select any MX device and your desired speed grade.

- h. Click **Next** and follow the Wizard's prompts to finish creating the project.

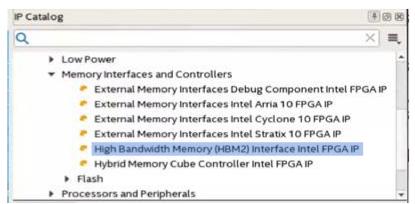

- 2. In the IP Catalog, open Library ➤ Memory Interfaces and Controllers.

- Launch the parameter editor by selecting High Bandwidth Memory (HBM2)

Interface Intel FPGA IP.

### Figure 6. Selecting High Bandwidth Memory (HBM2) Interface Intel FPGA IP in the IP Catalog

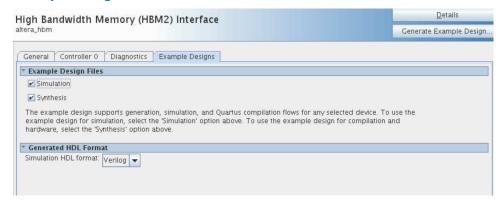

### 4.2. Parameterizing the High Bandwidth Memory (HBM2) Interface Intel FPGA IP

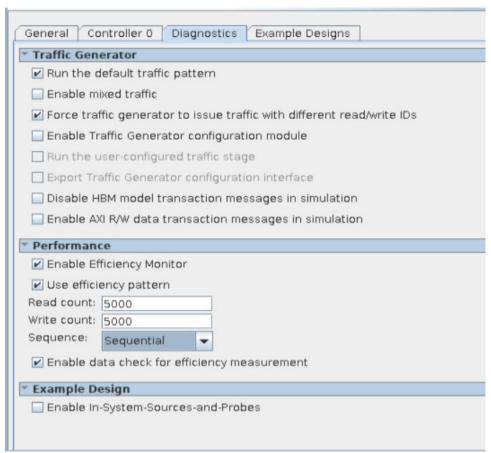

You can parameterize your HBM2 IP with the HBM2 IP parameter editor.

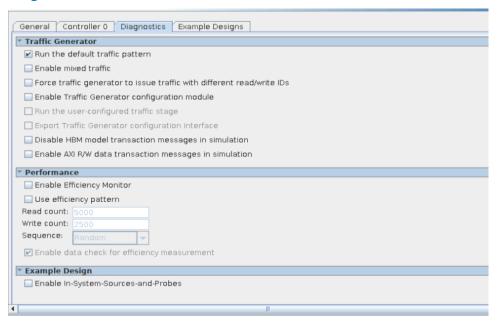

The parameter editor comprises the following tabs, on which you set the parameters for your IP:

- General

- Controller

- Diagnostics

- Example Designs

### 4.2.1. General Parameters for High Bandwidth Memory (HBM2) Interface Intel FPGA IP

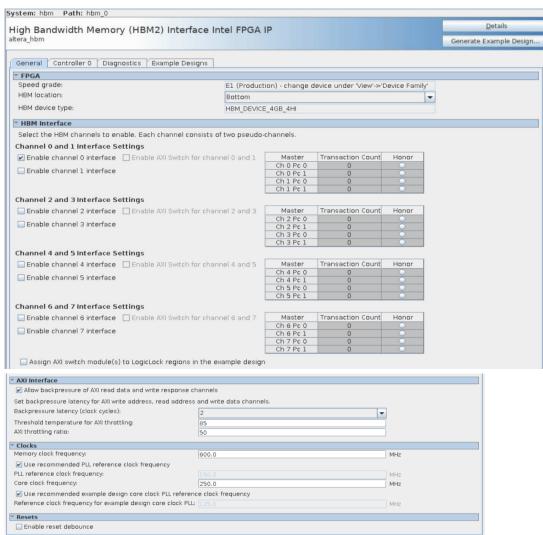

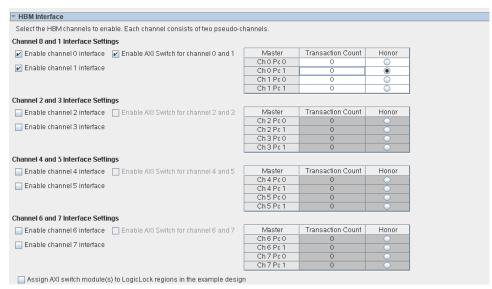

The **General** tab allows you to select the channels that you want to implement, and to select the memory and fabric core clock frequency.

### Figure 7. General Tab

### Table 4. Group: General / FPGA

| Display Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Speed Grade  | Speed grade of FPGA device and whether it is an engineering sample (ES) or a production device. The value is automatically determined based on the device selected under View > Device Family. If you do not specify a device, the system assumes a production device of the fastest speed grade. You should always specify the correct target device during IP generation; failure to specify the correct device may result in generated IP that does not work on hardware. |

|              | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### 4. Creating and Parameterizing the High Bandwidth Memory (HBM2) Interface Intel FPGA IP UG-20031 | 2020.04.13

| Display Name     | Description                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Specifies the speed grade of the Intel Stratix 10 FPGA.                                                                                                                            |

| HBM2 Location    | Determines the location of the HBM2 interface in the Intel Stratix 10 FPGA. The FPGA offers HBM2 interfaces on the top and bottom of the FPGA core.                                |

| HBM2 Device Type | The HBM device type. 4GB/4H refers to HBM2 device with a total device density of 4GB in a 4-high Stack, and 8GB8H refers to a total HBM2 device density of 8GB in an 8-high Stack. |

### Table 5. Group: General / HBM2 Interface

| Display Name                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel 0 and 1 Interface Settings (Applies to HBM2 Channels 2 and 3, 4 and 5, 6 and 7) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Enable Channel 0 interface                                                              | Adds a High Bandwidth Memory controller on channel 0 of the Universal Interface Block. Each controller handles two HBM Pseudo Channels. You can select the HBM2 memory channels that you want to implement. Each HBM2 channel supports a 128-bit interface to the HBM2 device, using two 64-bit Pseudo Channels. The user interface to the HBM2 controller uses the AXI4 protocol. Each controller has one AXI4 interface per Pseudo Channel or two AXI4 interfaces per channel.                                                                           |

| Enable Channel 1 interface                                                              | Adds a High Bandwidth Memory controller on channel 1 of the Universal Interface Block. Each controller handles two HBM Pseudo Channels. You can select the HBM2 memory channels that you want to implement. Each HBM2 channel supports a 128-bit interface to the HBM2 device, using two 64-bit Pseudo Channels. The user interface to the HBM2 controller uses the AXI4 protocol. Each controller has one AXI4 interface per Pseudo Channel or two AXI4 interfaces per channel.                                                                           |

| Enable AXI Switch for channel 0 and 1                                                   | Adds soft AXI switch logic that enables each AXI master to access the entire memory space of Channels 0 and 1 in HBM2 DRAM. Refer to Soft AXI Switch for information on using the AXI switch.  Note: You must enable two HBM2 channels to access the                                                                                                                                                                                                                                                                                                       |

|                                                                                         | corresponding 4x4 AXI switch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Master                                                                                  | Enables selection of arbitration schemes to provide efficient memory access for each AXI master.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Transaction Count                                                                       | Provide the total transaction count that the master intends to issue when provided access. Each transaction count refers to a single BL4 or pseudo-BL8 transaction. The total transaction count includes transaction counts to all the Pseudo Channels that the master intends to issue when provided access. The default value is 0. The HBM2 IP can support a maximum of 65535 transactions. Be aware that high transaction counts can reduce fabric performance. Refer to AXI Switch Selection in HBM2 IP Catalog for information on transaction count. |

| Honor                                                                                   | Select the master that requires higher priority over other masters. You can choose only one master; if you do not choose a master, all masters receive the same priority and round robin arbitration is followed.                                                                                                                                                                                                                                                                                                                                          |

| Assign AXI switch module(s) to Logic Lockregions in the example design                  | Provides Logic Lock regions for the AXI switch as reference for the design example. You can use this and provide the Logic Lock constraints to improve timing closure in actual design.                                                                                                                                                                                                                                                                                                                                                                    |

### **Table 6.** Group: General / AXI Interface

| Display Name                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Allow backpressure of AXI read data and write response channels | Instantiates FIFOs in soft logic to buffer read data and write response on the AXI interfaces. This is required if the RREADY/BREADY signals are ever deasserted. You can disable this option to reduce latency but only if RREADY/BREADY are never used to backpressure the interface.                                                                                                                                                       |

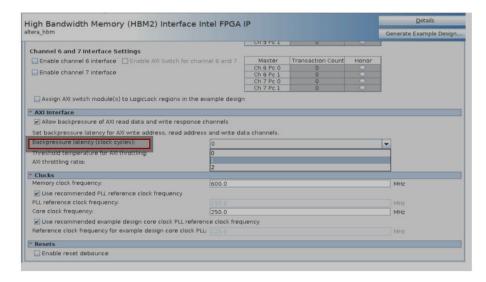

| Backpressure latency (clock cycles)                             | Select a value from 0 to 2 (0 is the default).  Allows the user interface time to react to the controller READY signals (AXI Write Address / Read Address / Write Data) and can also be used to improve timing between the AXI User Interface and the HBM2 IP with no increase in latency.                                                                                                                                                    |

|                                                                 | When Backpressure latency is set to 1, a single register stage is added in the AXI interface signals from the core to the HBM2 controller. When Backpressure latency is set to 2, one register stage is added on signals from the core to the HBM2 controller and one register on READY signal from the controller to the core.                                                                                                               |

|                                                                 | Beginning with the Intel Quartus Prime software version 19.4, the HBM2 IP itself generates the registers, so there is no need to manually add the registers as was necessary in earlier versions.                                                                                                                                                                                                                                             |

|                                                                 | If you have used the backpressure latency feature in an Intel Quartus Prime software version earlier than 19.4 and are upgrading to version 19.4 or later, you must remove the backpressure registers and regenerate the HBM2 IP in the newer software version. If you do not do this, the HBM2 interface IP will not function.  Refer to Improving User Logic to HBM2 Controller AXI Interface Timing for information on using this feature. |

| Threshold temperature for AXI throttling                        | This parameter defines the temperature of the HBM2 stack, in degrees Celsius, above which the HBM2 controller throttles AXI interface transactions. The temperature setting applies to all the AXI4 interfaces; however, you must enable this feature on the corresponding controller tab of each HBM2 controller. When you enable throttling, the HBM2 controller reduces the amount of traffic on the DRAM channel.                         |

| AXI throttling ratio                                            | If AXI interface throttling is enabled based on temperature this parameter defines the throttle ratio as a percentage (0 = no throttling, 100 = full throttling). You can enable or disable throttling on the individual controller tabs.                                                                                                                                                                                                     |

### Table 7. Group: General / Reset

| Display Name          | Description                                                           |

|-----------------------|-----------------------------------------------------------------------|

| Enable reset debounce | If enabled, reset debouncing logic is added on the wmcrst_n_in signal |

| Debounce period       | Set the debounce period in ms. The minimum period is 20 ms.           |

Table 8. Group: General / Clocks

| Display Name                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory clock frequency                                                  | The frequency of the memory clock in MHz. Specifies the clock frequency for the HBM2 interface. The maximum supported HBM2 clock frequency depends on the FPGA device speed grade:  - 1 Speed grade: 1 GHz - 2 Speed grade: 800 MHz - 3 Speed grade: 600 MHz                                                                                                                                                                                                                                                                                                          |

| Use recommended PLL reference clock frequency                           | When checked the PLL reference clock frequency is automatically calculated for best performance. Uncheck the check box if you want to specify your own PLL reference clock frequency. Automatically calculates the PLL reference clock frequency for best performance. You should disable this parameter if you want to select a different PLL reference clock frequency                                                                                                                                                                                              |

| PLL reference clock frequency                                           | PLL reference clock frequency. This is a universal interface bus (UIB) PLL reference clock. You must feed a clock of this frequency to the PLL reference clock input of the memory interface. Enable this parameter only if you disable <b>Use recommended PLL reference clock frequency</b> , and want to specify a PLL reference clock frequency. You should use the fastest possible PLL reference clock frequency to achieve best jitter performance.                                                                                                             |

| Core clock frequency                                                    | The frequency of the user AXI4 interface in MHz. This clock must be provided from an I/O PLL (not instantiated by the HBM2 IP). The reference clock driving the core I/O PLL must be provided from the same oscillator that supplies the UIB PLL reference clock on the board for a given HBM2 interface, to achieve maximum performance.  The maximum supported core frequency depends on the device speed grade and timing closure of the core interface clock within the FPGA. The minimum frequency of the core clock is one-fourth the HBM2 interface frequency. |

| Use recommended example design core clock PLL reference clock frequency | Automatically calculates the PLL reference clock frequency for best performance. Uncheck the check box if you want to specify your own PLL reference clock frequency.  Automatically calculates the example design core clock PLL reference clock frequency for best performance. Disable this parameter if you want to select a different reference clock frequency.                                                                                                                                                                                                 |

| Reference clock frequency for example design core clock PLL             | The PLL reference clock frequency in MHz for the PLL supplying the core clock. This parameter is used only in the example design PLL. Specify the externally provided reference clock frequency for the core clock PLL.                                                                                                                                                                                                                                                                                                                                               |

#### **Related Information**

- Clock Signals on page 38

- Non-zero Latency Backpressure on page 54

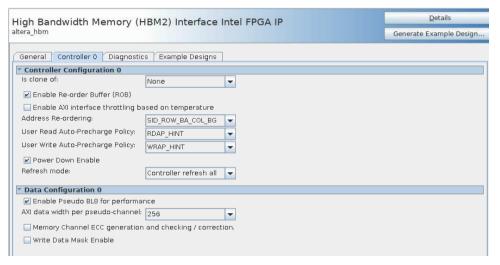

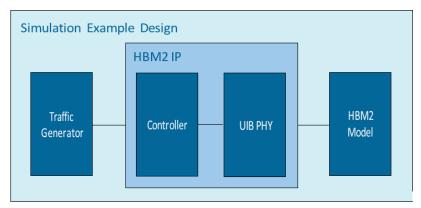

### **4.2.2.** Controller Parameters for High Bandwidth Memory (HBM2) Interface Intel FPGA IP

The parameter editor contains one **Controller** tab for each memory channel that you specify on the **General** tab. The **Controller** tab allows you to select the HBM2 controller options that you want to enable.

UG-20031 | 2020.04.13

### Figure 8. Controller Tab

### Table 9. Group: Controller / Controller 0 Configuration

Note:

When you enable the AXI Switch option, the controller configurations for the corresponding two HBM2 channels should use the same AXI Data Configuration and Enable Re-order buffer options.

| Display Name                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Is clone of                                          | Set this option to make this controller a clone of the selected controller. Parameters are copied from the specified controller. This parameter applies when you select more than one HBM2 controller. Set this parameter if you want one controller to have the same settings as another.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Enable Re-order buffer                               | Specifies that read data be reordered to match the order in which transactions are issued. If you disable this feature, the Read Data provided at the AXI Interface is not expected to follow the same order in which the Read Requests were issued. You can then reorder the data, based on the AXI read ID of the transaction.  This parameter applies to cases with multiple AXI transaction IDs. By using different AXI read/write IDs, you allow the HBM2 controller to reorder transactions for better efficiency. If you use the same AXI ID for all transactions, the controller issues the commands to memory in the order in which they arrive; in this instance, you need not enable the reorder buffer. |

| Enable AXI interface throttling based on temperature | Enables temperature-based throttling for this channel. You can specify the threshold temperature and throttling ratio on the General tab. Enables AXI thermal throttling for the specific HBM2 controller. The parameter that sets the trigger temperature for thermal throttling resides on the <b>General</b> tab. When the temperature of the HBM2 stack reaches the threshold temperature for HBM2 throttling as set on the <i>General</i> tab, the HBM2 controller begins to throttle user requests.                                                                                                                                                                                                           |

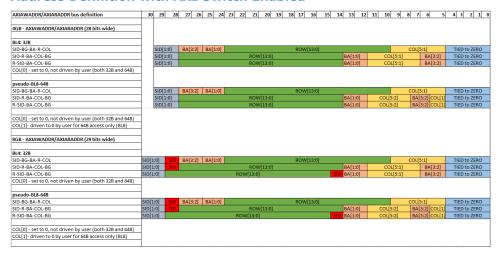

| Address reordering                                   | Describes the mapping of AXI address to HBM address.<br>Specifies the pattern for mapping from the AXI interface to<br>the HBM2 memory device. By choosing the right address<br>reordering configuration, you help to improve the efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                      | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Display Name                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | of accesses to the HBM2 memory device, based on user traffic pattern. The HBMC supports three types of address reordering:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                  | Address order (32B access: pseudo-BL8 disabled):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                  | SID-BG-BANK-ROW-COL[5:1]<br>SID-ROW-BANK-COL[5:1]-BG<br>ROW-SID-BANK-COL[5:1]-BG<br>COL[0]=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                  | Address order (64B access (pseudo-BL8 enabled):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                  | SID-BG-BANK-ROW-COL[5:1]<br>SID-ROW-BANK-COL[5:2]-BG-COL[1]<br>ROW-SID-BANK-COL[5:2]-BG-COL[1]<br>COL[1:0] = {00})                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                  | SID applies only to the 8GB/8H HBM2 devices and is not available for 4GB/4H devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| User Read Auto-Precharge Policy  | Describes the policy for determining whether to issue autoprecharge. FORCED indicates that the controller follows the user auto-precharge request exactly. HINT indicates that the controller may override the auto-precharge request by disabling it when a page hit is detected (that is, if it receives two commands, one with auto-precharge and one without auto-precharge to the same page, the controller changes auto-precharge for the first to 0 so that the second can access the page without reopening it). You can issue the request to precharge together with the read command, through the axi_x_y_aruser input, where x denotes the HBM2 channel number (0-7) and y denotes the HBM2 Pseudo Channel number (0/1).  You can choose between two values for this parameter:  RDAP_FORCED mode, in which the HBM2 controller implements a user-requested auto-precharge command.  RDAP_HINT mode, in which the controller determines when to issue an auto-precharge command, based on user-issued auto-precharge input and the address specified. |

| User Write Auto-Precharge Policy | Describes the policy for determining whether to issue autoprecharge. FORCED indicates that the controller follows the user auto-precharge request exactly. HINT indicates that the controller may override the auto-precharge request by disabling it when a page hit is detected (that is, if it receives two commands, one with auto-precharge and one without auto-precharge to the same page, the controller changes auto-precharge for the first to 0 so that the second can access the page without reopening it). You can issue a precharge request together with the write command, through the axi_x_y_awuser input, where x denotes the HBM2 channel number (0-7) and y denotes the HBM2 Pseudo Channel number (0/1).  You can choose between two values for this parameter:  • WRAP_FORCED mode, in which the HBM2 controller implements a user-requested auto-precharge command.  • WRAP_HINT mode, in which the controller determines when to issue an auto-precharge command, based on user-issued auto-precharge input and the address specified. |

| Power Down Enable                | Causes the controller to power down when idle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Refresh mode                     | Specifies the method of controlling refreshes to the high bandwidth memory. User refresh modes are initiated with an access on the Advanced Peripheral Bus (APB). You can choose one of three values for this parameter:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                  | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

UG-20031 | 2020.04.13

| Display Name                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                       | The default value is Controller refresh all, which allows the controller to decide when to issue refresh requests.  The User refresh all mode issues commands to all banks that correspond to an HBM2 Pseudo-Channel. User refresh all follows the APB protocol; the request must be addressed to one Pseudo-Channel at a time. A user-controlled refresh example is enabled in the design example when you select the User refresh all mode.  The User refresh per-bank mode issues commands to a specific bank that corresponds to an HBM2 Pseudo-Channel. User refresh per-bank follows the APB protocol; the request must be addressed to one Pseudo-Channel at a time. |

| Enable Pseudo BL8 for performance                     | If enabled, data access granularity is 64B (64 bits per Pseudo-Channel at BL8) which can achieve greater efficiency. Otherwise data access granularity is 32B (64 bits per Pseudo-Channel at BL4).  The controller sets the memory transactions burst length based on this setting and ignores the input provided on the user-driven axi_awsize and axi_arsize signals on the AXI interface.                                                                                                                                                                                                                                                                                |

| AXI data width per Pseudo-Channel                     | AXI Data width per Pseudo Channel. The available data widths are: 256 bits - This refers to 256-bit data transfers at the AXI interface. ECC or write data mask option is available in this data width mode only. 288 bits - This refers to 288-bit data transfers at the AXI interface. ECC or write data mask option is not available in this mode. You must implement your own ECC logic when choosing this data width option.                                                                                                                                                                                                                                           |

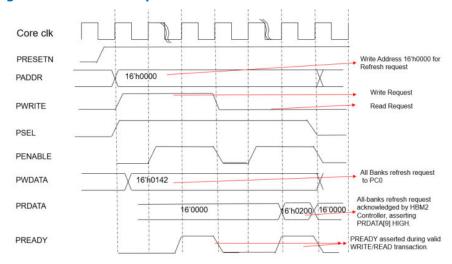

| Memory channel ECC generation and checking/correction | Memory Channel ECC generation and checking / correction. The HBM2 controller supports single-bit error correction and double-bit error detection. This feature is available only when you select the 256-bit AXI data width mode. The controller does not support write data mask in ECC generation mode.                                                                                                                                                                                                                                                                                                                                                                   |