# **Intel® FPGA Power and Thermal Calculator User Guide**

Updated for Intel® Quartus® Prime Design Suite: 20.3

$\label{eq:ug-20252} \mbox{ $U$G-20252 | 2021.01.21 } \\ \mbox{ Latest document on the web: } \mbox{ $PDF$ | $HTML$ }$

### **Contents**

| 1. Overview of the Intel® FPGA Power and Thermal Calculator                             | 3          |

|-----------------------------------------------------------------------------------------|------------|

| 1.1. Intel FPGA PTC Power Model Status                                                  | 3          |

| 1.2. Definitions of Power Terms Used in this Document                                   | 4          |

| 2. Setting Up the Intel FPGA Power and Thermal Calculator                               | <b>5</b>   |

| 2.1. Availability                                                                       | 5          |

| 2.2. Obtaining the Standalone Intel FPGA Power and Thermal Calculator                   |            |

| 2.3. Estimating Power Consumption with the Intel FPGA Power and Thermal Calculator      |            |

| 2.3.1. Estimating Power Consumption Before Starting the FPGA Design                     |            |

| 2.3.2. Estimating Power Consumption While Creating the FPGA Design                      | 6          |

| 2.3.3. Estimating Power Consumption After Completing the FPGA Design                    | 8          |

| 3. Intel FPGA Power and Thermal Calculator Graphical User Interface                     | 10         |

| 3.1. Intel FPGA PTC Select Family Dialog Box                                            |            |

| 3.2. Intel FPGA PTC Basic GUI Components                                                |            |

| 3.2.1. Intel FPGA PTC Data Entry Pages                                                  |            |

| 3.2.2. Intel FPGA PTC Field Types                                                       |            |

| 3.2.3. Intel FPGA PTC Input Field Dependencies                                          |            |

| 3.2.4. Intel FPGA PTC Data Entry Error Messages                                         | 14         |

| 4. Intel FPGA Power and Thermal Calculator Pages                                        | 16         |

| 4.1. Intel FPGA PTC - Power Summary                                                     |            |

| 4.2. Intel FPGA PTC - Common Page Elements                                              |            |

| 4.3. Intel FPGA PTC - Device Selection and Thermal Analysis Windows                     |            |

| 4.4. Intel FPGA PTC - Main Page                                                         |            |

| 4.5. Intel FPGA PTC - Logic Page                                                        |            |

| 4.6. Intel FPGA PTC - RAM Page                                                          |            |

| 4.8. Intel FPGA PTC - Clock Page                                                        |            |

| 4.9. Intel FPGA PTC - PLL Page                                                          |            |

| 4.10. Intel FPGA PTC - I/O Page                                                         |            |

| 4.11. Intel FPGA PTC - I/O-IP Page                                                      |            |

| 4.12. Intel FPGA PTC - Transceiver Page                                                 | 35         |

| 4.12.1. Estimating E-Tile Channel PLL Power with the Intel Power and Thermal            | 2-         |

| Calculator                                                                              |            |

| 4.14. Intel FPGA PTC - Thermal Page                                                     |            |

| 4.15. Intel FPGA PTC - Report Page                                                      |            |

| 4.16. Intel FPGA PTC - Intel Enpirion Page                                              |            |

| 5. Factors Affecting the Accuracy of the Intel FPGA Power and Thermal Calculator        |            |

| 5.1. Toggle Rate                                                                        |            |

|                                                                                         |            |

| 6. Intel FPGA Power and Thermal Calculator User Guide Archive                           | 53         |

| 7. Document Revision History for the Intel FPGA Power and Thermal Calculator User Guide | <b>5</b> / |

|                                                                                         |            |

| A Measuring Static Dower                                                                | 56         |

# 1. Overview of the Intel® FPGA Power and Thermal Calculator

This user guide describes the Intel® FPGA Power and Thermal Calculator (PTC). The current version of the Intel FPGA PTC supports Intel Agilex $^{\text{\tiny TM}}$  and Intel Stratix $^{\text{\tiny R}}$  10 devices.

This tool does not support older devices such as the Intel Arria $^{(8)}$  10 and Intel Cyclone $^{(8)}$  10 families; use the corresponding Early Power Estimator if you are working with those devices.

This user guide provides guidelines for using the Intel FPGA PTC, and details about thermal parameters and the factors contributing to FPGA power consumption.

You can calculate FPGA power consumption using the Intel FPGA PTC, and for more accurate power estimation, use the Power Analyzer in the Intel Quartus® Prime software. Intel recommends that you switch from the Intel FPGA PTC to the Power Analyzer once your design is available. The Power Analyzer produces more accurate results because it has more detailed information about your design, including routing and configuration information about each of the resources in your design.

You should treat the Intel FPGA PTC results as an estimate of power, not as a specification. You must verify the actual power consumption during device operation, because the information is sensitive to the actual device and design input signals. See the appendix *Measuring Static Power* for information on how to measure device static power in a way that correlates with the way that Intel FPGA PTC reports static power.

The features of the Intel FPGA PTC include:

- The ability to estimate the power consumption of your design before creating the design or during the design process.

- The ability to import device resource information from the Intel Quartus Prime software using the **.qptc** file generated with the Intel Quartus Prime software.

- The ability to determine preliminary thermal assessments of your design.

#### 1.1. Intel FPGA PTC Power Model Status

The Main page of the Intel FPGA Power and Thermal Calculator (PTC) shows the current power model status for the selected device. The power models in the Intel FPGA PTC can be in advance, preliminary, or final status:

- Advance power models are based on simulation results, process model projections, and design targets. Advance power models may change over time.

- Preliminary power models include post-layout simulation results, process data, and initial silicon correlation results. Preliminary power models may change over time.

- Final power models correlate to production devices with thousands of designs, and are not expected to change.

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

The accuracy of the power model is determined on a per-power-rail basis for both the Intel Quartus Prime Power Analyzer and the Intel FPGA Power and Thermal Calculator. For most designs, the Power Analyzer and the Intel FPGA PTC have the following accuracies, assuming final power models:

- Intel Quartus Prime Power Analyzer: Within 10% of silicon for the majority of power rails and the highest power rails, assuming accurate inputs and toggle rates.

- Intel FPGA Power and Thermal Calculator: Within 15% of silicon for the majority of power rails and the highest power rails, assuming accurate inputs and toggle rates.

#### 1.2. Definitions of Power Terms Used in this Document

The total power consumption of an Intel Agilex or Intel Stratix 10 device consists of the following components:

- Static power—the power that the configured device consumes when powered up but no user clocks are operating. Static power is dependent on device size, device grade, power characteristics, and junction temperature. For Intel Stratix 10 devices, this excludes DC bias power of analog blocks, such as I/O and transceiver analog circuitry.

- Dynamic power—the additional power consumption of the device due to signal activity or toggling.

- Standby power—for Intel Stratix 10 devices only: additional power, independent of signal activity or toggling, that is consumed only when specific circuitry is enabled through configuration RAM settings. Standby power includes, but is not limited to, I/O and transceiver DC bias power.

# 2. Setting Up the Intel FPGA Power and Thermal Calculator

#### 2.1. Availability

For Intel Agilex and Intel Stratix 10 devices, the Intel FPGA Power and Thermal Calculator (PTC) is integrated with the Intel Quartus Prime software. You can access the Power and Thermal Calculator from the **Tools** menu in the Intel Quartus Prime software, or by running the quartus\_ptc command in your command shell.

For the convenience of designers who may be working only on power estimation and not running design compilations with the Intel Quartus Prime software, a standalone version of the Intel FPGA PTC is also available. The standalone version offers all the same features as the Intel FPGA Power and Thermal Calculator version integrated within the Intel Quartus Prime software.

# 2.2. Obtaining the Standalone Intel FPGA Power and Thermal Calculator

The standalone Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) is available from the *Additional Software* tab of the Intel Quartus Prime Pro Edition page of the *Download Center for FPGAs*.

#### **Launching the Standalone Version**

- To launch the Windows version of the standalone Intel FPGA PTC, click the icon in the **Start** menu.

- To launch the Linux version of the standalone Intel FPGA PTC, navigate to the folder where you installed the Intel FPGA PTC, and type ptc <Enter>.

# 2.3. Estimating Power Consumption with the Intel FPGA Power and Thermal Calculator

With the Intel FPGA Power and Thermal Calculator (Intel FPGA PTC), you can estimate power consumption at any point in your design cycle.

The Intel FPGA PTC lets you estimate the power consumption when you have not yet begun your design, or when your design is only partially complete. Although the Intel FPGA PTC can provide a power estimate for your completed design, Intel recommends

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

that you use the Power Analyzer in the Intel Quartus Prime software when the design is available, for a more accurate estimate based on the exact placement and routing information of the completed design.

#### 2.3.1. Estimating Power Consumption Before Starting the FPGA Design

Table 1. Advantage and Constraints of Power Estimation before Designing FPGA

| Advantage                                                                                                                                                                      | Constraint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| You can obtain power estimates before starting your FPGA design.      You can adjust design resources and parameters and see how those changes affect total power consumption. | Accuracy depends on your inputs and your estimate of the device resources. Where this information may change (during or after your design is complete), your power estimation results will be less accurate.      The Intel FPGA PTC uses averages and not the actual design implementation details. The Power Analyzer has access to the full design details. For example, the Intel FPGA PTC uses average values for ALM configuration, while the Power Analyzer uses an exact configuration for each ALM. |  |

To estimate power consumption with the Intel FPGA PTC before starting your FPGA design, follow these steps:

- 1. On the Main page of the Intel FPGA PTC, select the target device, device grade, package, and transceiver grade from the **Device**, **Device Grade**, **Package**, and **Transceiver Grade** drop-down lists.

- 2. Enter values for each page in the Intel FPGA PTC. Different pages display different power-consuming FPGA resources, such as clocks and phase-locked loops (PLLs).

- 3. The calculator displays the total estimated power consumption in the **Total Power** cell of the Power Summary.

- 4. Save the file as roject name.ptc for later use.

Note:

For information on the individual pages of the Intel FPGA PTC, refer to the Power and Thermal Calculator Pages chapter.

#### 2.3.2. Estimating Power Consumption While Creating the FPGA Design

If your FPGA design is partially complete, you can import a <code>.qptc</code> file (revision

name>.qptc) generated by the Intel Quartus Prime software into the Intel FPGA

Power and Thermal Calculator. After importing the information from the <code>.qptc</code> file into the Intel FPGA PTC, you can edit the Intel FPGA PTC data to reflect the device resource estimates for your final design.

If you have instructed the Intel Quartus Prime Power Analyzer (QPA) to produce a .qptc file (see the Processing > Power Analyzer menu in the Intel Quartus Prime software), the following assignment is written to the .qsf file:

set\_global\_assignment -name POWER\_AND\_THERMAL\_CALCULATOR\_EXPORT\_FILE <filename>

When you open the Intel FPGA PTC with a Quartus project (either from the **Tools** menu, or if you specified a project on the quartus\_ptc command line) it looks for this QSF assignment and attempts to open the specified file. If the specified file isn't found, an error message occurs. After dismissing the error message, you are free to use the Intel FPGA PTC to enter design information. If you want, you can remove this QSF assignment to suppress the error message when opening the Intel FPGA PTC.

Table 2. Advantages and Constraints of Power Estimation if your FPGA Design is Partially Complete

| Advantage                                                                                                                                                                                                                                                                                                      | Constraint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| You can perform power estimation early in the FPGA design cycle. You can adjust design resources and parameters and see how those changes affect total power consumption. Provides the flexibility to automatically populate the Intel FPGA PTC based on the Intel Quartus Prime software compilation results. | Accuracy depends on your inputs and your estimate of the device resources; where this information may change (during or after your design is complete). Your power estimation results may be less accurate.      Unlike the Power Analyzer, which has access to the full design details, the Intel FPGA PTC uses averages and not the actual design implementation. For example, the Intel FPGA PTC uses average values for ALM configuration, while the Power Analyzer uses an exact configuration for each ALM. |  |

#### **Importing a File**

Importing a **.qptc** file saves you time and effort otherwise spent on manually entering all the information into the Intel FPGA PTC. You can also manually change any of the values after importing a file.

You can create a **.qptc** file for an Intel Agilex- or Intel Stratix 10-based design, by selecting **Generate Power and Thermal Calculator Import File** from the **Project** menu in the Intel Quartus Prime software.

#### **Importing Data into the Intel FPGA Power and Thermal Calculator**

You must import the **.qptc** file into the Intel FPGA PTC before modifying any information. Also, you must verify all your information after importing a file.

Importing a file from the Intel Quartus Prime software populates all input values based on your design and design settings that were specified in the Intel Quartus Prime software. Alternatively, you can import values exported from an earlier version of the Intel FPGA PTC.

To import data into the Intel FPGA PTC, follow these steps:

- 1. On the File menu, click Open.

- 2. Browse to an existing Intel FPGA PTC file generated by the current or earlier version of the Intel FPGA PTC or the Intel Quartus Prime software, and click **Open**.

- 3. After the file is imported into the Intel FPGA PTC, the mouse cursor changes from busy to normal. If there are any warnings during the import, the Intel FPGA PTC displays the PTC Import Warnings dialog box. Analyze each warning carefully to understand the cause; if any of the warnings are unexpected, you must manually modify the corresponding fields in the Intel FPGA PTC after the import is completed. You can copy all warning messages to the clipboard for future reference by clicking Copy. Click OK to dismiss the PTC Import Warnings dialog box. (Examples of warnings that could occur, would be if device ordering codes

had changed such that previous values for Device Grade, Device, and Package and Transceiver Grade fields could not be imported directly, or if the  $V_{CC}$  voltage isn't applicable to the selected device.)

## Importing .qptc Data for Intel Stratix 10 Devices into the Intel FPGA Power and Thermal Calculator for Intel Agilex Devices

If you want to import a data file originally exported from the Intel Quartus Prime software based on a design targeting Intel Stratix 10 devices, for use in the Intel Agilex version of the Intel FPGA Power and Thermal Calculator, follow these steps:

- 1. In the Intel Stratix 10 version of the Power and Thermal Calculator, open the existing **.qptc** file generated by the Intel Quartus Prime software based on a design targeting an Intel Stratix 10 device.

- Save the file as a .ptc file, and exit the Intel Stratix 10 Power and Thermal Calculator.

- 3. Launch the Intel Agilex version of the Power and Thermal Calculator, and open the .ptc file created in step 2.

- 4. Select the appropriate Intel Agilex device and modify resources and other settings to reflect your planned design targeting the Intel Agilex device.

### Importing an Early Power Estimator file from an Earlier Version to the Intel FPGA Power and Thermal Calculator (For Intel Stratix 10 devices only)

If you want to import a **.csv** file originally exported from the Intel Quartus Prime software version 19.4, or from the Early Power Estimator spreadsheet version 19.4, for a design targeting an Intel Stratix 10 device, for use in the Intel Stratix 10 version of the Power and Thermal Calculator version 20.3, follow these steps:

- Open the Early Power Estimator .csv file exported from the 19.4 version of the Intel Quartus Prime software or Early Power Estimator spreadsheet in the Intel Stratix 10 version of the Power and Thermal Calculator.

- 2. Save the file as a **.ptc** file, and exit the Intel Stratix 10 Power and Thermal Calculator.

#### *Note:* Some general points about the import process:

- A **.qptc** file created for an Intel Agilex or Intel Stratix 10 design, can always be imported into the Intel FPGA PTC for use with the same device family.

- A .ptc file created for an Intel Stratix 10 design can be imported into the Intel FPGA PTC for use with the similar design targeting an Intel Agilex device.

- A .qptc file created for an Intel Agilex design, cannot be imported into the Intel FPGA PTC for use with an Intel Stratix 10 design.

- Some power-consuming resources such as transceivers of an original Intel Stratix 10 design, might not be carried through the import process.

#### 2.3.3. Estimating Power Consumption After Completing the FPGA Design

#### 2. Setting Up the Intel FPGA Power and Thermal Calculator

UG-20252 | 2021.01.21

If your design is complete, Intel strongly recommends that you do not use the Power and Thermal Calculator, and instead use the Power Analyzer in the Intel Quartus Prime software. The Power Analyzer uses toggle rates from simulation, user assignments, and placement-and-routing information to provide more accurate power estimates.

**Send Feedback**

# 3. Intel FPGA Power and Thermal Calculator Graphical User Interface

The Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) employs a standard graphical user interface (GUI) similar to other tools in the Intel Quartus Prime software.

#### 3.1. Intel FPGA PTC Select Family Dialog Box

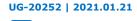

When you launch the Intel FPGA Power and Thermal Calculator (Intel FPGA PTC), the first dialog box that appears allows you to select the Intel FPGA family for your Intel FPGA PTC design.

Figure 1. Select Family Dialog Box

To proceed with the Intel FPGA PTC, select the desired device family, and click **OK**.

Note:

- 1. Once you have selected a device family to model, you cannot change that selection unless you start a new Intel FPGA PTC instance.

- Currently, the Intel FPGA PTC supports the Intel Agilex and Intel Stratix 10 FPGA device families. You will notice some differences on the Intel FPGA PTC pages, depending on the device family selected.

#### 3.2. Intel FPGA PTC Basic GUI Components

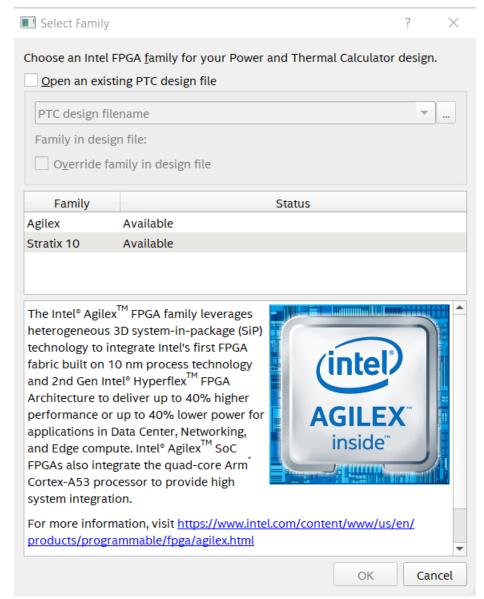

The Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) GUI provides data entry pages, and dockable **Power Summary**, **Device Selection**, **Page Selection**, and **Thermal Analysis** windows.

Not all dockable windows may be visible by default. You can change which of the dockable windows are visible using the **View** menu.

The shading of input fields alternates between white and light gray; these fields are editable, either by double-clicking and selecting a value from a drop-down list or by typing a value directly. Output fields are shaded in a darker gray. Fixed input fields—those whose values are determined by settings elsewhere and therefore aren't directly editable—have their font dimmed.

Figure 2. Intel FPGA PTC Graphical User Interface (GUI)

#### **Data Entry Area**

The data entry area provides pages for entering parameters associated with various aspects of your design.

#### **Power Summary**

The Power Summary shows the calculated power consumption of various types of resources, based on the current values in the data entry pages. The fields of the Power Summary cannot be edited directly.

#### **Device and Thermal Analysis Pages**

The **Device** and **Thermal Analysis** windows summarize device characteristics and presumed thermal operating conditions, respectively. This information is also available on the **Main** and **Thermal** data entry pages, respectively.

#### **Page Selection**

The **Page Selection** window allows you to choose the data entry page that you want to display.

#### 3.2.1. Intel FPGA PTC Data Entry Pages

The look and feel of the Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) is the same whether you are using the standalone version or the version integrated within the Intel Quartus Prime software. There are, however, differences depending on whether you are targeting Intel Agilex or Intel Stratix 10 devices.

The following are the pages within the Intel FPGA PTC:

- The **Main** page allows you to enter device, package, and cooling information, and displays thermal analysis information pertaining to constant junction temperature.

- The **Logic** page allows you to enter logic resources for all modules in your design.

- The RAM page represents design modules using RAM blocks. Among other

information, enter RAM type, data width, RAM depth (if applicable), RAM mode,

and port parameters.

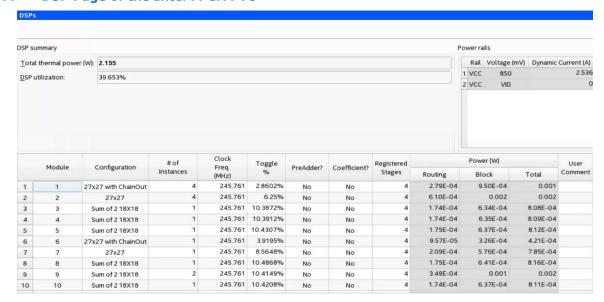

- The **DSP** page represents DSP design modules. Among other information, enter DSP configuration, clock frequency, toggle percentage, and register usage.

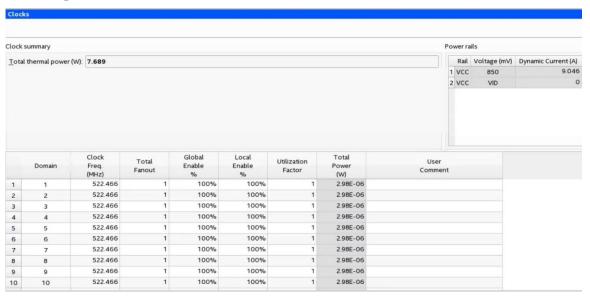

- The **Clock** page represents clock networks of separate clock domains.

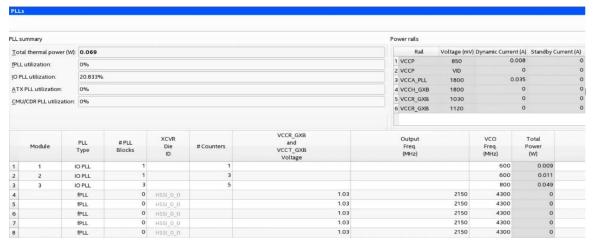

- The PLL page represents one or more PLLs in the device.

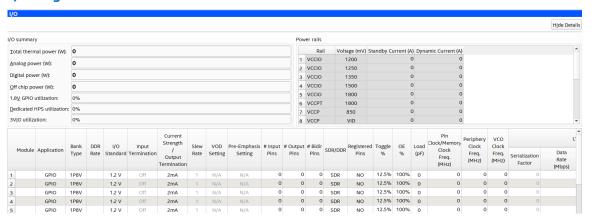

- The **I/O** page represents design modules using general-purpose I/O pins. This page does not apply to transceiver I/O pins. Among other information, enter I/O standard, input termination, current strength or output termination, data rate, clock frequency, output enable static probability, and capacitive load.

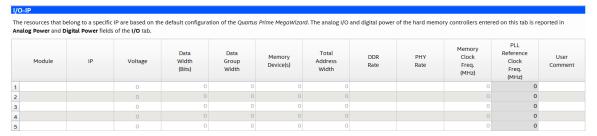

- The **I/O-IP** page represents design modules using complex I/O IP, such as DDR.

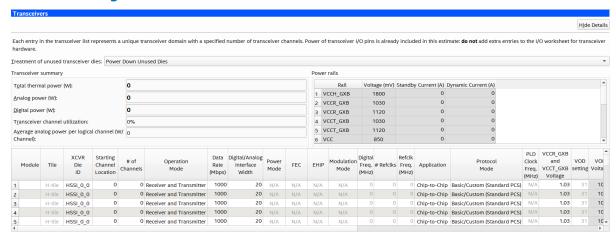

- The Transceiver page allows you to enter transceiver resources and their settings for all modules in your design.

- The HPS page applies to devices with HPS.

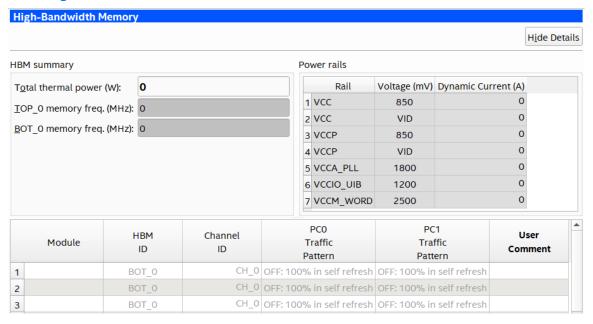

- The **HBM** page (Intel Stratix 10 devices only).

- The Thermal page.

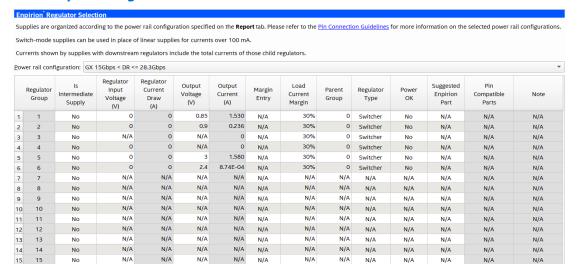

- The **Report** page shows per-rail currents calculated by the Intel FPGA Power and Thermal Calculator (PTC).

- The Intel Enpirion® page.

#### 3.2.2. Intel FPGA PTC Field Types

The Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) employs input fields with which you configure the tool for your design; the shading of input fields alternates between white and light gray. These fields are editable, either by double-clicking and selecting a value from a drop-down list or by typing a value directly.

Output fields report calculated values, and are shaded in a darker gray. Fixed input fields have their font dimmed.

#### 3.2.3. Intel FPGA PTC Input Field Dependencies

The value you specify for some input fields may affect the allowed values for other fields.

For example, the device package that you select may determine what transceiver grades are selectable. If you change the selected device package, and the currently selected transceiver grade is still legal for the new package, the **Transceiver Grade** value does not change. However, if the currently selected transceiver grade is not compatible with the selected device package, the **Transceiver Grade** value automatically changes to one of the legal values.

Changes that you make on one page may affect values on another page, because of dependencies between input fields. For example, if you select a device that does not support the current I/O standard specified in the I/O page, that I/O standard automatically changes to one of the I/O standards supported by the new device.

In general, the Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) does not automatically change an input value unless it is necessary to preserve the legality of the input. Changes in one field have minimal impact on other fields, while ensuring that overall combination of field values are legal. However, this can sometimes lead to unanticipated results. Consider the following example:

Assume that **Dev1** is selected in the Main page, and I/O standard **IO1** is selected in the I/O page. Assume also that device **Dev1** supports I/O standards **IO1** and **IO2**. Suppose that you change the device selection to **Dev2**, which supports only one I/O standard, **IO2**. As a result of you changing the device selection, the I/O standard in the I/O page changes to **IO2**. If you then reverted the device selection back to **Dev1**, the I/O standard does not change, because **IO2** is a legal I/O standard value for the device **Dev1**. The important point to note, is that the changing of device from **Dev1** to **Dev2** and back again, had the—potentially unintended—consequence of changing the I/O standard in the I/O page.

Note:

In most cases, field dependencies are limited to the same page, and often even within the same row. However, device, device grade, package and transceiver grade selection can have a much wider impact, as illustrated above. A simple way to verify that no unintended changes resulted from changing a device is to use the **File**  $\succ$  **Save As** function to export the Intel FPGA PTC state before and after the change in device selection. You can then compare the two .ptc files using a third-party *diff* utility to identify any fields that have changed.

#### 3.2.4. Intel FPGA PTC Data Entry Error Messages

If the value you enter does not pass legality checks, or is inappropriate for the field, the system displays an error message. Typically the message may indicate the conditions under which a value is invalid, or specify a valid range of values.

#### **Error Message Type: Invalid Value**

If you enter an invalid value — such as a temperature value that is outside the allowed range for a selected family, device, transceiver grade, device grade and package combination — an error message appears, indicating that the entered value is invalid and stating the allowed range of values. You can click OK to dismiss the error message, and the field reverts to its previous value.

#### 3. Intel FPGA Power and Thermal Calculator Graphical User Interface

UG-20252 | 2021.01.21

#### **Error Message Type: Incorrect Format**

Many fields require a specific type of data. If the data you enter is not of the type required, an error message appears. For example, if an integer value is expected and you enter a fractional value, the resulting error message indicates that the entered value cannot be converted to a valid value for the input field. After you click OK, the field reverts to its previous value.

Similarly, if a numerical value is expected and you enter a text value, the resulting error message indicates that the entered value cannot be converted to a valid value for the input field. After you click OK, the field reverts to its previous value.

### 4. Intel FPGA Power and Thermal Calculator Pages

The Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) is a tool that allows you to enter information onto pages based on architectural features. The Intel FPGA PTC then reports, in watts, subtotals of the power consumed by each architectural feature. For more information about each architectural feature refer to the respective page descriptions.

Note:

Currently, the Intel FPGA PTC supports the Intel Agilex and Intel Stratix 10 FPGA device families. You will notice some differences on the Intel FPGA PTC pages, depending on the device family selected.

#### 4.1. Intel FPGA PTC - Power Summary

The **Power Summary** tile of the Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) can be displayed at all times, and shows the calculated power consumption by resource type.

The values displayed in the **Power Summary** update in real time, as you change parameters on the data entry pages.

In addition to displaying total power consumption, the **Power Summary** displays power consumption values for the resource types listed in the following table.

**Table 3.** Resource Types Displayed in the Power Summary

| Intel Agilex PTC Power Summary |                                                                                                           |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| Resource Type                  | Description                                                                                               |  |

| Logic                          | The dynamic power consumed by adaptive logic modules (ALMs), flipflops (FFs) and routing fabric.          |  |

| RAM                            | The dynamic power consumed by specialized blocks optimized for data storage and retrieval.                |  |

| DSP                            | The dynamic power consumed by specialized blocks optimized for fast math operations.                      |  |

| Clock                          | The dynamic power consumed by clock networks. The clock dynamic power is affected by the selected device. |  |

| PLL                            | The dynamic power consumed by phase-locked loops (PLLs).                                                  |  |

| I/O                            | The dynamic power consumed by I/O pins and I/O subsystems.                                                |  |

| Transceiver                    | The dynamic power consumed by transceiver blocks.                                                         |  |

| HPS                            | The dynamic power consumed by the hard processor system (HPS).                                            |  |

| НВМ                            | The dynamic power consumed by high-bandwidth memory (HBM) and the universal interface bus (UIB) modules.  |  |

|                                | continued                                                                                                 |  |

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

| Miscellaneous                     | The dynamic power consumed by other FPGA circuitry not included in other categories above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Static Power                      | The power that the configured device consumes when powered up but with no user clocks operating. The static power ( $P_{STATIC}$ ) is the power dissipated on the chip, independent of design activity. $P_{STATIC}$ includes the static power from all FPGA functional blocks. $P_{STATIC}$ is the only power component that varies with junction temperature and power characteristics (process). $P_{STATIC}$ is also the only power component that varies significantly with selected device.                                                                                                                                                                             |

| Total Power                       | The total power dissipated as heat from the FPGA. Does not include power dissipated in off-chip termination resistors. Total power dissipation in the FPGA may differ from the sum of power on all rails due to several factors including, but not limited to, power dissipated in off-chip termination resistors.                                                                                                                                                                                                                                                                                                                                                            |

|                                   | Intel Stratix 10 PTC Power Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Resource Type                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Logic                             | The dynamic power consumed by adaptive logic modules (ALMs), flipflops (FFs) and associated routing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RAM                               | The dynamic power consumed by RAMs and associated routing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DSP                               | The dynamic power consumed by digital signal processing (DSP) blocks and associated routing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Clock                             | The dynamic power consumed by clock networks. The clock dynamic power is affected by the selected device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PLL                               | The dynamic and standby power consumed by phase-locked loops (PLLs).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I/O                               | The dynamic and standby power consumed by I/O pins and I/O subsystems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Transceiver                       | The dynamic and standby power consumed by transceiver blocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Hard Processor                    | The dynamic and standby power consumed by the hard processor system (HPS).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| High-Bandwidth Memory             | The dynamic power consumed by high-bandwidth memory (HBM) and the universal interface bus (UIB) modules.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Static Power                      | The static power consumed regardless of clock frequency. This includes static power consumed by I/O and transceiver blocks, but does not include standby power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Total, Before SmartVID<br>Savings | The total power consumption before SmartVID power savings. Includes static power (PSTATIC) and power consumed by different blocks as reported above. Does not include power dissipated in off-chip termination resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SmartVID Savings                  | The total power reduction (static and dynamic) resulting from the lower voltage that is made possible by SmartVID. This power reduction is dependent on the user design and device characteristics. The combination of these factors may result in different static and dynamic power savings, so the exact dynamic and static components are not identified separately, and the power reduction reported here is a worst-case result. The reduction reported in this field is already taken into consideration in the Total (W) field. The SmartVID Power Savings field applies only to devices that support SmartVID and only when Power Characteristics is set to Maximum. |

| Total Power                       | The total power dissipated as heat from the FPGA. Does not include power dissipated in off-chip termination resistors. Total power dissipation in the FPGA may differ from the sum of power on all rails due to several factors including, but not limited to, power dissipated in off-chip termination resistors.                                                                                                                                                                                                                                                                                                                                                            |

### 4.2. Intel FPGA PTC - Common Page Elements

The Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) is divided into multiple pages, each allowing entry of a subset of FPGA resources. Some elements are common to more than one page.

#### **Recalculate mode**

The **Recalculate mode** pulldown is available at the top-left corner of the PTC, regardless of which page is displayed. The available settings are *Automatic* and *Manual*:

- Automatic: In Automatic mode, the system automatically recalculates all field values whenever you modify an input value. Automatic is the default mode.

- Manual: In Manual mode, the system does not recalculate values automatically. To recalculate, you must press the blue button immediately to the right of the Recalculate mode pulldown.

Tip:

In *Automatic* mode, the system may appear to become unresponsive while recalculating. If you are making multiple changes, you may find it a better experience to select *Manual* mode, and recalculate only once, after you have entered all your changes.

#### **Total Thermal Power**

The Total thermal power field estimates the total thermal power consumed by all FPGA resources on the specific page. Some pages may also provide a breakdown of the components contributing to the total thermal power. The total thermal power displayed in individual pages does not include static power, which is reported in the Power Summary for the whole device.

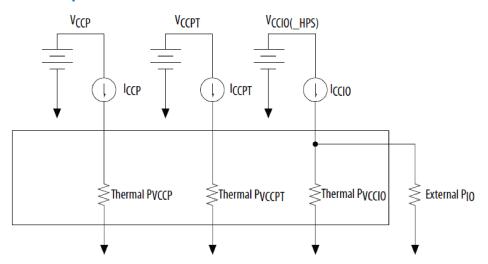

Thermal power is the power dissipated in the device. Total thermal power is the sum of the thermal power of all the resources used in the device, including dynamic power. Total thermal power includes only the thermal component for the I/O page and does not include external power dissipation, such as from voltage-referenced termination resistors.

#### **Resource Utilization**

Most pages contain one or more fields that provide an estimate of the percentage resource utilization for the modules in the specific page. Such values are calculated based on the maximum available resources of a given type for a selected device. If resource utilization exceeds 100%, it indicates that the current device may not be able to support the resources entered into the page.

#### **Power Rail Current Consumption**

Most pages include a table showing the dynamic current consumption for all power rails used by the FPGA resources in the specific page. The same power rail may appear in multiple pages, and the dynamic currents reported in the **Report** page are the sums of all corresponding currents for a given rail at a given voltage in individual pages. The **Report** page also includes static currents, which are not reported in individual pages.

Note:

If you want to resize columns within a page, that is most easily done with the page size maximized. You can also resize all columns on all pages by selecting **View** ➤ **Resize All Columns**, or by pressing F5 on your keyboard.

UG-20252 | 2021.01.21

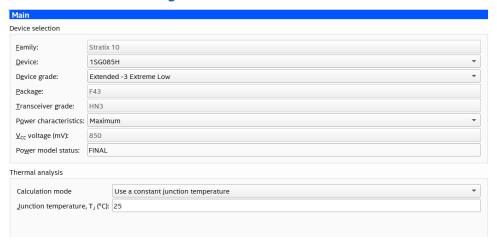

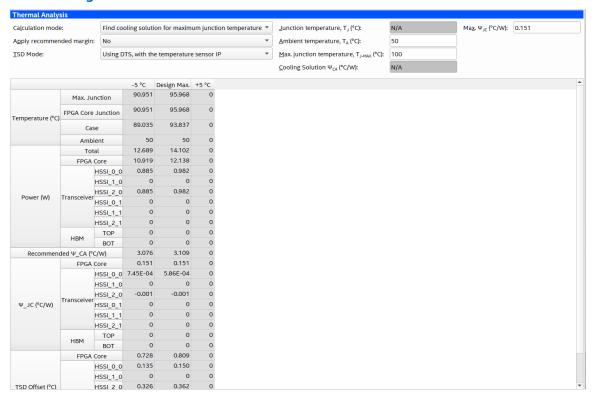

# 4.3. Intel FPGA PTC - Device Selection and Thermal Analysis Windows

The **Device Selection** window displays information also available on the **Main** page; the **Thermal Analysis** window displays a subset of the information available on the **Thermal** page.

The **Device Selection** and **Thermal Analysis** pages can be displayed at all times, allowing you to view this information while working on a page other than the **Main** page.

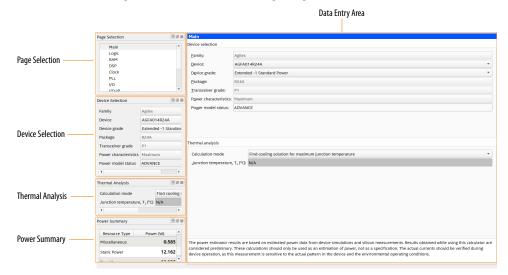

#### 4.4. Intel FPGA PTC - Main Page

The Main page of the Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) allows you to enter device, package, and cooling information, and displays thermal analysis options.

#### Figure 3. Intel FPGA PTC Main Page

The required parameters depend on whether the junction temperature is manually entered or auto computed.

#### **Table 4.** Device Selection Parameters

| Parameter    | Description                                                                                                                                                                                                                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Family       | Shows the device family selected at startup, either directly or through the imported file.                                                                                                                                     |

| Device       | Select your device.  Larger devices consume more static power and have higher clock dynamic power. All other power components are unaffected by device selection.                                                              |

| Device Grade | Select the combination of Operating Temperature, Speed Grade, and Power Option used. Refer to the device datasheet for available combinations.                                                                                 |

| Package      | Select the device package.  Larger packages provide a larger cooling surface and more contact points to the circuit board, thus they offer lower thermal resistance. Package selection does not affect dynamic power directly. |

|              | continued                                                                                                                                                                                                                      |

| Parameter                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transceiver Grade            | Select the transceiver grade.  Note: For information on transceiver grades, refer to the Device Overview document for a given device family.                                                                                                                                                                                                                                                                                                                                                      |

| Power characteristics        | Select typical or theoretical worst-case silicon process.  There is a process variation from die-to-die. This variation primarily affects static power consumption. If you choose <i>Typical</i> power characteristics, estimates are based on longterm projections of average power consumed by typical silicon. For FPGA board power supply design and thermal design, choose <i>Maximum</i> for worst-case values.  (The <i>Typical</i> option is not yet available for Intel Agilex devices.) |

| V <sub>CC</sub> Voltage (mV) | (This field appears in the Intel Stratix 10 PTC only.)                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Power Model Status           | Indicates whether the power model for the device is in advance, preliminary, or final status.                                                                                                                                                                                                                                                                                                                                                                                                     |

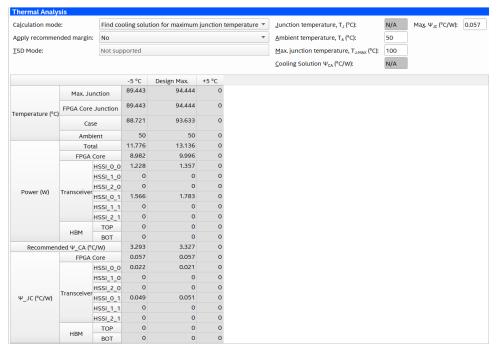

The Thermal Analysis section displays the junction temperature  $(T_J)$  and other thermal parameters, depending on the thermal analysis mode.

#### **Table 5.** Thermal Analysis

| Column Heading                            | Description                                                                                                                                                                         |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Calculation mode                          | Specifies the conditions at which to run thermal analysis.                                                                                                                          |

| Junction temperature, T <sub>J</sub> (°C) | Specify the junction temperature for all dies in the package.  Note: This field is applicable only when the selected Calculation mode value is Use a constant junction temperature. |

You can directly enter or automatically compute junction temperatures based on the information provided. To enter the junction temperature, select **Use a constant junction temperature** in the **Calculation mode** field, then enter the desired junction temperature in the **Junction temperature T<sub>J</sub>** ( $^{\circ}$ C) field in the **Thermal Analysis** section. In this mode, the junction temperatures for all dies in the package are assumed to have the specified value. To automatically compute junction temperatures, select one of the other options in the same field.

#### 4.5. Intel FPGA PTC - Logic Page

The Logic of the Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) allows you to enter logic resources for all modules in your design.

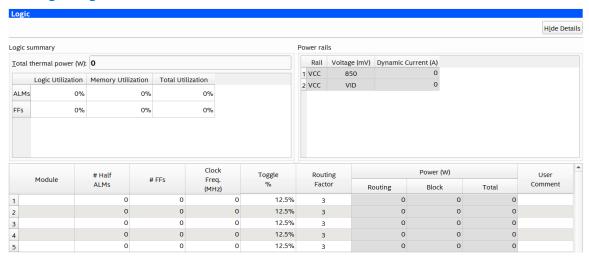

#### Figure 4. Logic Page of the Intel FPGA PTC

#### **Table 6.** Logic Page Information

| Column Heading   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Module           | Specify a name for each module of the design. This is an optional entry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| #Half ALMs       | Enter twice the number of Adaptive Logic Modules (ALMs) used in your design, which you can find in the Compilation Report, by selecting Fitter ➤ Place Stage ➤ Resource Usage Summary. For power estimation purposes, the number of ALMs used in your design is the sum of the following values in the Compilation Report:  • ALMs used for LUT logic and register circuitry  • ALMs used for LUT logic  • ALMs used for register circuitry  • ALMs adjustment for power estimation  The adjustment for power estimation is necessary because some unused ALMs may still consume power due to Fitter optimizations.                                                                                                                                                                                                                                                                                                       |

| # FFs            | Enter the number of <b>Primary logic registers</b> , plus <b>Secondary logic registers</b> , plus the number of registers reported as <b>Register control circuitry for power estimation</b> , all of which you can find in the Compilation Report, by selecting <b>Fitter &gt; Place Stage &gt; Resource Usage Summary</b> . The <b>Register control circuitry for power estimation</b> adjustment is necessary because some unused registers may still consume power due to fitter optimizations.  Clock routing power associated with flipflops is calculated separately on the Clock page of the Intel FPGA PTC.                                                                                                                                                                                                                                                                                                      |

| Clock Freq (MHz) | Enter a clock frequency (in MHz). This value is limited by the maximum frequency specification for the device family.  For Intel Stratix 10 devices, when you import a design from the Intel Quartus Prime software, some imported half ALMs and flipflops may have a clock frequency of 0 MHz; this can occur for one of two reasons:  • The Intel Quartus Prime software did not have sufficient information to determine clock frequency due to incomplete clock constraints.  • The Intel Quartus Prime software exported a .qptc file containing half ALMs where only flipflops are used. Such ALMs are imported as ALMs with clock frequency of 0 MHz, while their flipflops are imported into a separate row with the correct clock frequency.  It is possible that due to the floating point precision used in the tool, the frequency reported may differ slightly from what is reported in the Timing Analyzer. |

| Colu           | ımn Heading | Description                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Toggle %       |             | Enter the average percentage of clock cycles when the block output signals change values. Toggle percentage is multiplied by clock frequency to determine the number of transitions per second. For example, 100 MHz frequency with a 12.5% toggle rate, means that each LUT or flipflop output toggles 12.5 million times per second (100MHz × 12.5%).                                   |

|                |             | The toggle percentage ranges from 0 to 100%. Typically, the toggle percentage is 12.5%, which is the toggle percentage of a 16-bit counter. Most logic only toggles infrequently; therefore, toggle rates of less than 50% are more realistic. To ensure you do not underestimate the toggle percentage, use a realistic toggle percentage obtained through simulation.                   |

|                |             | For example, a T flipflop (TFF) with its input tied to VCC has a toggle rate of 100% because its output is changing logic state on every clock cycle. Refer to the 4-Bit Counter Example below for a more detailed analysis.                                                                                                                                                              |

|                |             | For any rows containing flipflops, toggle percentage cannot exceed 100%. A small portion of ALMs in a design may experience glitching that results in toggle percentage exceeding 100% for such ALMs. Enter such ALMs into a separate row with # FFs set to 0. For Intel Stratix 10 devices in the Intel FPGA PTC, toggle percentage cannot exceed 100% in any rows containing flipflops. |

| Routing Factor |             | Indicates the extent of the routing power of the outputs.                                                                                                                                                                                                                                                                                                                                 |

|                |             | Characteristics that have a large power impact and are captured by this factor include the following:                                                                                                                                                                                                                                                                                     |

|                |             | The fanout of the outputs                                                                                                                                                                                                                                                                                                                                                                 |

|                |             | <ul> <li>The number of routing resources used</li> <li>The relative power usage of the different types of routing resources used</li> </ul>                                                                                                                                                                                                                                               |

|                |             | The default value for this field is typical; the actual value varies between blocks in                                                                                                                                                                                                                                                                                                    |

|                |             | your design, and depends on the placement of your design. For most accurate results, you should import this value from the Intel Quartus Prime software after compiling your design, because the Intel Quartus Prime software has access to detailed placement and routing information.                                                                                                   |

|                |             | In the absence of an Intel Quartus Prime design, higher values generally correspond to signals that span large distances on the FPGA and fanout to many destinations, while lower values correspond to more localized signals.                                                                                                                                                            |

|                |             | You can change this field from its default value to explore possible variations in power consumption depending on block placement. When changing this value, keep in mind that typical designs rarely use extreme values, and only for a small subset of the design.                                                                                                                      |

| Power (W)      | Routing     | Indicates the power dissipation due to estimated routing (in W).                                                                                                                                                                                                                                                                                                                          |

|                |             | Routing power depends on placement and routing, which is a function of design complexity. The values shown are representative of routing power based on observed behavior across more than 100 real-world designs.                                                                                                                                                                        |

|                |             | Use the Intel Quartus Prime Power Analyzer for accurate analysis based on the exact routing used in your design.                                                                                                                                                                                                                                                                          |

|                | Block       | Indicates the power dissipation due to internal toggling of the ALMs and registers (in W).                                                                                                                                                                                                                                                                                                |

|                |             | Logic block power is a combination of the function implemented and the relative toggle rates of the various inputs. The Intel FPGA PTC uses an estimate based on observed behavior across more than 100 real-world designs.                                                                                                                                                               |

|                |             | Use the Intel Quartus Prime Power Analyzer for accurate analysis based on the exact synthesis of your design.                                                                                                                                                                                                                                                                             |

|                | Total       | Indicates the estimated power (in W), based on information entered into the Intel FPGA PTC. It is equal to the sum of routing power and block power.                                                                                                                                                                                                                                      |

| User Comment   | :           | Enter any comments. This is an optional entry.                                                                                                                                                                                                                                                                                                                                            |

|                |             | •                                                                                                                                                                                                                                                                                                                                                                                         |

UG-20252 | 2021.01.21

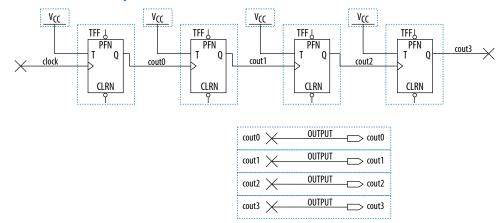

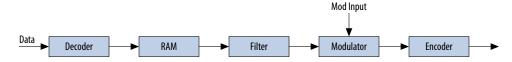

Figure 5. 4-Bit Counter Example

The cout0 output of the first TFF has a toggle percentage of 100% because the signal toggles on every clock cycle. The toggle percentage for the cout1 output of the second TFF is 50% because the output toggles every two clock cycles. Similarly, the toggle percentage for the cout2 and cout3 outputs are 25% and 12.5%, respectively. Therefore, the average toggle percentage for this 4-bit counter is (100 + 50 + 25 + 12.5)/4 = 46.875%.

For more information about logic block configurations, refer to the Intel Agilex Logic Array Blocks and Adaptive Logic Modules User Guide.

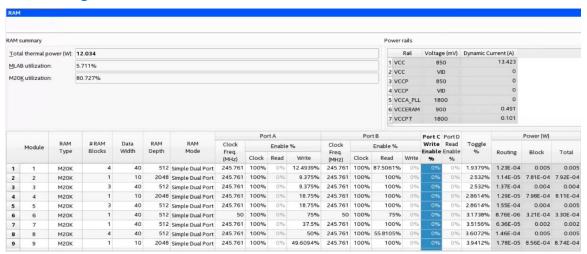

#### 4.6. Intel FPGA PTC - RAM Page

Each row in the RAM page of the Intel FPGA Power and Thermal Calculator (Intel FPGA PTC) represents a design module with RAM blocks of the same type, same data width, same RAM depth (if applicable), same RAM mode, and the same port parameters.

Each row in the RAM page of the Intel FPGA PTC represents a logical RAM module that you can implement using one or more physical RAM blocks. The Intel FPGA PTC implements each logical RAM module with the minimum number of physical RAM blocks, in the most power-efficient way possible, based on the specified logical width and depth.

You must know how your RAM is implemented by the Intel Quartus Prime Compiler when you are selecting the RAM block mode. For example, if a ROM is implemented with two ports, it is considered a true dual-port memory and not a ROM. Single-port and ROM implementations use only one port. Simple dual-port and true dual-port implementations use both Port A and Port B.

Note:

- The Power and Thermal Calculator reports MLAB power in the RAM page as described above, as well as in the Power Summary table.

- In the *Power Summary* table, the MLAB power for Intel Agilex devices is spread across three categories: RAM, Logic, and Miscellaneous; this is done to be consistent with the reporting provided in the Intel Quartus Prime Power Analyzer.

Figure 6. RAM Page of the Intel FPGA PTC

**Table 7. RAM Page Information**