# Intel<sup>®</sup> Quartus<sup>®</sup> Prime Pro Edition User Guide

# **Design Optimization**

Updated for Intel® Quartus® Prime Design Suite: 21.2

**UG-20133 | 2021.06.23**Latest document on the web: **PDF | HTML**

# **Contents**

| 1. | Design  | Optimization Overview                                                       | 6    |

|----|---------|-----------------------------------------------------------------------------|------|

|    | 1.1.    | Device Considerations                                                       | 6    |

|    |         | 1.1.1. Device Migration Considerations                                      | 6    |

|    | 1.2.    | Required Settings for Initial Compilation                                   | 7    |

|    |         | 1.2.1. Initial I/O Assignment Guidelines                                    | 7    |

|    |         | 1.2.2. Initial Timing Constraint Guidelines                                 | 7    |

|    | 1.3.    | Optimization Trade-Offs and Limitations                                     | 8    |

|    |         | 1.3.1. Area Reduction Trade-Offs                                            | 8    |

|    |         | 1.3.2. Critical Path Delay Reduction Trade-Offs                             | 8    |

|    |         | 1.3.3. Power Consumption Reduction Trade-Offs                               |      |

|    |         | 1.3.4. Compilation Time Trade-Offs                                          |      |

|    | 1.4.    | Design Visualization and Optimization Tools                                 |      |

|    |         | 1.4.1. Design Visualization Tools                                           |      |

|    |         | 1.4.2. Design Optimization Tools                                            |      |

|    | 1.5.    | Design Optimization Overview Revision History                               | 11   |

| 2. | Optimi  | zing the Design Netlist                                                     | . 13 |

|    | -       | When to Use the Netlist Viewers: Analyzing Design Problems                  |      |

|    |         | Intel Quartus Prime Design Flow with the Netlist Viewers                    |      |

|    |         | RTL Viewer Overview                                                         |      |

|    | 2.0.    | 2.3.1. Maximizing Readability in RTL Viewer                                 |      |

|    |         | 2.3.2. Running the RTL Viewer                                               |      |

|    | 2.4.    | Technology Map Viewer Overview                                              |      |

|    |         | Netlist Viewer User Interface                                               |      |

|    |         | 2.5.1. Netlist Navigator Pane                                               |      |

|    |         | 2.5.2. Properties Pane                                                      |      |

|    |         | 2.5.3. Netlist Viewers Find Pane                                            |      |

|    | 2.6.    | Schematic View                                                              | 22   |

|    |         | 2.6.1. Display Schematics in Multiple Tabbed View                           | 22   |

|    |         | 2.6.2. Schematic Symbols                                                    |      |

|    |         | 2.6.3. Select Items in the Schematic View                                   | 27   |

|    |         | 2.6.4. Shortcut Menu Commands in the Schematic View                         |      |

|    |         | 2.6.5. Filtering in the Schematic View                                      |      |

|    |         | 2.6.6. View Contents of Nodes in the Schematic View                         |      |

|    |         | 2.6.7. Moving Nodes in the Schematic View                                   |      |

|    |         | 2.6.8. View LUT Representations in the Technology Map Viewer                |      |

|    |         | 2.6.9. Zoom Controls                                                        |      |

|    |         | 2.6.10. Navigating with the Bird's Eye View                                 |      |

|    |         | 2.6.11. Partition the Schematic into Pages                                  |      |

|    |         | 2.6.12. Follow Nets Across Schematic Pages                                  |      |

|    | 2.7     | 2.6.13. Maintaining Selection in the Resource Property Viewer               |      |

|    |         | Cross-Probing to a Source Design File and Other Intel Quartus Prime Windows |      |

|    |         | Cross-Probing to the Netlist Viewers from Other Intel Quartus Prime Windows |      |

|    |         | Viewing a Timing Path                                                       |      |

|    |         | ). Optimizing the Design Netlist Revision History                           |      |

| 3. | Netlist | Optimizations and Physical Synthesis                                        | 38   |

|    |         | Physical Synthesis Ontimizations                                            | 38   |

|        |      | 3.1.1. Enabling Physical Synthesis Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|        |      | 3.1.2. Physical Synthesis Options                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |

|        | 3.2. | . Applying Netlist Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |

|        |      | 3.2.1. WYSIWYG Primitive Resynthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |

|        | 3.3. | . Scripting Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

|        |      | 3.3.1. Synthesis Netlist Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

|        |      | 3.3.2. Physical Synthesis Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |

|        | 3.4. | . Netlist Optimizations and Physical Synthesis Revision History                                                                                                                                                                                                                                                                                                                                                                                                                     | 42                                                  |

| 4. Ar  | ea O | ptimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44                                                  |

|        | 4.1. | . Resource Utilization Information                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 44                                                  |

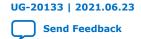

|        |      | 4.1.1. Flow Summary Report                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44                                                  |

|        |      | 4.1.2. Fitter Reports                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |

|        |      | 4.1.3. Analysis and Synthesis Reports                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |

|        |      | 4.1.4. Compilation Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |

|        | 4.2. | . Optimizing Resource Utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |

|        |      | 4.2.1. Resource Utilization Issues Overview                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |

|        |      | 4.2.2. I/O Pin Utilization or Placement                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46                                                  |

|        |      | 4.2.3. Logic Utilization or Placement                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |

|        |      | 4.2.4. Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |

|        | 4.3. | . Scripting Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

|        |      | 4.3.1. Initial Compilation Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

|        |      | 4.3.2. Resource Utilization Optimization Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

|        | 4.4. | . Area Optimization Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |

| 5. Tin | nina | Closure and Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56                                                  |

|        | _    | Optimize Multi Corner Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |

|        |      | Optimize Critical Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |

|        | 5.2. | 5.2.1. Viewing Critical Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                     |

|        | 5.3. | Optimize Critical Chains                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |

|        | 5.5. | 5.3.1. Viewing Critical Chains                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |

|        | 5.4. | . Design Evaluation for Timing Closure                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

|        | J    | 5.4.1. Review Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

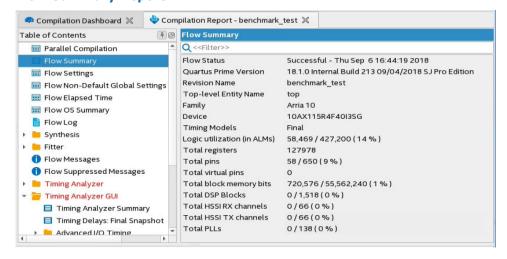

|        |      | 5.4.2. Evaluate Fitter Netlist Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |

|        |      | 5.4.3. Evaluate Optimization Results                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |

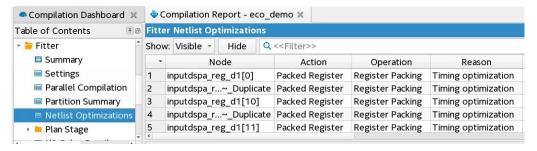

|        |      | 5.4.4. Evaluate Resource Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |

|        |      | 5.4.5. Evaluate Other Reports and Adjust Settings Accordingly                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                     |

|        |      | 5.4.6. Evaluate Clustering Difficulty                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |

|        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     |

|        |      | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64                                                  |

|        | 5.5. | 5.4.7. Revise and Recompile                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |

|        | 5.5. | 5.4.7. Revise and Recompile                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64                                                  |

|        | 5.5. | 5.4.7. Revise and Recompile                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64<br>64                                            |

|        | 5.5. | 5.4.7. Revise and Recompile                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64<br>64<br>66                                      |

|        | 5.5. | 5.4.7. Revise and Recompile                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64<br>64<br>66<br>68                                |

|        | 5.5. | 5.4.7. Revise and Recompile                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64<br>66<br>68<br>69                                |

|        | 5.5. | 5.4.7. Revise and Recompile                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64<br>66<br>68<br>69                                |

|        | 5.5. | 5.4.7. Revise and Recompile                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64<br>66<br>68<br>69<br>91<br>93                    |

|        | 5.5. | 5.4.7. Revise and Recompile Timing Optimization 5.5.1. Correct Design Assistant Rule Violations 5.5.2. Implement Fast Forward Timing Closure Recommendations 5.5.3. View Timing Optimization Advisor 5.5.4. Review Timing Path Details 5.5.5. Try Optional Fitter Settings 5.5.6. Back-Annotate Optimized Assignments 5.5.7. Optimize Settings with Design Space Explorer II                                                                                                        | 64<br>66<br>68<br>69<br>91<br>93                    |

|        | 5.5. | 5.4.7. Revise and Recompile Timing Optimization 5.5.1. Correct Design Assistant Rule Violations 5.5.2. Implement Fast Forward Timing Closure Recommendations 5.5.3. View Timing Optimization Advisor 5.5.4. Review Timing Path Details 5.5.5. Try Optional Fitter Settings 5.5.6. Back-Annotate Optimized Assignments 5.5.7. Optimize Settings with Design Space Explorer II 5.5.8. I/O Timing Optimization Techniques                                                              | 64<br>66<br>68<br>69<br>91<br>93<br>94              |

|        | 5.5. | 5.4.7. Revise and Recompile Timing Optimization 5.5.1. Correct Design Assistant Rule Violations 5.5.2. Implement Fast Forward Timing Closure Recommendations 5.5.3. View Timing Optimization Advisor 5.5.4. Review Timing Path Details 5.5.5. Try Optional Fitter Settings 5.5.6. Back-Annotate Optimized Assignments 5.5.7. Optimize Settings with Design Space Explorer II 5.5.8. I/O Timing Optimization Techniques 5.5.9. Register-to-Register Timing Optimization Techniques 1 | 64<br>66<br>68<br>69<br>91<br>93<br>94<br>97        |

|        |      | 5.4.7. Revise and Recompile Timing Optimization 5.5.1. Correct Design Assistant Rule Violations 5.5.2. Implement Fast Forward Timing Closure Recommendations 5.5.3. View Timing Optimization Advisor 5.5.4. Review Timing Path Details 5.5.5. Try Optional Fitter Settings 5.5.6. Back-Annotate Optimized Assignments 5.5.7. Optimize Settings with Design Space Explorer II 5.5.8. I/O Timing Optimization Techniques                                                              | 64<br>66<br>68<br>69<br>91<br>93<br>94<br>97<br>.02 |

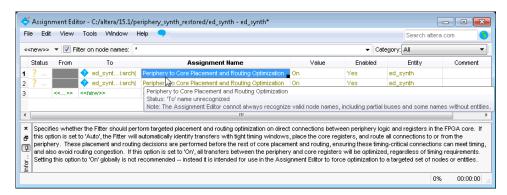

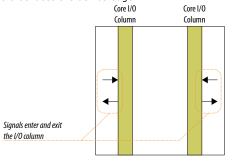

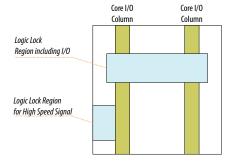

|       | 5.6.1          | . Setting Periphery to Core Optimizations in the Advanced Fitter Setting Dialog Box     | 117 |

|-------|----------------|-----------------------------------------------------------------------------------------|-----|

|       | F 6 2          | 2. Setting Periphery to Core Optimizations in the Assignment Editor                     |     |

|       |                |                                                                                         |     |

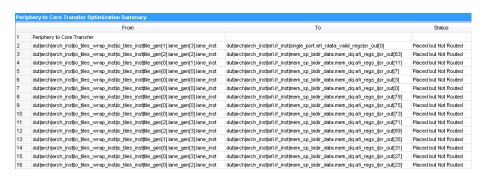

|       |                | 3. Viewing Periphery to Core Optimizations in the Fitter Reportng Support               |     |

|       |                | In Support                                                                              |     |

|       |                | 2. I/O Timing Optimization Techniques                                                   |     |

|       |                | 8. Register-to-Register Timing Optimization Techniques                                  |     |

|       |                | Closure and Optimization Revision History                                               |     |

|       | _              | ·                                                                                       |     |

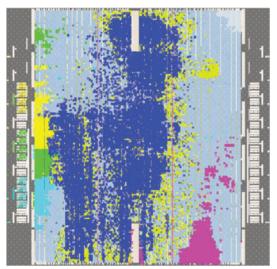

| 6. An |                | l Optimizing the Design Floorplan                                                       |     |

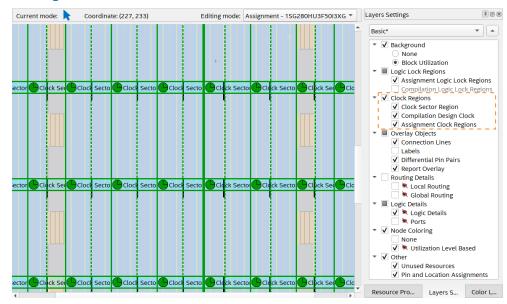

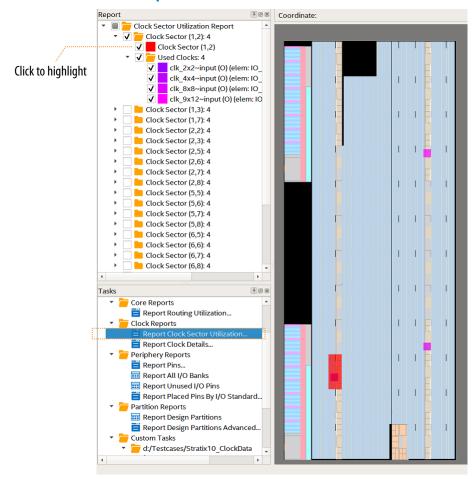

|       |                | Floorplan Analysis in the Chip Planner                                                  |     |

|       |                | Starting the Chip Planner                                                               |     |

|       |                | 2. Chip Planner GUI Components                                                          |     |

|       |                | 3. Viewing Design Elements in the Chip Planner                                          |     |

|       |                | I. Exploring Paths in the Chip Planner                                                  |     |

|       |                | 5. Viewing Assignments in the Chip Planner                                              |     |

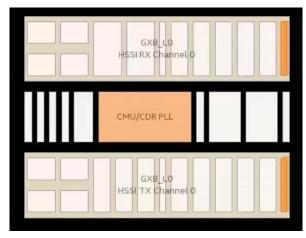

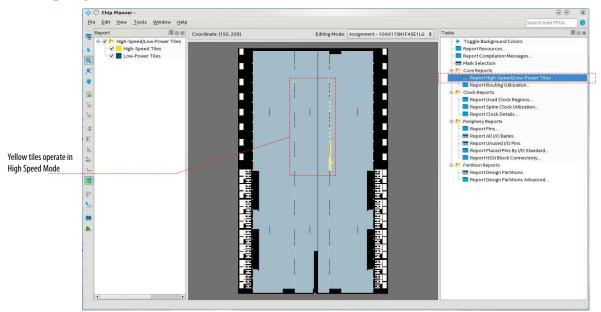

|       |                | 5. Viewing High-Speed and Low-Power Tiles in the Chip Planner                           | 139 |

|       |                | ng Partitions and Logic Lock Regions with the Design Partition Planner and Chip Planner | 139 |

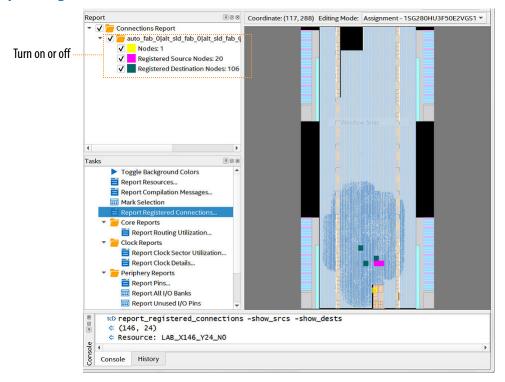

|       |                | . Viewing Design Connectivity and Hierarchy                                             |     |

|       |                | Logic Lock Regions in the Chip Planner                                                  |     |

|       |                | Viewing Connections Between Logic Lock Regions in the Chip Planner                      |     |

|       |                | B. Logic Lock Regions                                                                   |     |

|       |                | I. Attributes of a Logic Lock Region                                                    |     |

|       |                | 5. Migrating Assignments between Intel Quartus Prime Standard Edition and               |     |

|       |                | Intel Quartus Prime Pro Edition                                                         |     |

|       | 6.3.6          | 5. Creating Logic Lock Regions                                                          |     |

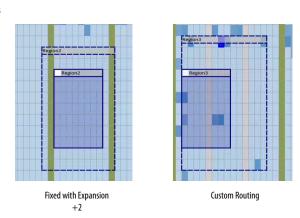

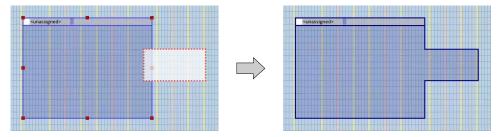

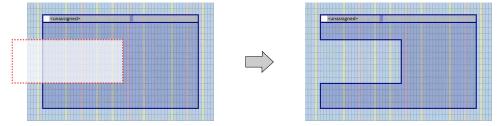

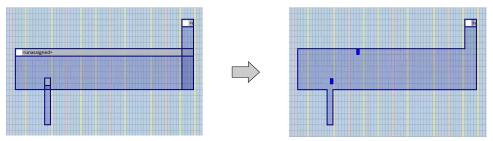

|       |                | 7. Customizing the Shape of Logic Lock Regions                                          |     |

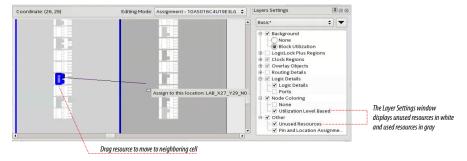

|       |                | B. Placing Device Resources into Logic Lock Regions                                     |     |

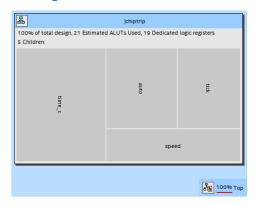

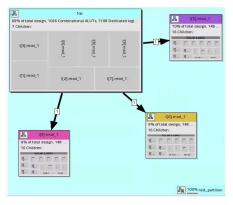

|       | 6.3.9          | 9. Hierarchical Regions                                                                 | 152 |

|       | 6.3.1          | .0. Additional Intel Quartus Prime Logic Lock Design Features                           | 152 |

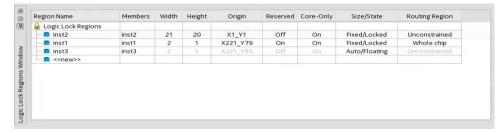

|       | 6.3.1          | 1. Logic Lock Regions Window                                                            | 152 |

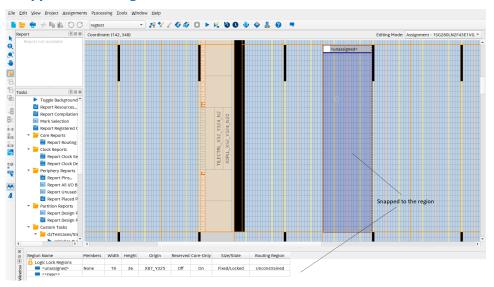

|       | 6.3.1          | .2. Snapping to a Region                                                                | 153 |

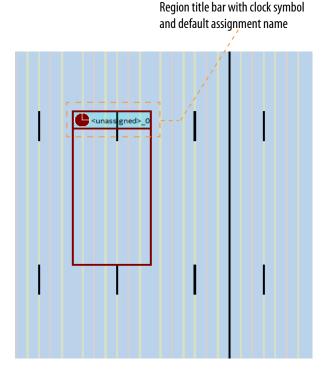

|       | 6.4. Using L   | Jser-Defined Clock Regions in the Chip Planner                                          | 154 |

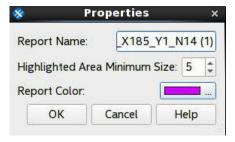

|       | 6.4.1          | . Creating Clock Assignments with the Chip Planner                                      | 155 |

|       | 6.4.2          | 2. Resizing a Clock Assignment                                                          | 156 |

|       | 6.4.3          | B. Moving a Clock Assignment                                                            | 156 |

|       | 6.4.4          | I. Deleting a Clock Region Assignment                                                   | 156 |

|       | 6.4.5          | 5. Assigning a Clock Signal to a Clock Region                                           | 157 |

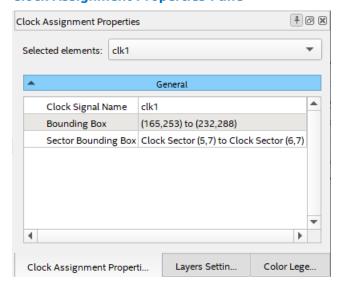

|       |                | 5. Clock Assignment Properties                                                          |     |

|       | 6.5. Scripting | ng Support                                                                              | 158 |

|       | 6.5.1          | Creating Logic Lock Assignments with Tcl commands                                       | 158 |

|       | 6.5.2          | 2. Assigning Virtual Pins with a Tcl command                                            | 159 |

|       | 6.5.3          | B. Logic Lock Region Assignment Examples                                                | 159 |

|       | 6.6. Analyzi   | ing and Optimizing the Design Floorplan Revision History                                | 160 |

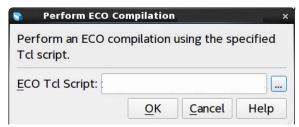

| 7. Us | ing the ECO    | Compilation Flow                                                                        | 163 |

|       | 7.1. ECO Co    | ompilation Flow                                                                         | 163 |

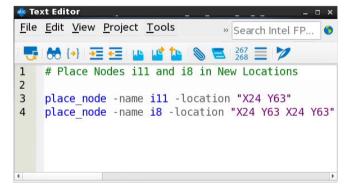

|       | 7.2. ECO Tc    | Script Example                                                                          | 164 |

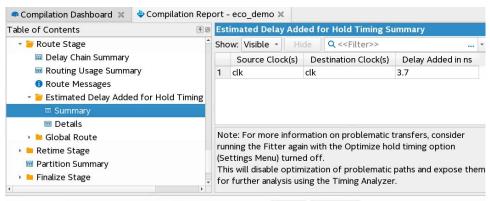

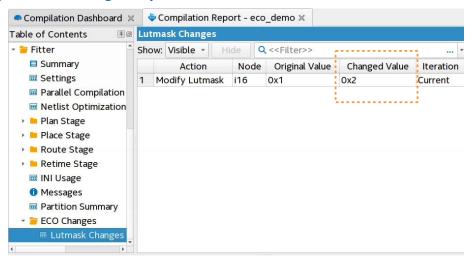

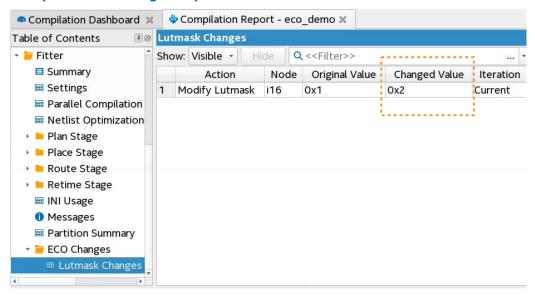

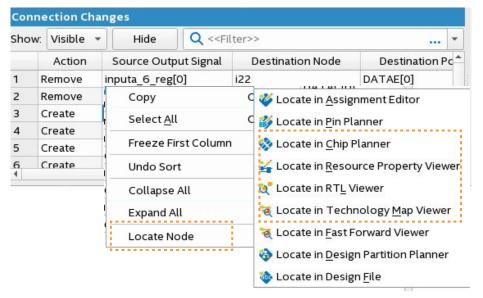

|       | 7.3. Viewing   | g ECO Compilation Reports                                                               | 165 |

|       | 7.4 ECO C      |                                                                                         | 166 |

#### Contents

| 7.4.1. ECO Command Quick Reference                                         | 167 |

|----------------------------------------------------------------------------|-----|

| 7.4.2. make_connection                                                     | 167 |

| 7.4.3. remove_connection                                                   |     |

| 7.4.4. modify_lutmask                                                      |     |

| 7.4.5. adjust_pll_refclk                                                   |     |

| 7.4.6. modify_io_slew_rate                                                 |     |

| 7.4.7. modify_io_current_strength                                          | 170 |

| 7.4.8. modify_io_delay_chain                                               | 170 |

| 7.4.9. create_new_node                                                     |     |

| 7.4.10. remove_node                                                        | 172 |

| 7.4.11. place_node                                                         | 172 |

| 7.4.12. unplace_node                                                       | 173 |

| 7.4.13. create_wirelut                                                     | 173 |

| 7.5. ECO Command Limitations                                               | 174 |

| 7.6. Interactive ECO Fitting                                               | 175 |

| 7.6.1. eco_load_design and eco_commit_design Commands                      | 175 |

| 7.7. Using the ECO Compilation Flow Revision History                       | 176 |

| 8. Intel Quartus Prime Pro Edition Design Optimization User Guide Archives | 177 |

| A. Intel Quartus Prime Pro Edition User Guides                             | 178 |

# 1. Design Optimization Overview

The early stages of FPGA design development typically focus on meeting timing requirement, resource usage, and power consumption goals. After meeting those basic goals, you can focus on optimizing performance.

Optimization of FPGA design performance requires a multi-dimensional approach to meet the design goals, while also reducing area, critical path delay, power consumption, and runtime. The Intel® Quartus® Prime software supports various tools and techniques for performance optimization.

This chapter describes the techniques and tools in the Intel Quartus Prime software that you can use to meet your design goals and achieve the highest design performance in Intel FPGAs.

#### **Related Information**

Compilation Flows, Intel Quartus Prime Pro Edition User Guide: Design Compilation

#### 1.1. Device Considerations

All Intel FPGAs have a unique timing model that contains delay information for all physical elements in the device, such as combinational adaptive logic modules, memory blocks, interconnects, and registers. The delays encompass all valid combinations of operating conditions for the target FPGA. Additionally, the device size and package determine pin-out and the resource availability. When selecting the target Intel FPGA device for your design, consider the performance specifications of the device.

#### 1.1.1. Device Migration Considerations

If you anticipate a change to the target device later in the design cycle, plan for the migration from the beginning of cycle. This strategy helps to minimize changes to the design at a later stage.

When choosing a design's target device in the Intel Quartus Prime software, you can see a list of compatible devices by clicking the **Migration Devices** button in the **Device** dialog box.

#### **Related Information**

Migration Devices Dialog Box In Intel Quartus Prime Help

# 1.2. Required Settings for Initial Compilation

Compilation results can vary significantly, depending on the assignments and settings that you choose. In the Intel Quartus Prime software, the default values for timing settings provide the best trade-off between compilation time, resource utilization, and timing performance. You can adjust these settings if you want to further optimize for compile time, resource utilization, or timing performance. Before compiling a design in the Intel Quartus Prime software, consider the following guidelines for specifying initial settings.

# 1.2.1. Initial I/O Assignment Guidelines

In a FPGA design, I/O standards and drive strengths affect I/O timing. Follow these guidelines when specifying initial I/O assignments:

- When specifying I/O assignments, make sure that the Intel Quartus Prime software is using an accurate I/O timing delay for timing analysis and Fitter optimizations.

- If the PCB layout does not indicate pin locations, then leave the pin locations unconstrained. This technique allows the Compiler to search for the best layout. Otherwise, make pin assignments to constrain the compilation appropriately.

#### **Related Information**

I/O Planning Overview

In Intel Quartus Prime Pro Edition User Guide: Design Constraints

# 1.2.2. Initial Timing Constraint Guidelines

For best results, use realistic timing requirements for initial compilation. Applying more stringent timing requirements than the design requires can cause the Compiler to increase performance at the expense of resource usage, power utilization, or compilation time.

Specifying comprehensive timing requirement settings helps you to achieve the best results for the following reasons:

- Comprehensive timing assignments enable the Compiler to work hardest to

optimize the performance of the timing-critical parts of the design. This

optimization can also save area or power utilization in non-critical parts of the

design.

- If enabled, the Intel Quartus Prime software can performs physical synthesis optimizations based on the comprehensive timing requirements.

Following compilation and timing analysis, the Compilation Report reports whether the design meets the timing requirements. You can then use the Intel Quartus Prime Timing Analyzer reporting commands to provide detailed information about all timing paths.

#### **Related Information**

- Using the Intel Quartus Prime Timing Analyzer

In Intel Quartus Prime Pro Edition User Guide: Timing Analyzer

- Intel Quartus Prime Timing Analyzer Cookbook

# 1.3. Optimization Trade-Offs and Limitations

Design optimization is often a trade-off between performance, resource usage, power utilization, and compilation time. You can apply various settings to achieve the correct balance of these factors for your design goals.

**Table 1.** Design Optimization Trade-Off Examples

| Trade-off                                                                      | Comments                                                                                                                                                         |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Resource usage and critical path timing.                                       | Certain techniques (such as logic duplication) can improve timing performance at the cost of increased area.                                                     |

| Power requirements can result in area and timing trade-offs.                   | For example, reducing the number of available high-speed tiles, or attempting to shorten high-power nets at the expense of critical path nets.                   |

| System cost and time-to-market considerations can affect the choice of device. | For example, a device with a higher speed grade or more clock networks can facilitate timing closure at the expense of higher power consumption and system cost. |

Finally, constraints that are too stringent can produce a situation with no possible solution for the selected device. If the Fitter cannot resolve a design due to resource limitations, timing constraints, or power constraints, consider rewriting parts of the HDL code.

#### 1.3.1. Area Reduction Trade-Offs

By default, the Intel Quartus Prime Fitter might physically spread a design over the entire device to meet the set timing constraints. If you prefer to optimize your design to use the smallest area, you can change this behavior. If you require reduced area, you can enable certain physical synthesis options to modify your netlist to create a more area-efficient implementation, but at the cost of increased runtime and decreased performance.

#### **Related Information**

- Area Optimization on page 44

- Netlist Optimizations and Physical Synthesis on page 38

# 1.3.2. Critical Path Delay Reduction Trade-Offs

To meet complex timing requirements involving multiple clocks, routing resources, and area constraints, the Intel Quartus Prime software offers a close interaction between synthesis, floorplan editing, place-and-route, and timing analysis processes.

By default, the Intel Quartus Prime Fitter works to meet the timing requirements, and stops when the requirements are met. Therefore, specifying realistic constraints is crucial for timing closure.

Under-constrained designs can lead to sub-optimal results. For over-constrained designs, the Fitter might over-optimize non-critical paths at the expense of true critical paths. In addition, area and compilation time may also increase.

For designs with high resource usage, the Intel Quartus Prime Fitter might have trouble finding a legal placement. In such circumstances, the Fitter automatically modifies settings to try to trade off performance for area.

UG-20133 | 2021.06.23

The Intel Quartus Prime Fitter offers advanced options that can help improve the design performance when you properly set constraints. Use the Timing Optimization Advisor to determine which options are best suited for the design.

In high-density FPGAs, routing accounts for a major part of critical path timing. Because of this, duplicating or retiming logic can allow the Fitter to reduce delay on critical paths. The Intel Quartus Prime software offers push-button netlist optimizations and physical synthesis options that can improve design performance at the expense of considerable increases of compilation time and area. Turn on only those options that help you keep reasonable compilation times and resource usage. Alternately, you can modify the HDL to manually duplicate or adjust the timing logic.

#### **Related Information**

Optimize Critical Paths on page 56

# 1.3.3. Power Consumption Reduction Trade-Offs

The Intel Quartus Prime software has features that help reduce design power consumption. The power optimization options control the power-driven compilation settings for Synthesis and the Fitter. You can adjust these settings

#### **Related Information**

**Power Optimization**

In Intel Quartus Prime Pro Edition User Guide: Power Analysis and Optimization

## 1.3.4. Compilation Time Trade-Offs

Many Fitter settings influence compilation time. Most of the default settings in the Intel Quartus Prime software are set for reduced compilation time. You can modify these settings for your project requirements to trade-off longer compilation time for increased performance.

The Intel Quartus Prime software supports parallel compilation in computers with multiple processors. This technique can reduce compilation times by up to 15%.

#### **Related Information**

Reducing Compilation Time, Intel Quartus Prime Pro Edition User Guide: Design Compilation

# 1.4. Design Visualization and Optimization Tools

The Intel Quartus Prime software provides various tools to help you visualize and optimize the design settings and constraints for the best design implementation.

#### 1.4.1. Design Visualization Tools

The Intel Quartus Prime software provides tools that display different graphical representations of your design to help you visualize and optimize placement, connectivity, and routing congestion at various stages of the design cycle.

**Table 2.** Design Visualization Tools

| Tool                                         | Description                                                                                                                                                                                                                                                               |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTL Viewer                                   | Provides a schematic representation of the design before synthesis and place-and-route.                                                                                                                                                                                   |

| Technology Map Viewer                        | Provides a schematic representation of the design implementation in the selected device architecture after synthesis and place-and-route. Optionally, you can include timing information.                                                                                 |

| Chip Planner                                 | Allows you to make floorplan assignments, perform power analysis, and visualize critical paths and routing congestion.                                                                                                                                                    |

| Interface Planner                            | Simplifies the planning of accurate constraints for physical implementation. Use Interface Planner to prototype interface implementations, plan clocks, and rapidly define a legal device floorplan.                                                                      |

| State Machine Viewer                         | Presents a high-level, graphical view of finite state machines in your design. The viewer displays the states and their related transitions, as well as a state transition table with condition equations for state transitions, and encoding information for each state. |

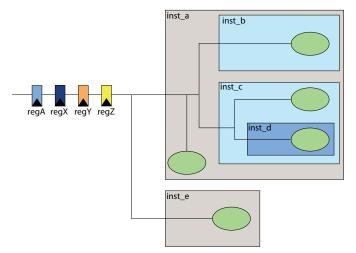

| Design Partition Planner                     | Displays design entities, I/O banks, connectivity, design hierarchy, and design partition membership. Design Partition Planner can assist you in visualizing a design's structure for creating effective design partitions.                                               |

| Design Partition Planner and Chip<br>Planner | Allows you to partition and layout the design at a higher level chip view.                                                                                                                                                                                                |

#### **Related Information**

- Design Floorplan Analysis in the Chip Planner on page 125

- Creating Partitions and Logic Lock Regions with the Design Partition Planner and the Chip Planner on page 139

- RTL Viewer Overview on page 15

- Technology Map Viewer Overview on page 16

- State Machine Viewer Overview

- Interface Planning, Intel Quartus Prime Pro Edition User Guide: Design Constraints

# 1.4.2. Design Optimization Tools

The Intel Quartus Prime software provides tools help you identify design RTL and project settings that potentially limit performance.

**Table 3. Design Optimization Tools**

| Tool                                           | Description                                                                                                                                                                                                                                                                                                                        | To Access                                                                        |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

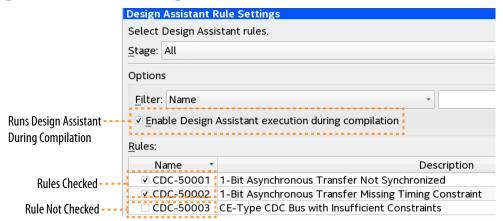

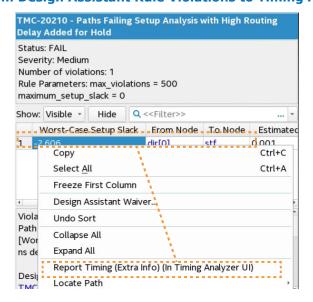

| Design Assistant                               | Automatically reports any violations against a standard set of Intel FPGA-recommended design guidelines, as Correct Design Assistant Rule Violations on page 64 describes.                                                                                                                                                         | Assignments ➤ Settings ➤ Design Assistant Rule Settings                          |

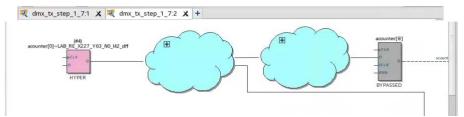

| Fast Forward Timing Closure<br>Recommendations | Fast Forward compilation generates design recommendations to help you to break performance bottlenecks and maximize use of Hyper-Registers to drive the highest performance in Intel Stratix <sup>®</sup> 10 and Intel Agilex <sup>™</sup> designs, as Implement Fast Forward Timing Closure Recommendations on page 66 describes. | On the Compilation Dashboard, click Fast Forward Timing Closure Recommendations. |

|                                                |                                                                                                                                                                                                                                                                                                                                    | continued                                                                        |

| Tool                                     | Description                                                                                                                                                                                                                                                    | To Access                                                                                                   |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

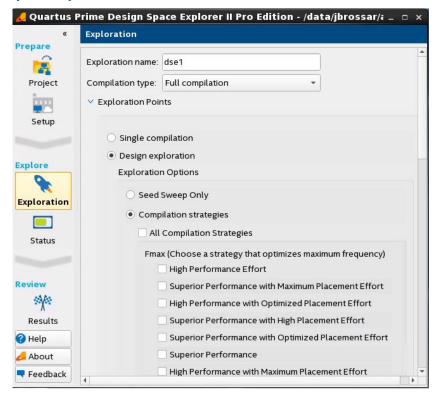

| Design Space Explorer II                 | Provides an easy and efficient way to run seed sweeps with different combinations of design settings and constraints to identify the optimal combination for your design, as Optimize Settings with Design Space Explorer II on page 94 describes.             | Tools ➤ Launch Design<br>Space Explorer II                                                                  |

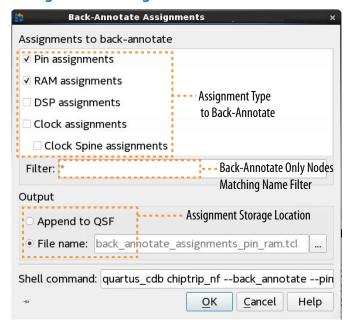

| Assignment Back-Annotation<br>Dialog Box | Back-annotation copies the last compilation's resource assignments to preserve your optimized implementation in subsequent compilations, as Back-Annotate Optimized Assignments on page 93 describes.                                                          | Assignments ➤ Back-<br>Annotate Assignments                                                                 |

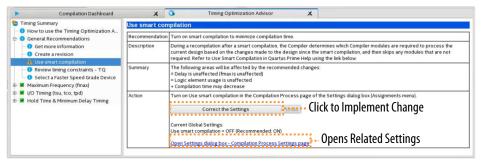

| Design Advisors                          | Provide recommendations about your current project settings and constraints. Consider the recommendations to optimize fitting, meet timing or power requirements, or improve the design performance, as View Timing Optimization Advisor on page 68 describes. | Click Tools ➤ Advisors >  Timing Optimization Advisor  Power Optimization Advisor  Compilation Time Advisor |

# **Related Information**

- Fast Forward Compilation, Intel Quartus Prime Pro Edition User Guide: Design Compilation

- Design Assistant, Intel Quartus Prime Pro Edition User Guide: Design Recommendations

# 1.5. Design Optimization Overview Revision History

The following revision history applies to this chapter:

| Document Version | Intel Quartus Prime Version | Changes                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2020.09.28       | 20.3.0                      | Reorganized "Design Optimization Tools" section.  Added references to Design Assistant, Fast Forward Timing Closure Recommendations, and assignment back-annotation to "Design Optimization Tools" topic.  Added Interface Planner and State Machine Viewer to list of "Design Visualization Tools".  Reworded titles in "Optimization Trade-Offs and Limitations" section for greater clarity. |

| 2018.05.07       | 18.0.0                      | General topic reorganization.     Added how DSE II works, and the main steps to follow when performing a design exploration.                                                                                                                                                                                                                                                                    |

| 2017.11.06       | 17.1.0                      | Added mention to the Design Partition Planner in Design Analysis topic.                                                                                                                                                                                                                                                                                                                         |

| 2016.10.31       | 16.1.0                      | Implemented Intel rebranding.                                                                                                                                                                                                                                                                                                                                                                   |

| 2016.05.03       | 16.0.0                      | Removed statements about serial equivalence when using multiple processors.                                                                                                                                                                                                                                                                                                                     |

| 2015.11.02       | 15.1.0                      | Changed instances of <i>Quartus II</i> to <i>Quartus Prime</i> .                                                                                                                                                                                                                                                                                                                                |

| 2014.12.15       | 14.1.0                      | <ul> <li>Updated location of Fitter Settings, Analysis &amp; Synthesis Settings, and<br/>Physical Synthesis Optimizations to Compiler Settings.</li> <li>Updated DSE II content.</li> </ul>                                                                                                                                                                                                     |

| June 2014        | 14.0.0                      | Updated format.                                                                                                                                                                                                                                                                                                                                                                                 |

| November 2013    | 13.1.0                      | Minor changes for HardCopy.                                                                                                                                                                                                                                                                                                                                                                     |

|                  | <u>'</u>                    | continued                                                                                                                                                                                                                                                                                                                                                                                       |

| Document Version | Intel Quartus Prime Version | Changes                                                                                                                                                                                                                                    |

|------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2013         | 13.0.0                      | Added the information about initial compilation requirements. This section was moved from the Area Optimization chapter of the Intel Quartus Prime Handbook. Minor updates to delineate division of Timing and Area optimization chapters. |

| June 2012        | 12.0.0                      | Removed survey link.                                                                                                                                                                                                                       |

| November 2011    | 10.0.3                      | Template update.                                                                                                                                                                                                                           |

| December 2010    | 10.0.2                      | Changed to new document template. No change to content.                                                                                                                                                                                    |

| August 2010      | 10.0.1                      | Corrected link                                                                                                                                                                                                                             |

| July 2010        | 10.0.0                      | Initial release. Chapter based on topics and text in Section III of volume 2.                                                                                                                                                              |

# 2. Optimizing the Design Netlist

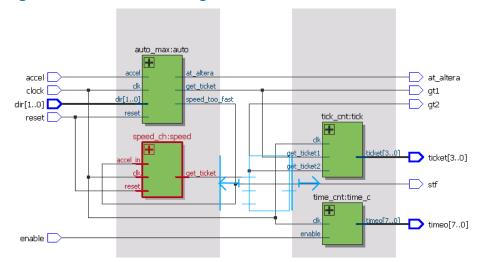

This chapter describes how you can use the Intel Quartus Prime Netlist Viewers to analyze and debug your designs.

As FPGA designs grow in size and complexity, the ability to analyze, debug, optimize, and constrain your design is critical. With today's advanced designs, several design engineers are involved in coding and synthesizing different design blocks, making it difficult to analyze and debug the design. The Intel Quartus Prime RTL Viewer and Technology Map Viewer provide powerful ways to view your initial and fully mapped synthesis results during the debugging, optimization, and constraint entry processes.

#### **Related Information**

- Intel Quartus Prime Design Flow with the Netlist Viewers on page 14

- RTL Viewer Overview on page 15

- Technology Map Viewer Overview on page 16

- Filtering in the Schematic View on page 28

- Viewing a Timing Path on page 36

# 2.1. When to Use the Netlist Viewers: Analyzing Design Problems

You can use the Netlist Viewers to analyze and debug your design. The following simple examples show how to use the RTL Viewer and Technology Map Viewer to analyze problems encountered in the design process.

Using the RTL Viewer is a good way to view your initial synthesis results to determine whether you have created the necessary logic, and that the logic and connections have been interpreted correctly by the software. You can use the RTL Viewer to check your design visually before simulation or other verification processes. Catching design errors at this early stage of the design process can save you valuable time.

If you see unexpected behavior during verification, use the RTL Viewer to trace through the netlist and ensure that the connections and logic in your design are as expected. Viewing your design helps you find and analyze the source of design problems. If your design looks correct in the RTL Viewer, you know to focus your analysis on later stages of the design process and investigate potential timing violations or issues in the verification flow itself.

You can use the Technology Map Viewer to look at the results at the end of Analysis and Synthesis. If you have compiled your design through the Fitter stage, you can view your post-mapping netlist in the Technology Map Viewer (Post-Mapping) and your post-fitting netlist in the Technology Map Viewer. If you perform only Analysis and Synthesis, both the Netlist Viewers display the same post-mapping netlist.

In addition, you can use the RTL Viewer or Technology Map Viewer to locate the source of a particular signal, which can help you debug your design. Use the navigation techniques described in this chapter to search easily through your design. You can trace back from a point of interest to find the source of the signal and ensure the connections are as expected.

The Technology Map Viewer can help you locate post-synthesis nodes in your netlist and make assignments when optimizing your design. This functionality is useful when making a multicycle clock timing assignment between two registers in your design. Start at an I/O port and trace forward or backward through the design and through levels of hierarchy to find nodes of interest, or locate a specific register by visually inspecting the schematic.

Throughout your FPGA design, debug, and optimization stages, you can use all of the netlist viewers in many ways to increase your productivity while analyzing a design.

#### **Related Information**

- Intel Quartus Prime Design Flow with the Netlist Viewers on page 14

- RTL Viewer Overview on page 15

- Technology Map Viewer Overview on page 16

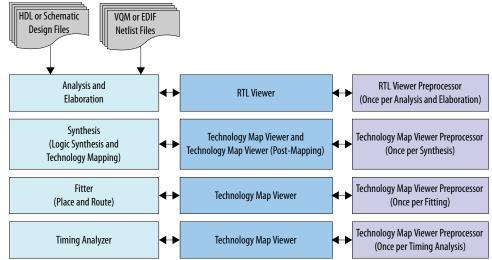

# 2.2. Intel Quartus Prime Design Flow with the Netlist Viewers

When you first open one of the Netlist Viewers after compiling the design, a preprocessor stage runs automatically before the Netlist Viewer opens.

Click the link in the preprocessor process box to go to the **Settings** > **Compilation Process Settings** page where you can turn on the **Run Netlist Viewers preprocessing during compilation** option. If you turn this option on, the preprocessing becomes part of the full project compilation flow and the Netlist Viewer opens immediately without displaying the preprocessing dialog box.

# Figure 1. Intel Quartus Prime Design Flow Including the RTL Viewer and Technology Map Viewer

This figure shows how Netlist Viewers fit into the basic Intel Quartus Prime design flow.

UG-20133 | 2021.06.23

Before the Netlist Viewer can run the preprocessor stage, you must compile your design:

- To open the RTL Viewer first perform Analysis and Elaboration.

- To open the Technology Map Viewer (Post-Fitting) or the Technology Map Viewer (Post-Mapping), first perform Analysis and Synthesis.

The Netlist Viewers display the results of the last successful compilation.

- Therefore, if you make a design change that causes an error during Analysis and Elaboration, you cannot view the netlist for the new design files, but you can still see the results from the last successfully compiled version of the design files.

- If you receive an error during compilation and you have not yet successfully run the appropriate compilation stage for your project, the Netlist Viewer cannot be displayed; in this case, the Intel Quartus Prime software issues an error message when you try to open the Netlist Viewer.

Note:

If the Netlist Viewer is open when you start a new compilation, the Netlist Viewer closes automatically. You must open the Netlist Viewer again to view the new design netlist after compilation completes successfully.

#### 2.3. RTL Viewer Overview

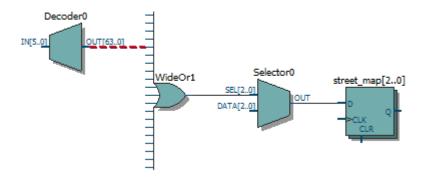

The RTL Viewer allows you to view a register transfer level (RTL) graphical representation of Intel Quartus Prime Pro Edition synthesis results or third-party netlist files in the Intel Quartus Prime software.

You can view results after Analysis and Elaboration for designs that use any supported Intel Quartus Prime design entry method, including Verilog HDL Design Files (.v), SystemVerilog Design Files (.sv), VHDL Design Files (.vhd), AHDL Text Design Files (.tdf), or schematic Block Design Files (.bdf).

You can also view the hierarchy of atom primitives (such as device logic cells and I/O ports) for designs that generate Verilog Quartus Mapping File (.vqm) or Electronic Design Interchange Format (.edf) files through a synthesis tool.

The RTL Viewer displays a schematic view of the design netlist after Analysis and Elaboration or after the Intel Quartus Prime software performs netlist extraction, but before technology mapping and synthesis or fitter optimizations. This view a preliminary pre-optimization design structure and closely represents the original source design.

- For designs synthesized with the Intel Quartus Prime Pro Edition synthesis, this view shows how the Intel Quartus Prime software interprets the design files.

- For designs synthesized with a third-party synthesis tool, this view shows the netlist that the synthesis tool generates.

To run the RTL Viewer for an Intel Quartus Prime project, first analyze the design to generate an RTL netlist. To analyze the design and generate an RTL netlist, click **Processing** > **Start** > **Start Analysis & Elaboration**. You can also perform a full compilation on any process that includes the initial Analysis and Elaboration stage of the Intel Quartus Prime compilation flow.

To open the RTL Viewer, click **Tools** ➤ **Netlist Viewers** ➤ **RTL Viewer**.

#### **Related Information**

Netlist Viewer User Interface on page 17

# 2.3.1. Maximizing Readability in RTL Viewer

While displaying a design, the RTL Viewer optimizes the netlist to maximize readability:

- Removes logic with no fan-out (unconnected output) or fan-in (unconnected inputs) from the display.

- Hides default connections such as V<sub>CC</sub> and GND.

- Groups pins, nets, wires, module ports, and certain logic into buses where appropriate.

- Groups constant bus connections.

- Displays values in hexadecimal format.

- Converts NOT gates into bubble inversion symbols in the schematic.

- Merges chains of equivalent combinational gates into a single gate; for example, a 2-input AND gate feeding a 2-input AND gate is converted to a single 3-input AND gate.

# 2.3.2. Running the RTL Viewer

To run the RTL Viewer for an Intel Quartus Prime project:

Analyze the design to generate an RTL netlist by clicking Processing ➤ Start ➤ Start Analysis & Elaboration.

You can also perform a full compilation on any process that includes the initial Analysis and Elaboration stage of the Intel Quartus Prime compilation flow.

2. Open the RTL Viewer by clicking **Tools** ➤ **Netlist Viewers** ➤ **RTL Viewer**.

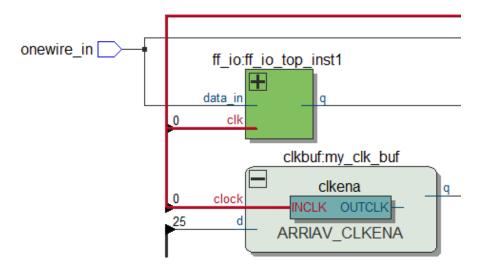

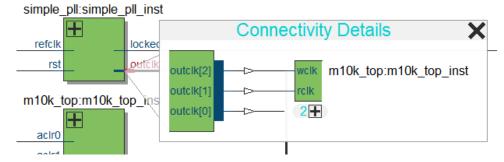

# 2.4. Technology Map Viewer Overview

The Intel Quartus Prime Technology Map Viewer provides a technology-specific, graphical representation of FPGA designs after Analysis and Synthesis or after the Fitter maps the design into the target device.

The Technology Map Viewer shows the hierarchy of atom primitives (such as device logic cells and I/O ports) in the design. For supported device families, you can also view internal registers and look-up tables (LUTs) inside logic cells (LCELLs), and registers in I/O atom primitives.

Where possible, the Intel Quartus Prime software maintains the port names of each hierarchy throughout synthesis. However, the software may change or remove port names from the design. For example, the software removes ports that are unconnected or driven by GND or  $V_{CC}$  during synthesis. If a port name changes, the software assigns a related user logic name in the design or a generic port name such as IN1 or OUT1.

You can view Intel Quartus Prime technology-mapped results after synthesis, fitting, or timing analysis. To run the Technology Map Viewer for an Intel Quartus Prime project, on the **Processing** menu, point to **Start** and click **Start Analysis & Synthesis** to synthesize and map the design to the target technology. At this stage,

UG-20133 | 2021.06.23

the Technology Map Viewer shows the same post-mapping netlist as the Technology Map Viewer (Post-Mapping). You can also perform a full compilation, or any process that includes the synthesis stage in the compilation flow.

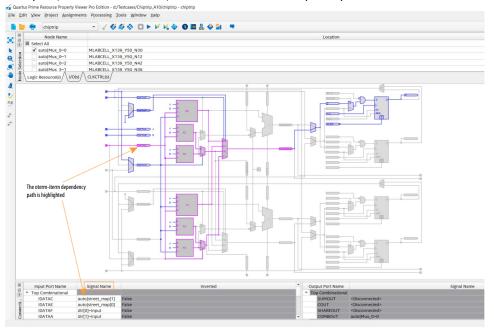

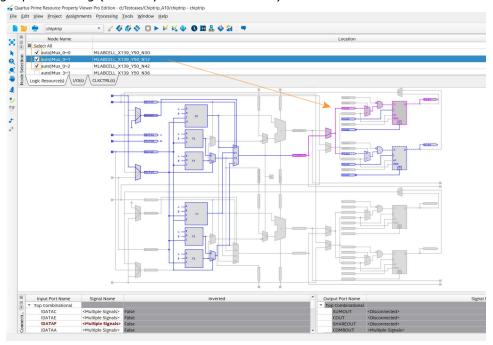

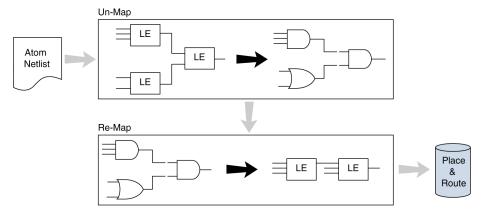

For designs that completed the Fitter stage, the Technology Map Viewer shows how the Fitter changed the netlist through physical synthesis optimizations, while the Technology Map Viewer (Post-Mapping) shows the post-mapping netlist. If you have completed the Timing Analysis stage, you can locate timing paths from the Timing Analyzer report in the Technology Map Viewer.

To open the Technology Map Viewer, click **Tools** ➤ **Netlist Viewers** ➤ **Technology Map Viewer (Post-Fitting)** or **Technology Map Viewer (Post Mapping)**.

#### **Related Information**

- Viewing a Timing Path on page 36

- View Contents of Nodes in the Schematic View on page 28

- Netlist Viewer User Interface on page 17

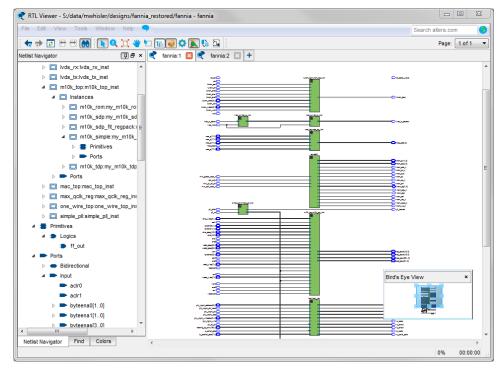

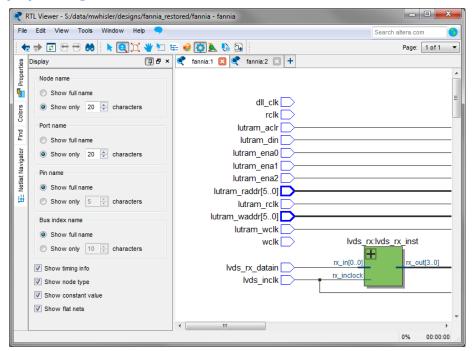

# 2.5. Netlist Viewer User Interface

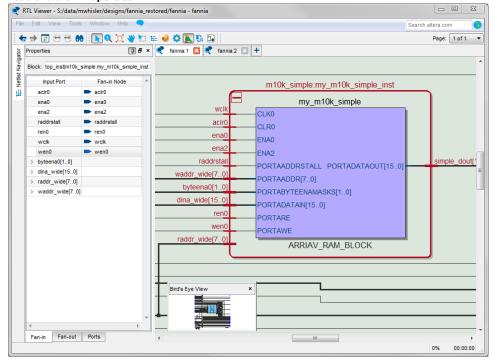

The Netlist Viewer is a graphical user-interface for viewing and manipulating nodes and nets in the netlist.

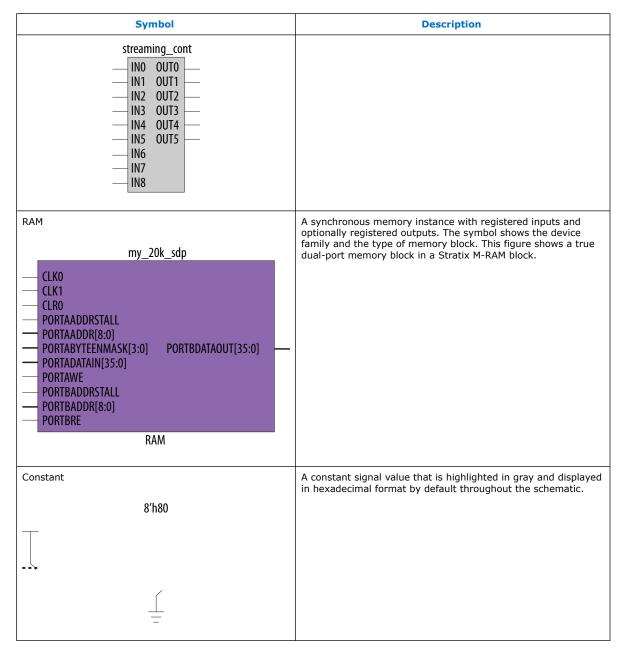

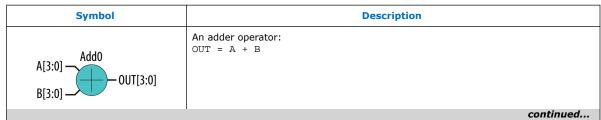

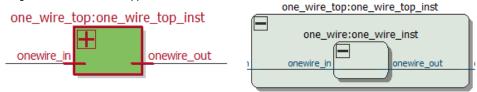

The RTL Viewer and Technology Map Viewer each consist of these main parts:

- The Netlist Navigator pane—displays a representation of the project hierarchy.

- The **Find** pane—allows you to find and locate specific design elements in the schematic view.

- The **Properties** pane displays the properties of the selected block when you select **Properties** from the shortcut menu.