# SDI IP コアのユーザーガイド

インテル® Quartus® Prime 開発デザインスイートの更新情報: 19.1

この翻訳版は参照用であり、翻訳版と英語版の内容に相違がある場合は、英語版が優先されるものとします。翻訳版は、 資料によっては英語版の更新に対応していない場合があります。最新情報につきましては、必ず<mark>英語版の最新資料</mark>をご確 認ください。

ID: 683587

**UG-SDI1005** バージョン: **2020.08.20**

# 目次

| 1. SDI IP コアの概要                                    | 4  |

|----------------------------------------------------|----|

| 1.1. リリース情報                                        | 4  |

| 1.2. デバイスファミリーのサポート                                |    |

| 1.3. 概要                                            | 5  |

| 1.4. リソース使用率                                       | 7  |

|                                                    | _  |

| 2. SDI IP コアのご利用にあたって                              |    |

| 2.1. インテル FPGA IP コアのインストールとライセンス                  |    |

| 2.1.1. Intel FPGA IP Evaluation Mode               |    |

| 2.2. IP Catalog とパラメーター・エディター                      |    |

| 2.2.1. IP コアの生成 (インテル Quartus Prime スタンダード・エディション) |    |

| 2.2.2. SDI IP コアのパラメーター化                           |    |

| 2.2.3. SDI IP コアのパラメーター                            | 14 |

| 3. 機能の説明                                           | 16 |

| 3.1. トランスミッター                                      | 16 |

| HD-SDIのLN挿入                                        |    |

| HD-SDI の CRC 生成と挿入                                 |    |

| スクランブルと NRZI コーディング                                |    |

| トランシーバー・クロック                                       |    |

| 3.2. レシーバー                                         |    |

| NRZI デコーディングとデスクランブル                               |    |

| ワード・アライメント                                         |    |

| ビデオ・タイミング・フラグの抽出                                   |    |

| RP168 スイッチング・コンプライアンス                              |    |

| HD-SDI の LN 抽出                                     |    |

| HD-SDI の CRC チェック                                  |    |

| トランシーバーへのアクセス                                      |    |

| トランシーバー・クロック                                       |    |

| 3.3. トランシーバー                                       | 25 |

| 3.3.1. トランスミッターのクロック                               |    |

| 3.3.2. レシーバーのクロック                                  | 29 |

| 3.3.3. トランスミッターのトランシーバー・インターフェイス                   | 30 |

| 3.3.4. レシーバーのトランシーバー・インターフェイス                      | 31 |

| 3.4. 着信 SDI ストリームへのロック                             | 32 |

| 3.5. SDI における受信ビデオ・フォーマットの仕様                       | 34 |

| 4. SDI IP コアの信号                                    | 36 |

| 4.1. SDI クロック信号                                    |    |

| 4.1. SDI クロック信号<br>4.2. SDI インターフェイス信号             |    |

| 4.2. SDI 1 フターフェイス信号                               |    |

| 4.4. SDI ステーダス信号                                   | 45 |

|                                                    |    |

| 5. SDI IP コアのユーザーガイド・アーカイブ                         | 51 |

| 6 SDIIDコアのユーザーガイドや訂層麻                              | 52 |

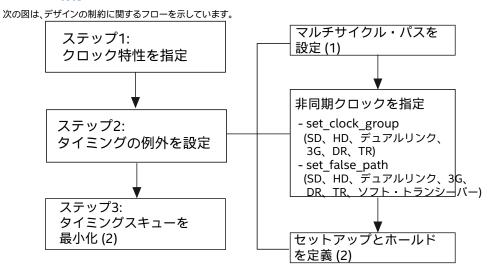

| A. 制約                                     | 55 |

|-------------------------------------------|----|

| A.1. タイミング・アナライザーでの制約の指定                  | 55 |

| A.1.1. Stratix IV デバイスを使用している SDI IP コアにお |    |

| A.2. SDI ソフト・トランシーバーの制約                   | 61 |

| B. クロック                                   | 62 |

| B.1. クロックのバージョン                           | 62 |

| C. 受信と再送信                                 | 63 |

| C.1. ループバック FIFO バッファー                    | 63 |

# 1. SDI IP コアの概要

SDI (シリアル・デジタル・インターフェイス) IP コアは、レシーバー、トランスミッター、または全二重 SDI を標準解像度 (SD)、高解像度 (HD)、または 3 ギガビット/秒 (3G) で実装します。SDI IP コアは、デュアル・スタンダード (HD-SDIと SD-SDI) およびトリプル・スタンダード (SD-SDI、HD-SDI、3G-SDI) をサポートします。これらのモードは、自動のレシーバーレートの検出を提供します。

### 注意:

インテルでは、SDI IP コアのサポートを終了しています。この IP は、サポートなしで引き続き使用することが可能です。ただし、インテルでは、SDI II Intel® FPGA IP を使用し、最新の機能と継続的なサポートをご利用いただくことを推奨しています。

### 表 1. SDI IP コアの機能

| 機能         | 説明                                                                                                                                     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|

| サポート       | <ul><li>複数の SDI 規格とビデオ・フォーマット</li><li>RP168 ビデオ・スイッチ・ライン要件</li></ul>                                                                   |

| トランスミッター   | <ul> <li>巡回冗長検査 (CRC) のエンコーディング (HD のみ)</li> <li>ライン番号 (LN) の挿入 (HD のみ)</li> <li>ワード・スクランブル</li> <li>トランスミッターのクロック・マルチブレクサー</li> </ul> |

| レシーバー      | <ul> <li>CRC のデコーディング (HD のみ)</li> <li>LN の抽出 (HD のみ)</li> <li>ビデオのタイミング信号のフレーミングと抽出</li> <li>ワードのアライメントとデスクランブル</li> </ul>            |

| IP Catalog | 使いやすいパラメーター・エディター                                                                                                                      |

# 関連情報

- SDI II Intel FPGA IP User Guide

- SDI Audio Intel FPGA IP User Guide

# 1.1. リリース情報

次の表に、このリリースの SDI IP コアに関する情報を示します。

### 表 2. リリース情報

| 項目    | 内容        |

|-------|-----------|

| バージョン | 19.1      |

| リリース日 | 2019年9月   |

|       | continued |

Intel Corporation.無断での引用、転載を禁じます。Intel、インテル、Intel ロゴ、その他のインテルの名称やロゴは、Intel Corporation またはその子会社の商標です。インテルは FPGA 製品および半導体製品の性能がインテルの標準保証に準拠することを保証しますが、インテル製品およびサービスは、予告なく変更される場合があります。インテルが書面にて明示的に同意する場合を除き、インテルはここに記載されたアプリケーション、または、いかなる情報、製品、またはサービスの使用によって生じるいっさいの責任を負いません。インテル製品の顧客は、製品またはサービスを購入する前、および、公開済みの情報を信頼する前には、デバイスの仕様を最新のバージョンにしておくことをお勧めします。

### 683587 | 2020.08.20

| 項目       | 内容     |

|----------|--------|

| 注文コード    | IP-SDI |

| プロダクト ID | 00AE   |

| ベンダー ID  | 6AF7   |

インテルでは、この IP コアが前回のリリースに含まれている場合は、インテル® Quartus® Prime 開発ソフトウェアの現在のバージョンが各 IP コアの前回のバージョンをコンパイルすることを検証しています。この検証における例外は、Serial Digital Interface (SDI) IP Core Release Notes で報告されています。インテルでは、前回のリリースより古い IP コアのバージョンでのコンパイルは検証していません。

### 関連情報

- Errata for SDI IP core in the Knowledge Base

- Serial Digital Interface (SDI) IP Core Release Notes

# 1.2. デバイスファミリーのサポート

次の表は、SDI IP コアのデバイスサポート情報を示しています。

### 表 3. デバイスファミリーのサポート

| デバイスファミリー                              | サポート   |

|----------------------------------------|--------|

| Arria <sup>®</sup> II GZ               | 最終     |

| Arria V                                | 最終     |

| Cyclone® IV GX (1)                     | 最終     |

| Cyclone V                              | 最終     |

| Stratix <sup>®</sup> IV <sup>(2)</sup> | 最終     |

| Stratix V (2)                          | 最終     |

| 他のデバイスファミリー                            | サポートなし |

# 1.3. 概要

SMPTE (Society of Motion Picture and Television Engineers) は、SDI 規格を定義しています。この規格は、ビデオシステム設計者にビデオ制作施設の機器間のインターコネクトとして広く使用されています。

<sup>(1)</sup> チャネル・リコンフィグレーション・モードでのトランシーバーのダイナミック・コンフィグレーションは、 EP4CGX110 および EP4CGX150 デバイスでのデュアルおよびトリプル・スタンダードにはサポートされていません。代わりに、PLL リコンフィグレーション・モードでの最終トランシーバー・ダイナミック・リコンフィグレーションを使用します。

<sup>(2)</sup> SD-SDI モードで SDI IP コアを駆動する際に 27MHz しか利用できない場合は、追加の PLL で 67.5MHz のリファレンス・クロックを生成する必要があります。

SDI IP コアは、次の SDI データレートを処理します。

- SMPTE259M-1997 10-Bit 4:2:2 Component Serial Digital Interface で定義されている 270 メガビット/秒 (Mbps) SD-SDI

- SMPTE292M-1998 Bit-Serial Digital Interface for High Definition Television Systems で定義されている 1.5 ギガビット/秒 (Gbps) HD-SDI

- SMPTE425M-AB 2006 3Gb/s Signal/Data Serial Interface- Source Image Format Mapping で定義されている 3Gbps SDI

- SMPTE372M-Dual Link 1.5Gb/s Digital Interface for 1920×1080 and 2048×1080

Picture Formats で定義されている予備的なデュアルリンク SDI のサポート

- 270Mbps および 1.5Gbps SDI に向けたデュアル・スタンダード・サポート

- 270Mbps、1.5Gbps、3Gbps SDI に向けたトリプル・スタンダード・サポート

- SD-SDI、HD-SDI、および 3G-SDI に向けたトリプル・スタンダード・サポート

- SMPTE425M Level A サポート (ソース画像の直接フォーマット)

- SMPTE425M Level B サポート (デュアル・リンク・マッピング)

## 表 4. **SDI** 規格のサポート

SD-SDI を除くすべての SDI 規格には、トランシーバーベースのデバイスが必要です。 次の表に、さまざまな FPGA デバイスにおける SDI 規格のサポートを示します。

| デバイスファミリー                                                                                   | SDI 規格 |        |        |                                          |                 |                 |

|---------------------------------------------------------------------------------------------|--------|--------|--------|------------------------------------------|-----------------|-----------------|

|                                                                                             | SD-SDI | HD-SDI | 3G-SDI | <b>HD-SDI</b> デュアル<br>リンク <sup>(3)</sup> | デュアル・スタンダ<br>ード | トリプル・スタンダ<br>ード |

| Arria II GX                                                                                 | あり     | あり     | あり     | あり                                       | あり              | あり              |

| Arria V                                                                                     | あり     | あり     | あり     | あり                                       | あり              | あり              |

| Stratix IV (4)                                                                              | あり     | あり     | あり     | あり                                       | あり              | あり              |

| Stratix V (4)                                                                               | あり     | あり     | あり     | あり                                       | あり              | あり              |

| Cyclone IV GX<br>(EP4CGX15,<br>EP4CGX30)                                                    | あり     | _      | _      | _                                        | _               | _               |

| Cyclone IV GX<br>(EP4CGX30<br>(F484),<br>EP4CGX50,<br>EP4CGX75,<br>EP4CGX110,<br>EP4CGX150) | あり     | あり     | あり     | あり                                       | あり              | あり              |

| Cyclone V <sup>(5)</sup>                                                                    | あり     | あり     | あり     | あり                                       | あり              | あり              |

<sup>(3)</sup> HD-SDI デュアルリンクは、リンク A とリンク B の間で最大 40ns のタイミング差をサポートし、SMPTE372M の要件を満たします。

<sup>(5)</sup> 必要なデータレートが高すぎるため、3G-SDI スタンダードは、トランシーバーのスピードグレード 7 の Cyclone V デバイスではサポートされません。

<sup>(4)</sup> トランシーバーを備える Stratix IV および Stratix V のバリアントのみが、すべての SDI レートをサポートします。

# 1.4. リソース使用率

次の表は、SDI IP コアのさまざまなパラメーターの一般的なリソース使用率を示しています。これは、インテル Quartus Prime スタンダード・エディション・ソフトウェアでの場合になります。

*注意:* 特に指定されていない限り、IP コアのリソース使用率は双方向インターフェイスの設定に基づいています。

# 表 5. リソース使用率

| デバイス                                     | ビデオ規格                    | LE  | 組み合わせ ALUT | ロジックレジスター |

|------------------------------------------|--------------------------|-----|------------|-----------|

| Arria II GX                              | SD-SDI                   | _   | 839        | 680       |

|                                          | HD-SDI                   | _   | 978        | 833       |

|                                          | 3G HD-SDI                | _   | 1,259      | 1,015     |

|                                          | デュアルリンク HD-SDI           | _   | 2,029      | 1,711     |

|                                          | デュアル・スタンダード・レ<br>シーバー    | _   | 1,257      | 926       |

|                                          | デュアル・スタンダード・ト<br>ランスミッター | _   | 267        | 180       |

|                                          | トリプル・スタンダード              | -   | 1,891      | 1,305     |

| Arria V                                  | SD-SDI                   | _   | 1,189      | 920       |

|                                          | HD-SDI                   | _   | 1,185      | 910       |

|                                          | 3G HD-SDI                | _   | 1,444      | 1,142     |

|                                          | デュアルリンク HD-SDI           | _   | 2,446      | 1,880     |

|                                          | デュアル・スタンダード・レ<br>シーバー    | _   | 1,605      | 1,175     |

|                                          | デュアル・スタンダード・ト<br>ランスミッター | _   | 349        | 269       |

|                                          | トリプル・スタンダード              | _   | 2,273      | 1,677     |

| Cyclone IV GX<br>(EP4CGX15,<br>EP4CGX30) | SD-SDI                   | 916 |            |           |

| Cyclone IV GX                            | SD-SDI                   | _   | 1,129      | 671       |

| (EP4CGX50、<br>EP4CGX75、                  | HD-SDI                   | _   | 1,164      | 670       |

| EP4CGX110、<br>EP4CGX150)                 | 3G HD-SDI                | _   | 1,409      | 790       |

| •                                        | デュアルリンク HD-SDI           | _   | 2,515      | 1,467     |

|                                          | デュアル・スタンダード・レ<br>シーバー    | _   | 1,479      | 755       |

|                                          | デュアル・スタンダード・ト<br>ランスミッター | -   | 364        | 229       |

|                                          | トリプル・スタンダード              | _   | 2,235      | 1,121     |

| Cyclone V                                | SD-SDI                   | _   | 1,140      | 832       |

|                                          | HD-SDI                   | _   | 1,122      | 808       |

|                                          | 3G HD-SDI                | _   | 1,402      | 997       |

|                                          |                          |     |            | continued |

| デバイス       | ビデオ規格                    | LE | 組み合わせ ALUT | ロジックレジスター |

|------------|--------------------------|----|------------|-----------|

|            | デュアルリンク HD-SDI           | _  | 2,351      | 1,696     |

|            | デュアル・スタンダード・レ<br>シーバー    | _  | 1,539      | 1,042     |

|            | デュアル・スタンダード・ト<br>ランスミッター | -  | 352        | 260       |

|            | トリプル・スタンダード              | _  | 2,217      | 1,508     |

| Stratix IV | SD-SDI                   | _  | 839        | 680       |

|            | HD-SDI                   | _  | 978        | 833       |

|            | 3G HD-SDI                | _  | 1,259      | 1,015     |

|            | デュアルリンク HD-SDI           | _  | 2,029      | 1,711     |

|            | デュアル・スタンダード・レ<br>シーバー    | _  | 1,257      | 926       |

|            | デュアル・スタンダード・ト<br>ランスミッター | _  | 267        | 180       |

|            | トリプル・スタンダード              | _  | 1,891      | 1,305     |

| Stratix V  | SD-SDI                   | _  | 913        | 707       |

|            | HD-SDI                   | _  | 955        | 703       |

|            | 3G HD-SDI                | _  | 1,126      | 823       |

|            | デュアルリンク HD-SDI           | _  | 2,049      | 1,522     |

# 2. SDI IP コアのご利用にあたって

# 2.1. インテル FPGA IP コアのインストールとライセンス

インテル Quartus Prime 開発ソフトウェアのインストールには、インテル FPGA IP ライブラリーが含まれています。このライブラリーでは、追加ライセンスが不要な本番での使用に役立つ IP コアを多数提供しています。一部のインテル FPGA IP コアには、本番での使用に別途ライセンスの購入が必要です。 Intel FPGA IP Evaluation Mode を使用すると、ライセンス取得が必要なインテル FPGA IP コアをシミュレーションおよびハードウェアで評価してから、IP コアの完全な本番向けライセンスの購入を決定することができます。ハードウェア・テストを完了し、本番で IP を使用する準備が整った段階で、ライセンス取得が必要なインテル IP コアの完全な本番向けライセンスを購入します。

インテル Quartus Prime 開発ソフトウェアは、デフォルトで IP コアを次の位置にインストールします。

### 表 6. IP コアのインストール位置

| 位置                                                                 | ソフトウェア                           | プラットフォーム |

|--------------------------------------------------------------------|----------------------------------|----------|

| <pre><drive>:\intelFPGA\quartus\ip\altera</drive></pre>            | インテル Quartus Prime スタンダード・エディション | Windows  |

| <pre><home directory="">:/intelFPGA/quartus/ip/altera</home></pre> | インテル Quartus Prime スタンダード・エディション | Linux    |

注意: インテル Quartus Prime 開発ソフトウェアは、インストール・パスのスペースをサポートしていません。

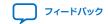

# 2.1.1. Intel FPGA IP Evaluation Mode

無償の Intel FPGA IP Evaluation Mode を使用すると、ライセンスの取得が必要なインテル FPGA IP コアを購入する前に、それらをシミュレーションとハードウェアで評価することができます。 Intel FPGA IP Evaluation Mode では、次の評価をサポートしています。その際に、追加ライセンスは不要です。

- 許可されているインテル FPGA IP コアのシステムでの動作シミュレーション

- IP コアの機能、サイズ、スピードの迅速かつ容易な検証

- IP コアを含むデザインに向けた時間制限付きデバイス・プログラミング・ファイルの生成

- IP コアとのデバイスのプログラミング、およびハードウェアでのデザインの検証

Intel FPGA IP Evaluation Modeでは、次の動作モードをサポートしています。

- **Tethered** ライセンスの取得が必要なインテル FPGA IP を含むデザインを無期限に実行することができます。これには、ボードとホスト・コンピューター間の接続を使用します。テザーモードでは、JTAG (シリアル・ジョイント・テスト・アクション・グループ) ケーブルの接続がボードの JTAG ポートとホスト・コンピューターとの間に必要です。ホスト・コンピューターでは、インテル Quartus Prime の Programmer をハードウェア評価期間中に実行します。 Programmer には、インテル Quartus Prime 開発ソフトウェアの最小のインストールのみが必要で、インテル Quartus Prime のライセンスは必要ありません。ホスト・コンピューターでは、JTAG ポートを介して周期的な信号をデバイスに送信することにより、評価時間を制御します。 デザインのライセンスが必要な IP コアのすべてがテザーモードをサポートしている場合、評価時間はいずれかの IP コアの評価期限に達するまでになります。すべての IP コアで無制限の評価時間をサポートしている場合は、デバイスはタイムアウトしません。

- Untethered ライセンスが必要な IP を含むデザインを一定時間実行することができます。イン テル Quartus Prime 開発ソフトウェアを実行しているホスト・コンピューターからデバイスが切 断された場合、IP コアは非テザーモードに戻ります。また、デザインのライセンスが必要な IP コア のいずれかがテザーモードをサポートしていない場合に、IP コアは非テザーモードに戻ります。

デザインのライセンスが必要なインテル FPGA IP のいずれかの評価時間が終了すると、デザインは機能を停止します。Intel FPGA IP Evaluation Mode を使用している IP コアはすべて、デザインのいずれかの IP コアがタイムアウトになると同時にタイムアウトします。評価時間が終了すると、ハードウェアの検証を続ける前に FPGA デバイスを再プログラミングする必要があります。IP コアを本番環境でも使用するには、該当する IP コアの完全な本番向けライセンスを購入してください。

ライセンスを購入し、完全な本番向けのライセンスキーを生成後に、制限のないデバイス・プログラミング・ファイルを生成することができます。Intel FPGA IP Evaluation Mode では、コンパイラーは時間制限付きのデバイス・プログラミング・ファイル(*<project name>* \_time\_limited.sof) のみを生成します。このファイルは、制限時間になると使用できなくなります。

### 図 -1: Intel FPGA IP Evaluation Mode のフロー

注意: パラメーター化の手順および実装の詳細については、各 IP コアのユーザーガイドを参照してください。

Intel FPGA Software License Agreements では、ライセンスのある IP コア、インテル Quartus Prime 開発ソフトウェア、およびライセンスのないすべての IP コアのインストールと使用について管理しています。

### 関連情報

- Intel FPGA Licensing Support Center

- Introduction to Intel FPGA Software Installation and Licensing

# 2.2. IP Catalog とパラメーター・エディター

IP Catalog には、プロジェクトで使用できる IP コアが表示されます。これには、インテル FPGA IP や IP Catalog の検索パスに追加されている他の IP が含まれます。IP Catalog の次の機能を使用し、IP コアの検索およびカスタマイズを行います。

- IP Catalog を Show IP for active device family または Show IP for all device families でフィルターします。プロジェクトを開いていない場合は、IP Catalog で Device Family を選択します。

- 検索フィールドを使用し、IP Catalog にある IP コアの完全な、または部分的な名称を検索します。

- IP Catalog で IP コアの名称を右クリックすると、サポートされるデバイスの詳細の表示や、IP コアのインストール・フォルダーを開いたり、IP の資料へのリンクを参照することができます。

- Search for Partner IP をクリックし、ウェブサイト上のパートナー IP の情報にアクセスします。

パラメーター・エディターは、インテル Quartus Prime スタンダード・エディション・プロジェクトの IP バリエーションに対してトップレベルの Quartus IP ファイル (.qip) を生成します。これらのファイルは、プロジェクトの IP のバリエーションを表し、パラメーター化の情報を格納します。

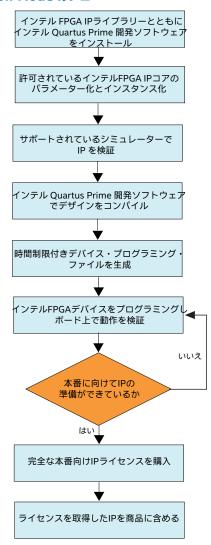

# 2.2.1. IP コアの生成 (インテル Quartus Prime スタンダード・エディション)

この項では、インテル Quartus Prime スタンダード・エディションのソフトウェアでレガシー・パラメーター・エディターを使用して行う IP バリエーションのパラメーター化と生成について説明します。

### 図 -2: レガシー・パラメーター・エディター

683587 | 2020.08.20

注意: レガシー・パラメーター・エディターは、インテル Quartus Prime プロ・エディションのソフトウェアとは 異なる出力ファイル構造を生成します。

- 1. IP Catalog (**Tools** > **IP Catalog**) で、カスタマイズする IP コアの名前を検索してダブルクリックします。パラメーター・エディターが表示されます。

- 2. IP バリエーションのトップレベル名と出力 HDL のファイルタイプを指定します。この名前により、 プロジェクト内の IP コアのバリエーションのファイルを識別します。**OK** をクリックします。IP バリ エーションの名前またはパスにスペースを含めないでください。

- 3. パラメーター・エディターで、IP バリエーションにパラメーターとオプションを指定します。特定の IP コアのパラメーターの詳細に関しては、お使いの IP コアのユーザーガイドを参照してください。

- 4. Finish または Generate (パラメーター・エディターのバージョンによって異なる) をクリックします。パラメーター・エディターは、指定されている内容に基づき IP バリエーションのファイルを生成します。生成完了時にプロンプトが表示されたら、Exit をクリックします。パラメーター・エディターはトップレベルの、gip ファイルを現在のプロジェクトに自動的に追加します。

- 注 インテル Arria® 10 デバイスよりも前にリリースされたデバイスの場合は、生成される.gip 意: および.sip ファイルをプロジェクトに追加し、IP とプラットフォーム・デザイナー・システムを表す必要があります。レガシー・パラメーター・エディターで生成された IP バリエーションをプロジェクトに手動で追加するには、Project > Add/Remove Files in Project をクリックし、IP バリエーションの.gip ファイルを追加します。

# 2.2.2. SDI IP コアのパラメーター化

SDI IP コアをパラメーター化するには、次の手順を実行します。

- 1. ビデオ規格を選択します。

- 2. Bidirectional、Transmitter、または Receiver のインターフェイス方向を選択します。

- 3. Transceiver Options タブをクリックします。

- 4. Transceiver and Protocol で、Generate transceiver and protocol blocks をクリックします。

- 5. 開始チャネル番号を選択します。

- 6. EP4CGX110 または EP4CGX150 デバイスを Cyclone IV GX に選択し、デュアルおよびトリプル・スタンダードを使用している場合は、Use PLL reconfiguration for transceiver dynamic reconfiguration をオンにします。

- 注意: 他の Cyclone IV GX デバイスでこのオプションをオンにすることは可能ですが、推奨されていません。

- 7. デザインで TX ブロックに 2 つのシリアル 入力クロックが必要な場合は、Enable TX PLL select for 1/1.000 and 1/1.001 data rate reconfiguration をオンにします。

- 注意: この機能は、Arria II および Stratix IV GX デバイスファミリーでのみ利用することができます。

- 8. Receiver/Transmitter Options タブをクリックします。

- 9. 必要なレシーバーオプションをオンにします。

- 10. 必要なトランスミッター・オプションをオンにします。

- 11. **Next** をクリックします。

# 関連情報

SDI IP コアのパラメーター (14 ページ)

# 2.2.3. SDI IP コアのパラメーター

SDI のパラメーターは、IP Catalog を使用して設定することができます。

| V;                                  | ラメーター                                                                           | 値                                                                                                                            | 説明                                                                                                                                                                                                                                                                                                           |

|-------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Protocol<br>Options                 | Video standard                                                                  | SD-SDI, HD-SDI,<br>3G-SDI, HD-SDI<br>dual link, dual or<br>triple standard SDI                                               | <ul> <li>ビデオ規格を設定します。</li> <li>SD-SDI - オーバーサンプリング・ロジックが含まれます。</li> <li>HD-SDI - LN の挿入および抽出と CRC の生成および抽出ブロックに切り替わります。SD-SDI を選択すると、LN の挿入および抽出と CRC の生成および抽出ブロックから切り替わります。</li> <li>Dual or triple rate SDI - SD-SDI および HD-SDI 規格の両方の処理ブロックが含まれます。さらに、バイパスパスのロジック、および入力規格を自動的に切り替えるロジックが含まれます。</li> </ul> |

|                                     | Interface settings                                                              | Birectional,<br>Receiver,<br>Transmitter                                                                                     | トランシーバーまたはプロトコルプロックの一方、もしくは両方を選択します。 GX 以外のデバイスを選択している場合は、SD-SDI プロトコルプロックのみが許可されます。 HD-SDI または 3G-SDI のプロトコルブロックを生成する場合は、GX デバイスを選択する必要があります。                                                                                                                                                               |

| Transceiver<br>Option               | Transceiver and<br>Protocol                                                     | Generate<br>transceiver and<br>protocol blocks、<br>generate<br>transceiver block<br>only、または generate<br>protocol block only | トランシーバーまたはプロトコルブロックの一方、もしくは両方を選択します。<br>GX 以外のデバイスを選択している場合は、SD-SDI プロトコルブロックのみが許可されます。<br>HD-SDI または 3G-SDI のプロトコルブロックを生成する場合は、GX デバイスを選択する必要があります。                                                                                                                                                         |

|                                     | Use soft logic for transceiver                                                  | On または Off                                                                                                                   | Stratix IV トランシーバーを使用するのではなく、ソフトロジックを使用してトランシーバー・ロジックを実装します。SD-SDI専用です。例えば、デバイスのハード・トランシーバーが不足している場合は、ソフトロジックで機能を実装することができます。デバイスに予備のトランシーバーがある場合は、それらを使用することをお勧めします。                                                                                                                                        |

|                                     | Starting channel number                                                         | 0,4,8,,156                                                                                                                   | デュアルまたはトリプル・スタンダード専用。各デュアルまたはトリプル・スタンダード SDI には、一意の開始チャネル番号が必要です。<br><i>注意:</i> このパラメーターは、Arria V、Cyclone V、および Stratix V デ<br>パイスには適用されません。                                                                                                                                                                 |

|                                     | Use PLL reconfiguration for transceiver dynamic reconfiguration                 | On または Off                                                                                                                   | デュアルまたはトリプル・スタンダードで、Cyclone IV GX デバイス専用。EP4CGX110 または EP4CGX150 デバイスを選択している場合は、このオプションをオンにする必要があります。                                                                                                                                                                                                        |

|                                     | Enable TX PLL select<br>for 1/1.000 and<br>1/1.001 data rate<br>reconfiguration | On または Off                                                                                                                   | トランスミッターのシリアル・リファレンス・クロックの追加の入力ポートを有効にします。<br><i>注意</i> : Arria II および Stratix IV デバイスでのみ利用することができます。                                                                                                                                                                                                        |

| Receiver/<br>Transmitter<br>Options | CRC error output                                                                | On または Off                                                                                                                   | <ul> <li>On: CRC の監視 (SD-SDI モードには適用されません)</li> <li>Off: CRC の監視なし (ロジックを保存)</li> </ul>                                                                                                                                                                                                                      |

| - •                                 | SDI synchronization output                                                      | On または Off                                                                                                                   | 同期出力を提供します。                                                                                                                                                                                                                                                                                                  |

|                                     | Tolerance to consecutive missed EAV/SAV                                         | 0, 1, 2,, 15                                                                                                                 | レシーバープロトコル専用。着信ビデオで許容される連続する欠落 EAV の数を設定することができます。レシーバーコアでより多くのエラーを許容する場合は、より大きな値を指定します。                                                                                                                                                                                                                     |

|                                     |                                                                                 |                                                                                                                              | continued                                                                                                                                                                                                                                                                                                    |

# 2. SDI IP コアのご利用にあたって

683587 | 2020.08.20

| パラ | ラメーター                     | 値          | 説明                                                                                                          |

|----|---------------------------|------------|-------------------------------------------------------------------------------------------------------------|

|    |                           |            | レシーバーコアでエラーを許容しない場合は、このオプションを 0 に設<br>定します。                                                                 |

|    | Two times oversample mode | On または Off | HD-SDI トランスミッター専用。オンにすると、トランシーバーが 2 倍の速度で動作し、ジッターのパフォーマンスが向上します。 148.5MHzのtx_serial_refclkリファレンス・クロックが必要です。 |

# 3. 機能の説明

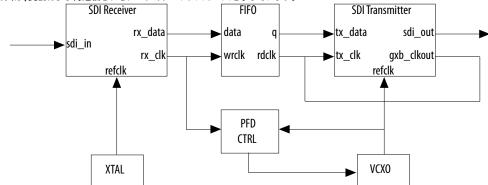

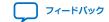

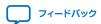

SDI IP コアは、トランスミッター、レシーバー、または全二重インターフェイスを実装します。SDI IP コアは、次のコンポーネントで構成されています。

- プロトコルブロック トランスミッターまたはレシーバー

- トランシーバー

- トランシーバー・コントローラー

パラメーター・エディターでは、デザインにプロトコル、トランシーバー、または複合ブロックのいずれかを指定することができます。例えば、デザインに複数のプロトコルブロックがある場合は、ブロックを 1 つのトランシーバーに多重化することができます。

トランシーバーは、ソフトロジック実装または GX トランシーバーのいずれかにすることができます。

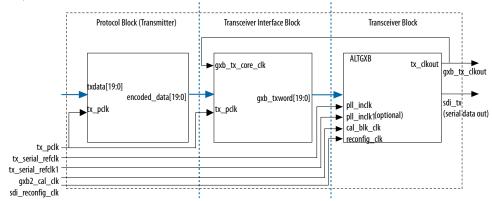

### 図 -3: SDI IP コアのブロック図

次の図は、SDI IP コアのブロック図を示しています。

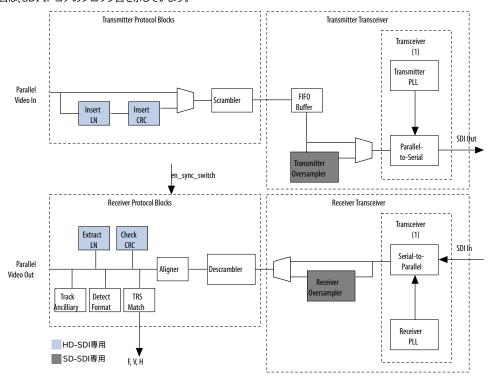

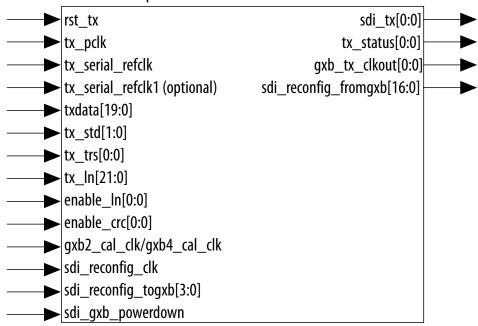

# 3.1. トランスミッター

トランスミッターには、次の要素が含まれます。

Intel Corporation.無断での引用、転載を禁じます。Intel、インテル、Intel ロゴ、その他のインテルの名称やロゴは、Intel Corporation またはその子会社の商標です。インテルは FPGA 製品および半導体製品の性能がインテルの標準保証に準拠することを保証しますが、インテル製品およびサービスは、予告なく変更される場合があります。インテルが書面にて明示的に同意する場合を除き、インテルはここに記載されたアプリケーション、または、いかなる情報、製品、またはサービスの使用によって生じるいっさいの責任を負いません。インテル製品の顧客は、製品またはサービスを購入する前、および、公開済みの情報を信頼する前には、デバイスの仕様を最新のバージョンにしておくことをお勧めします。

### 683587 | 2020.08.20

- SD/HD-SDI トランスミッター・スクランブラー

- HD-SDI トランスミッター・データ・フォーマッター (CRC および LN 挿入を含む)

- トランシーバー、プラス制御、およびマルチレート (デュアルまたはトリプル・スタンダード) SD/HD-SDI トランスミッターの動作を備えるインターフェイス・ロジック

- トランスミッター・クロック・マルチプレクサー (オプション)

トランスミッターは、次の機能を実行します。

- HD-SDIのLN挿入

- HD-SDI の CRC 生成と挿入

- クロックイネーブル信号の生成

- スクランブルと非ゼロ復帰反転 (NRZI) コーディング

- トランスミッター・ブロック内の 2 つのリファレンス・クロック信号間の内部切り替え。この機能はオプションであり、Arria II GZ および Stratix IV GX でのみ利用可能です。

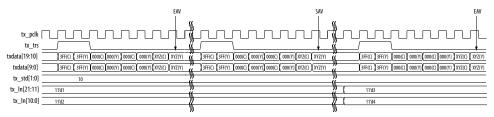

次の図は、SDI トランスミッターのトップレベルのブロック図を示しています。

# 図 -4: SDI トランスミッターのブロック図

HD-SDI の場合、トランスミッターは 20 ビットのパラレル・ビデオ・データを受け入れます。SD-SDI の場合は 10 ビットのパラレルデータです。

# 表 7. サポートされるビデオ規格における txdata のビット割り当て

次の表は、txdataのビットの割り当てを示しています。

| txdata  | SD-SDI                | HD-SDI | 3G-SDI Level A | 3G-SDI Level B                |

|---------|-----------------------|--------|----------------|-------------------------------|

| [19:10] | 未使用                   | Υ      | Υ              | Cb、Y、Cr、Y マルチプレク<br>ス (リンク A) |

| [9:0]   | Cb、Y、Cr、Y マルチプレク<br>ス | С      | С              | Cb、Y、Cr、Y マルチプレク<br>ス (リンク B) |

HD-SDI の動作の場合、現在のビデオライン番号が各ラインの適切なポイントに挿入されます。CRC も計算され、ルーマチャネルとクロマチャネルに挿入されます。

683587 | 2020.08.20

パラレル・ビデオ・データは、SDI の仕様に従いスクランブルされ、NRZI でエンコードされます。

トランシーバーは、エンコードされているパラレルデータを高速シリアル出力に変換します (パラレルからシリアルへの変換)。

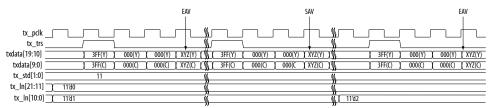

# HD-SDIのLN 挿入

SMPTE292M のセクション 5.4 では、各 HD-SDI ビデオラインに含まれる 2 ワードの形式を定義しています。これは、現在のライン番号を示すものです。HD-SDI の LN 挿入モジュールは、下位 11 ビットの $tx_1n$  を取得してフォーマットし、出力データに 2 ワードとして挿入します。 HD-SDI の LN 挿入モジュールは、現在のライン番号を入力として受け入れます。

LN ワード (LNO および LN1) は、EAV TRS シーケンスの「XYZ」ワードに続く2つのワードを上書きします。同じ値がルーマチャネルとクロマチャネルに含まれます。LN を正しく挿入するには、EAV TRS および SAV TRS の両方の最初のワードに tx\_trs 信号をアサートする必要があります (3-47 ページの図 3-31 および 3-48 ページの図 3-32 を参照してください)。

注意:

システムがライン番号を認識していない場合は、ロジックを実装して出力ビデオ・フォーマットを検出し、現在のラインを特定することができます。この機能は、この SDI MegaCore ファンクションの範囲外です。

# HD-SDI の CRC 生成と挿入

SMPTE292M のセクション 5.5 では、各 HD-SDI ビデオラインのクロマチャネルとルーマチャネルに 含まれる CRC を定義しています。HD-SDI の CRC モジュールは、必要な CRC を生成してフォーマット し、出力データに挿入します。

HD-SDI の CRC モジュールは、CRC の計算に含める必要があるワードを識別し、ワードの挿入が必要な出力データの位置を決定します。フォーマットされている CRC データワード (ルーマチャネルの場合は YCR0 と YCR1、クロマチャネルの場合は CCR0 と CCR1) は、EAV の後のライン番号ワードに続く2つのワードを上書きします。このモジュールは、ルーマチャネルとクロマチャネルに対して個別の計算を提供します。

モジュールは、アクティブなデジタルラインのすべてのワードに対して CRC を計算します。これは、最初のアクティブなワードラインから始まり、ライン番号の最後のワード (LN1) で終わります。CRC の初期値は 0 に設定されており、その後、多項式ジェネレーターの方程式 CRC(X) = X18 + X5 + X4 + 1が適用されます。

HD-SDI の CRC モジュールは、出力データの各ビットに多項式ジェネレーターの方程式を繰り返し適用することにより、CRC の計算を実装します。その際は、LSB が最初に処理されます。

CRC を正しく生成および挿入するには、EAV TRS および SAV TRS の両方の最初のワードに  $tx\_trs$  信号をアサートする必要があります (3-47 ページの図 3-31 および 3-48 ページの図 3-32 を参照してください)。

## スクランブルと NRZI コーディング

SMPTE292M のセクション 5 および SMPTE292M のセクション 7 では、SDI と HD-SDI の両方に使用される共通のチャネル・コーディングを定義しています。このチャネル・コーディングは、スクランブル関数 (G1(X) = X9 + X4 + 1) とそれに続く NRZI エンコーディング (G2(X) = X + 1) で構成されます。スクランブル・モジュールは、このチャネル・コーディングを実装します。モジュールをコンフィグレーションすることにより、10 ビットまたは 20 ビットのパラレルデータを処理することができます。

スクランブル・モジュールは、出力データの各ビットにスクランブルと NRZI エンコーディングのアルゴリズムを繰り返し適用し、チャネル・コーディングを実装します。その際は、LSB が最初に処理されます。 SMPTE259M の図 C.1 は、アルゴリズムがどのように実装されるかを示しています。

# トランシーバー・クロック

tx\_serial\_refclk1 はオプションのポートで、パラメーター・エディターで **Enable TX PLL** select for 1/1.000 and 1/1.001 data rate reconfiguration をオンにすると有効になります。

### 図 -5: トランスミッターのクロックスキーム

この表は、トランスミッターのクロックスキームを示しています。

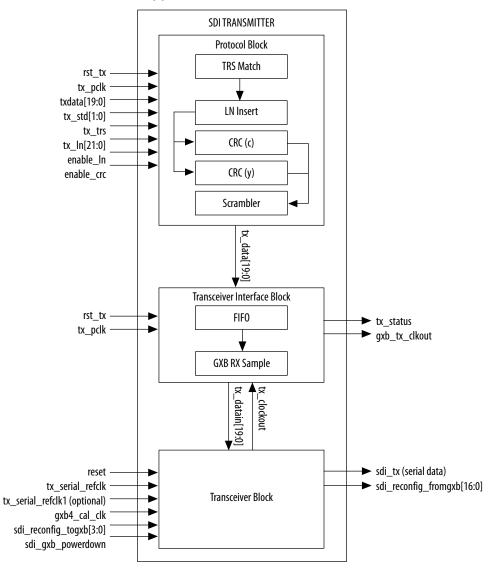

# 3.2. レシーバー

レシーバーには、次の要素が含まれます。

- SD/HD-SDI レシーバー・デスクランブラーとワードアライナー

- HD-SDI レシーバー CRC および LN 抽出器

- トランシーバー、プラス制御、およびマルチレート (デュアルまたはトリプル・スタンダード) SD/HD-SDI トランスミッターの動作を備えるインターフェイス・ロジック

- レシーバー・フレーミング (ビデオのタイミング信号の抽出を伴う)

- 補助データの識別と追跡

レシーバーは、次の機能を実行します。

- NRZI デコーディングとデスクランブル

- ワード・アライメント

- ビデオ・タイミング・フラグの抽出

- RP168 のスイッチング・コンプライアンス

- HD-SDIのLN抽出

- HD-SDI の CRC

- トランシーバーへのアクセス

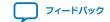

### 図 -6: SDI レシーバーのブロック図

次の図は、SDI レシーバーのトップレベルのブロック図を表しています。

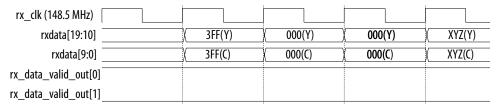

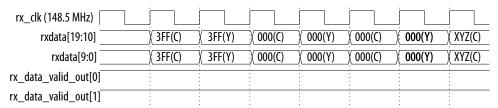

受信データは NRZI でデコードされ、デスクランブルされてから、ワードでアライメントされたパラレル 出力 (HD-SDI の場合は 20 ビット、SD-SDI の場合は 10 ビット) として示されます。rxdata バスの 定義については、3-41 ページの表 3-16 を参照してください。

### 表 8. サポートされるビデオ規格における rxdata のビット割り当て

次の表は、rxdata のビットの割り当てを示しています。

| rxdata  | SD-SDI                | HD-SDI | 3G-SDI Level A | 3G-SDI Level B                |

|---------|-----------------------|--------|----------------|-------------------------------|

| [19:10] | 未使用                   | Υ      | Υ              | Cb、Y、Cr、Y マルチプレク<br>ス (リンク A) |

| [9:0]   | Cb、Y、Cr、Y マルチプレク<br>ス | С      | С              | Cb、Y、Cr、Y マルチプレク<br>ス (リンク B) |

レシーバー・インターフェイスでは、受信データの F、V、および H のタイミング信号を抽出し、追跡します。アクティブな画像と補助データワードもまた、用途に応じて識別されます。

HD-SDI の場合は、受信した CRC がルーマチャネルとクロマチャネルに対してチェックされます。LN も抽出され、デザインからの出力として提供されます。

# NRZI デコーディングとデスクランブル

デスクランブラー・モジュールは、チャネルのデコード機能を提供します。これは、SDIと HD-SDI の両方に共通です。これには、NRZI デコーディング、およびそれに続いて必要なデスクランブルが実装されます。SMPTE259M の図 C.1 で示されているアルゴリズムは、レシーバーのデータに繰り返し適用されます。その際は、LSB が最初に処理されます。

# ワード・アライメント

アライナーワードでは、デスクランブルされたレシーバーデータをアライメントし、出力データのビット順序が元のビデオデータのビット順序と同じになるようにします。

## 表 9. EAV と SAV のシーケンス

EAV および SAV のシーケンスにより、正しいワード・アライメントを決定します。次の表に、それぞれの規格のパターンを示します。

| ビデオ規格          | EAV と SAV のシーケンス                        |  |

|----------------|-----------------------------------------|--|

| SD-SDI         | 3FF 000 000                             |  |

| HD-SDI         | 3FF 3FF 000 000 000 000                 |  |

| 3G-SDI Level A | 3FF 3FF 000 000 000 000                 |  |

| 3G-SDI Level A | 3FF 3FF 3FF 000 000 000 000 000 000 000 |  |

アライナーは、デスクランブルされたレシーバーデータで選択されているパターンと一致します。可能なワード・アライメントのいずれかでパターンが検出されると、フラグが立てられ、一致したアライメントが示されます。このプロセスは、レシーバーのデータに継続的に適用されます。

アライナーの第 2 段階では、データの正しいワード・アライメントを特定します。同じアライメントをもつ 3 つの連続する TRS を検索し、そのアライメントを格納します。その後、異なるアライメントで 2 つの連続する TRS が検出された場合は、この新しいアライメントが格納されます。

アライナーの最終段階では、受信データにバレルシフト機能を適用し、正しくアライメントされたパラレルワード出力を生成します。この SDI MegaCore ファンクションでは、バレルシフターを使用すると、デザインを 1 つのアライメントから別のアライメントに即座に切り替えることができます。

# ビデオ・タイミング・フラグの抽出

TRS 一致モジュールは、受信データから F、V、および H のビデオ・タイミング・フラグを抽出します。これ らのフラグを使用し、レシーバーのフォーマット検出、またはフライホイール機能の実装を行うことがで きます。

TRS 一致モジュールではまた、HD-SDI のライン番号と CRC ワードを識別します。

# RP168 スイッチング・コンプライアンス

RP168 の要件を満たすには、トランシーバーがスイッチング・ラインの終わりまでに回復可能である必 要があります。

#### サポートされているビデオ・スイッチング・タイプ 表 10.

次の表に、サポートされているビデオ・スイッチング・タイプを示します。

| 規格/データレート | フォーマット            | <b>RP168</b> のサポート | 切り替えるソース                 |

|-----------|-------------------|--------------------|--------------------------|

| Fixed     | Switch (同じフォーマット) | あり                 | HD-1080i30 から HD-1080i30 |

| Fixed     | Switch            | なし                 | HD-1080 からHD-720         |

| Switch    | Fixed             | なし                 | HD-1080 から SD-525        |

| Switch    | Switch            | なし                 | HD-1080 から SD-525        |

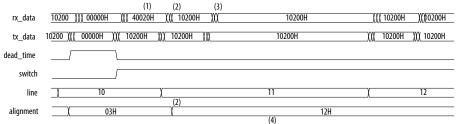

次の図は、RP168 スイッチング時のアライナーブロックとフォーマット・ブロックの動作を示しています。

#### 図 -7: アライナーブロックの動作

アライナーブロックは、ユーザー入力の en\_sync\_switch 信号に基づき、すぐに次の TRS タイミングにアライメントします。

align\_locked/rx\_status[2]

- (1) アライメントの不一致 (2) 次のTRSでの新しいアライメント (3) 新しいアライメントにデータがアライメント

- (4) 0割り込み

フォーマット・ブロックはユーザー入力の en sync switch 信号を 3 ラインラッチし、新しい TRS アライメントにすぐに再アライメントします。スイッチング時に、ダウンストリームの割り込みは0になり ます。trs locked および frame locked 信号は、同期切り替え時にデアサートされることはあり ません。

# HD-SDIのLN抽出

HD-SDI の LN 抽出モジュールは、SMPTE292M のセクション 5.4 で定義されている LN ワードを HD-SDI クロマチャネルから抽出してフォーマットします。デザインでは、LN を出力として提供します。

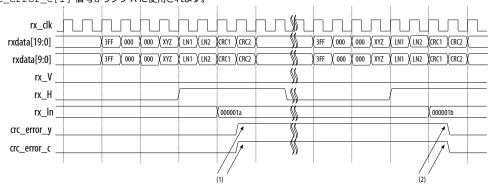

# HD-SDI の CRC チェック

CRC モジュールは、SMPTE292M のセクション 5.5 で定義されている CRC を HD-SDI のルーマチャネルおよびクロマチャネルに対してチェックします。

注意: このモジュールは、レシーバーとトランスミッターに共通です。

このチェックは、受信した各ビデオラインの CRC を再計算し、結果を受信した CRC データに対して確認 することによって実装されます。結果が異なる場合は、エラーフラグがアサートされます。ルーマチャネルとクロマチャネルには個別のエラーフラグがあります。フラグは、次のチェックが実行されるまでアサートされた状態で保たれます。

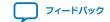

# トランシーバーへのアクセス

インテル Quartus Prime スタンダード・エディション・ソフトウェアを使用すると、暗号化されていない ALTGX ラッパーファイルを介してトランシーバーにアクセスすることができます。Arria II GX、Arria V、Cyclone IV GX、および Stratix IV GX のコンフィグレーションに向けた ALTGX ラッパーファイル にアクセスすることができます。

次のいずれかの方法を使用して、ALTGX ラッパーファイルにアクセスすることができます。

- それぞれのデバイス・ハンドブックに記載されている有効な範囲を使用して ALTGX ラッパーファイルを編集する

- ALTGX\_RECONFIG メガファンクションを介してアナログ制御を使用する

*注意:* 再生成後にラッパーファイルのデフォルトの内容を損失しないようにするには、カスタマイズされている ALTGX ラッパーファイルを IP カタログを使用して再インスタンス化しないでください。

### ALTGX ラッパーファイルの編集

パラメーターの設定を変更するには、ALTGX ラッパーファイルの有効な範囲を編集します。

例えば、電圧出力差動制御設定を4から7に変更するには、ラッパーファイルの次の行を変更します。

alt4gxb\_component.vod\_ctrl\_setting = 4

683587 | 2020.08.20

この行を、次のように変更します。

alt4gxb\_component.vod\_ctrl\_setting = 7

注意: 特定のインテルデバイスの有効な範囲を確認するには、それぞれのデバイスのハンドブックを参照してください。

# アナログ制御の使用

ALTGX の設定に柔軟にアクセスして制御する必要がある場合は、ALTGX\_RECONFIG メガファンクションを使用してアナログ・リコンフィグレーションを有効にします。アナログ制御を使用して、次のトランシーバー・パラメーターのデフォルト設定を編集します。

- 電圧出力の差

- プリエンファシス制御のプリタップ

- プリエンファシス制御の1番目のポストタップ

- プリエンファシス制御の2番目のポストタップ

- イコライザーの DC ゲイン

- イコライザーの DC 制御

ALTGX\_RECONFIG メガファンクションは、単一チャネルの reconfig\_togxb[3:0] ポートと reconfig\_fromgxb[16:0] ポートを使用して、ALTGX に接続します。

ランタイムにアナログ制御とチャネル・リコンフィグレーションを有効にするには、reconfig\_mode\_sel 信号を使用します。

# トランシーバー・クロック

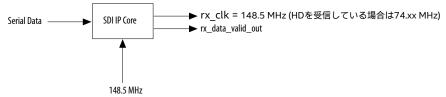

# 図 -9: レシーバーのクロックスキーム

次の図は、レシーバーの一般的なクロックスキームを示しています。

# 3.3. トランシーバー

トランシーバーでは、高速シリアル入力をデシリアライズします。

HD-SDI の場合、CDR 機能でデシリアライゼーションを実行し、レシーバー PLL をレシーバーデータにロックします。

SD-SDI の場合は、トランシーバーでシリアルデータの固定の周波数オーバーサンプルを提供します。 レシーバー PLL は常にリファレンス・クロックにロックされます。これにより、トランシーバーで 270Mbps のデータレートをサポートすることが可能です。

トランシーバーでは、SD-SDI または HD-SDI のデータのいずれかを処理することができます。データレートは自動的に検出されるため、インターフェイスではデバイスのリコンフィグレーションを必要とせずに、SD-SDI と HD-SDI の両方を処理することができます。

| 機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | サポートされるデバイス                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| クワッドあたり 2 つのトランスミッター PLL。<br>各クワッドでは、2 つの独立したトランスミッターのレートが許可されます。クワッド内のレシーバーは共通のトレーニング・クロックを共有しますが、独立したレシーバー PLL を備えています。同じトレーニング・クロックを SD-SDI と HD-SDI で使用するため、レシーバーは単一のクワッド内で異なる規格に対応することができます。                                                                                                                                                                                                                                                                                | Arria II GX、Arria V、Stratix IV GX、Stratix V                                        |

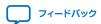

| 追加のシリアル・リファレンス・クロック・ポート。<br>この追加のクロックポートを使用すると、単一のトランシーバー・ブロックを使用して異なるデータレートに対する 2 つの異なるクロックレートを設定することが可能になり、必要なクロックレート (例えば、148.5MHz と 148.35MHz) を切り替えることができます。                                                                                                                                                                                                                                                                                                                | Arria II GX (Arria II GZ を含む) および Stratix<br>IV GX                                 |

| 上部と下部のクワッドからの8つの通常のトランシーバー・チャネル。 4つのMPLLと2つのGPLLをトランシーバー・チャネルのクロックに使用することができます。EP4CGX50およびEP4CGX75デバイスの各レシーバーにはクロック分周器があり、1つのMPLLですべてのレシーバーチャネルを駆動することができます。EP4CGX110およびEP4CGX150デバイスのレシーバーにはクロック分周器がありません。これにより、各MPLLで1つのレシーバーチャネルのみを駆動するように制限し、単一のクワッド内で異なる規格に対応します。 2つの受信リファレンス・クロック(例えば、148.5MHzと148.35MHz)をSDIレシーバーに供給する必要があります。ユーザーロジックにPPM検出機能を実装し、受信リファレンス・クロックとリカバリークロックのppmの差を検出します。検出された差に基づき、2つの受信リファレンス・クロックを切り替える必要があります。これには、rx_serial_refclk_clkswitch信号をトグルします。 | Cyclone IV GX デバイス — EP4CGX30 (F484)、<br>EP4CGX50、EP4CGX75、EP4CGX110、<br>EP4CGX150 |

### 関連情報

V-Series Transceiver PHY IP Core User Guide Notes

# 3.3.1. トランスミッターのクロック

トランスミッターには、パラレル・ビデオ・クロック ( $tx_pclk$ ) とトランスミッター・リファレンス・クロック ( $tx_serial_refclk$ ) の 2 つのクロックが必要です。

パラレル・ビデオ・クロックは、次のパラレルビデオ入力をサンプリングして処理します。

- SD-SDI 27MHz

- HD-SDI 74.25 または 74.175MHz

- 3G-SDI 148.5 または 148.35MHz

トランシーバーは、トランスミッター・リファレンス・クロックを使用して高速シリアル出力を生成します。 トランシーバーは 20 ビットの動作にコンフィグレーションされているため、リファレンス・クロックはシ リアル・データ・レートの 1/20 です。

注意: SD-SDI の場合、オーバーサンプリングの実装により、シリアル・データ・レートは SDI ビットレートの 5 倍になります (例えば、1,350Mbps)。トリプル・スタンダード SDI の場合は、オーバーサンプリング・レートは 11 です。

SD-SDI の動作の場合、トランスミッター・リファレンス・クロックは pclk から取得することができます。その際は、トランシーバー PLL の 1 つを使用します。 PLL は、27MHz の pclk 信号を 5/2 倍にすることができます。

他の規格の場合はすべて、外部マルチプレクサーを使用して代替リファレンス・クロックから選択します。

## 表 11. トランスミッター・クロックの周波数

次の表は、Arria II GX、Arria V、Cyclone IV GX、Cyclone V、Stratix IV、Stratix V デバイスのトランスミッター・クロック tx\_serial\_refclk の周波数を示しています。

| ビデオ規格                 | クロック周波数 (MHz)         |  |

|-----------------------|-----------------------|--|

| SD-SDI                | 67.5                  |  |

| HD-SDI (デュアルリンクを含む)   | 74.175 または 74.25      |  |

| HD-SDI (2 倍のオーバーサンプル) | 148.35 または 148.5      |  |

| デュアル・スタンダード           | 67.5、74.175、または 74.25 |  |

| トリプル・スタンダード           | 148.35 または 148.5      |  |

| 3G-SDI                | 148.35 または 148.5      |  |

# 注意:

SD-SDI 以外は、すべてのビデオ規格において tx\_serial\_refclk 信号を外部で多重化する必要があります。追加の入力リファレンス・クロック・ポートをシリアル・リファレンス・クロックに有効にする場合は、外部のマルチプレクサーは不要です。

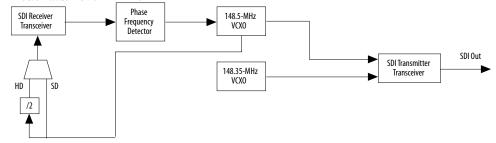

次の図は、Arria II GX、Arria V、Cyclone IV GX、Cyclone V、Stratix IV、Stratix V デバイスのトランスミッター・クロックを表しています。

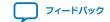

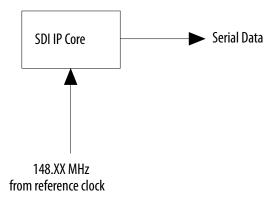

# 図 -10: SD-SDI のトランスミッター・クロック

SD-SDI

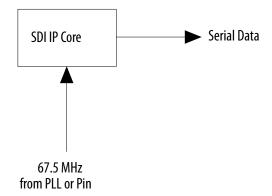

## 図 -11: HD-SDI のトランスミッター・クロック

このクロックでサポートされる周波数は 74.175 または 74.25MHz であり、それぞれ 1.4835 または 1.485Gbps の HD-SDI をサポートします。

HD-SDI

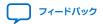

# 図 -12: デュアル・スタンダードのトランスミッター・クロック

マルチプレクサーはデバイス内にある必要があります。 *Dual Standard*

74.XX MHz

SDI IP Core Serial Data

67.5 MHz

### 図 -13: 3G-SDI およびトリプル・スタンダードのトランスミッター・クロック

このクロックでサポートされる周波数は 148.35 または 148.5MHz であり、それぞれ 2.967 または 2.970Gbps の HD-SDI をサポートします。

3G-SDI or Triple Standard

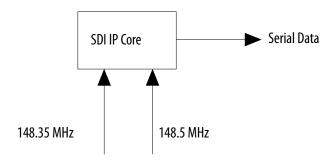

# 図 -14: 3G-SDI およびトリプル・スタンダードのトランスミッター・クロック (追加リファレンス・クロック・ポートあり)

追加のクロックポートが有効になっている場合は、148.5MHzと 148.35MHz の両方のクロックを一緒に供給することができます。 3G-SDI or Triple Standard (with additional reference clock port)

### 関連情報

Altera Transceiver PHY IP Core User Guide

Altera Native PHY IP コアに関する情報が提供されています。

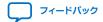

# 3.3.2. レシーバーのクロック

トランシーバーには、レシーバー・リファレンス・クロックの rx\_serial\_refclk が必要です。このクロックにより、トランシーバーのレシーバー PLL をトレーニングします。

- SD-SDI の動作の場合、クロックは名目上シリアル・データ・レートの 1/4 (例えば、67.5Mhz) にする必要があります。クロックはデータに対して周波数でロックされている必要はありません。

- HD-SDI の動作の場合、クロックは名目上シリアル・データ・レートの 1/20 にする必要があります。 クロックはデータに対して周波数でロックされている必要はありません。デザインでは、レシーバー PLL のトレーニングにのみクロックを使用します。

- デュアルまたはトリプル・スタンダードの動作の場合、レシーバー・リファレンス・クロックは 148.5MHz にする必要があります。このモードでは、トランシーバーは SD-SDI 信号を 11 倍でオーバーサンプリングします。

レシーバー・インターフェイスはすべて、共通のレシーバー・リファレンス・クロックを共有します。

### 表 12. レシーバークロックの周波数

次の表は、レシーバークロック rx\_serial\_refclk の周波数を示しています。

| ビデオ規格              | クロック周波数 (MHz)                   |  |

|--------------------|---------------------------------|--|

| SD-SDI             | 67.5                            |  |

| HD-SDI             | 74.175 または 74.25                |  |

| デュアルまたはトリプル・スタンダード | 148.35 または 148.5 <sup>(6)</sup> |  |

| 3G-SDI             | 148.35 または 148.5                |  |

### 図 -15: さまざまな規格におけるレシーバークロック

3G-SDIまたはデュアル/トリプル・スタンダード

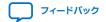

# 3.3.3. トランスミッターのトランシーバー・インターフェイス

インテルでは、トランシーバーを SDI 機能にインターフェイス接続するトランシーバー・インターフェイスを提供しています。

トランスミッターのトランシーバー・インターフェイスは、次の機能を実装します。

- パラレル・ビデオ・クロック・ドメインからトランシーバー・トランスミッター・クロック・ドメインへのリタイミング

- HD-SDI で使用するオプションの 2 倍のオーバーサンプリング

- SD-SDI で使用するトランスミッターのオーバーサンプリング

<sup>(6)</sup> SD-SDI の正しい動作には、148.5MHz のみを使用する必要があります。

### 表 13. トランスミッターのトランシーバー・インターフェイスの機能

| 機能                          | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| トランスミッターのリタイミング             | トランシーバーへのパラレルデータ入力である txdata は、トランシーバー・クロック入力の tx_coreclk に同期し、位相でアライメントされている必要があります。SD-SDI (およびオプションで HD-SDI) には、オーバーサンプリング・ロジックのため、リタイミング機能が必要です。トランスミッターは、小さな 16×20 の FIFO バッファーをリタイミングに使用します。  ・ HD-SDI の場合は、FIFO バッファーでパラレルビデオ入力をトランシーバー・クロックの tx_coreclk に再アライメントします。 tx_pclk ごとに書き込まれ、tx_coreclk ごとに読み出されます。  ・ SD-SDI の場合は、FIFO バッファーはトランスミッターのオーバーサンプリング・ロジックに必要なレート変換も提供します。SD-SDIのデータ幅変換ロジックを使用して、1つおきの tx_pclk で書き込まれます。読み出しは、5番目または 11番目の tx_coreclkで行われます。この操作により、トランスミッターのオーバーサンプリング・ロジックに対して、5番目または 11番目のクロックごとにパラレル・ビデオ・データのワードが提供されるようになります。 |

| HD-SDI の 2 倍のオーバーサンプリング     | 2 倍のオーバーサンプリング・モードでは、2 倍のオーバーサンプリング を実行し、トランシーバーを 2 倍のレートで実行することで、出カジッタ ーのパフォーマンスを向上させます。このモードでは、より高いレートの リファレンス・クロックが必要です。                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SD-SDI のトランスミッターのオーバーサンプリング | SD-SDI には、270Mbps のシリアル・データ・レートが必要です。これは、1,350Mbps の信号を送信することで実現します。その場合に、各ビットは 5 回繰り返されます。このプロセスにより、トランシーバーがサポートされる周波数で動作することを保証します。トリブル・スタンダード・モードでは、ビットは 2,970Mbps で送信され、各ビットは 11 回繰り返されます。                                                                                                                                                                                                                                                                                                                                                                 |

# 3.3.4. レシーバーのトランシーバー・インターフェイス

インテルでは、トランシーバーを SDI 機能にインターフェイス接続するトランシーバー・インターフェイスを提供しています。

レシーバーのトランシーバー・インターフェイスは、次の機能を実装します。

- SD-SDI で使用するレシーバー・オーバーサンプリング

- トランシーバー・コントローラー

# SD-SDI のレシーバーのオーバーサンプリング

Arria II GX、Arria V、Stratix IV、および Stratix Vトランシーバーでは、600Mbps 未満のデータレートに CDR をサポートしていません。レシーバーでは、固定の周波数オーバーサンプリングを使用して、270Mbps の SD-SDI を受信します。トランシーバーではシリアルデータを 1,350 または 2,970Mbps でサンプリングし、SD-SDI のレシーバーのオーバーサンプリング・ロジックで元の270Mbps のデータを抽出します。

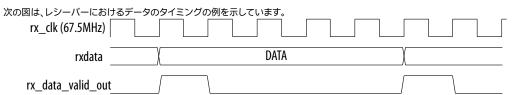

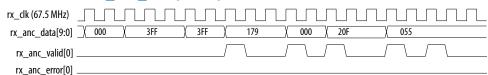

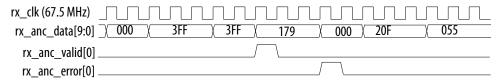

# 図 -16: レシーバーのデータのタイミング

## トランシーバー・コントローラー

SDI に必要なレシーバーの機能を実現するため、トランシーバー・コントローラーでトランシーバーを制御します。

インターフェイスで SD-SDI を受信すると、トランシーバーのレシーバー PLL はレシーバーのリファレンス・クロックにロックされます。

インターフェイスで HD-SDI を受信すると、トランシーバーのレシーバー PLL はまず、レシーバーのリファレンス・クロックにロックすることでトレーニングされます。PLL がロックされると、実際のレシーバーのデータレートを追跡することができます。有効な SDI 信号がない状態で一定期間が経過すると、PLL はリファレンス・クロックで再トレーニングされ、プロセスが繰り返されます。

まず、トランシーバー・コントローラーは、着信データストリームの粗いレート検出を行います。次に、トランシーバーのダイナミック・リコンフィグレーションにより、トランシーバーは検出された規格の正しいレートに再プログラミングされます。再プログラミング後に、トランシーバーは着信ストリームへのロックを試みます。0.1 秒以内に有効なデータが見られない場合、トランシーバーはレシーバーパスをリセットし、レート検出を再度実行します。

レート検出プロセスの開始時に、3 つの enable\_xx 信号のレベルがサンプリングされます。これらの信号のレベルと、トランシーバーが現在プログラムされている状態の情報によって、トランシーバーにプログラミングが必要かを決定します。このプロセスにより、トランシーバーが必要な場合にのみ再プログラミングされることを保証します。

# 3.4. 着信 SDI ストリームへのロック

トランシーバーの制御ステートマシンでは、ストリームにおける TRS の有無を使用し、SDI が正しく受信されているかを特定します。

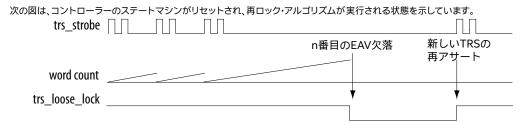

単一の有効な TRS は、レシーバーがいくつかの有効な SDI サンプルを取得していることを制御ステートマシンに示します。制御ステートマシンでは、指定している数の連続するライン内で EAV シーケンスを検出しない場合にのみ、このフラグをデアサートします。その時点で、コントローラーのステートマシンはリセットされ、再ロック・アルゴリズムが実行されます。

## 図 -17: ロック・アルゴリズム

同じアライメントをもつ 2 つの連続する TRS が検出されると、アライナーは新しいアライメントに再アライメントするため、このスキームでは、トランシーバーのリセット・ステート・マシンに影響を与えることなく、SDI ソースの切り替えとアライメントの変更が可能です。

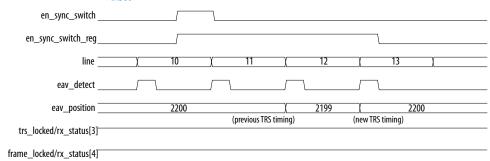

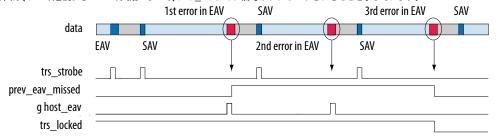

SDI MegaCore ファンクションではまた、着信する EAV および SAV 信号を監視し、それらの間隔が複数のラインにわたって一定であることを確認します。MegaCore ファンクションでの監視は、着信する SDI ワードごとにカウンターをインクリメントし、EAV または SAV が検出されたカウント値を格納する ことによって行います。EAV と SAV の間隔が 6 つのビデオラインで一貫している場合、MegaCore ファンクションは  $rx_status[3]$  出力で  $trs_locked$  を示します。

現在の SDI MegaCore ファンクションの拡張により、指定されている数の欠落 EAV または SAV を、trs\_locked 信号をデアサートせずに許容できるようになっています。

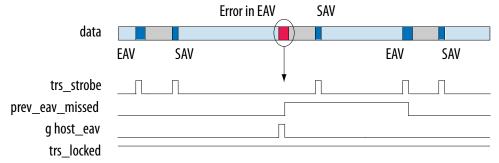

例えば、Tolerance to consecutive missed EAV/SAV パラメーターに 2 を指定している場合、1 つまたは 2 つの連続する EAV の欠落で、「欠落」フラグは設定されますが、 $trs_1ocked$  信号はデアサートされません。正しい位置での適切な EAV により、「欠落」フラグはリセットされます。

次に示されている一連の図は、TRS が欠落している場合、または位置が違う場合の許容動作を表しています。

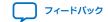

## 図 -18: 単一の EAV の欠落

次の図は、単一の EAV の欠落では、trs\_locked 信号がデアサートされないことを示しています。

# 図 -19: 2 つの連続する EAV の欠落

次の図は、2つの連続する EAV の欠落では、trs\_locked 信号がデアサートされないことを示しています。

# 図 -20: 3 つの連続する EAV の欠落

次の図は、3 つの連続する EAV の欠落によって、trs\_locked 信号がデアサートされることを示しています。

frame\_locked 信号では、TRS の EAV を検出し、フィールド (F) および垂直 (V) 同期の遷移を検査してから、ライン番号をカウントします。F および V の同期における遷移を検査することにより、フレームのタイミングが提供されます。フレームにおいて F および V の同期に立ち上がりエッジまたは立ち下

がりエッジがある場合に、ラインカウント値が格納されます。格納されたカウント値は複数のフレームにわたって比較され、それらが安定していることが確認されます。その後、frame\_locked 信号がアサートされます。

$frame_locked$  信号は、Fまたは V の同期が悪い場合、またはフレームからフレームへの立ち上がりエッジがある場合にデアサートされます。また、 $frame_locked$  信号は、 $trs_locked$  信号がデアサートするとデアサートされます。

$frame_locked$  信号が 0 の場合はフレームは無効であり、レシーバーで信頼できるビデオデータを受信しているとはみなされません。

# 3.5. SDI における受信ビデオ・フォーマットの仕様

次の表は、8ビットの受信ビデオ・フォーマットの仕様を一覧にしています。

| 12-140-16  | 合計アクティブライ | 合計ラインあたりの |       | rx_video_forma | rx_video_forma<br>t [4] | rx_video_f<br>ormat [3:0] |

|------------|-----------|-----------|-------|----------------|-------------------------|---------------------------|

| ビデオ規格      | ピテオ規格     | ワード       | レート   | t [7:5]        | プログレッシブ/イ<br>ンターレース     | フレームレート                   |

| SD         | 720       | _         | _     | 0              | 0                       | 8                         |

| 720p60     |           | 1650      | 60    | 2              | 1                       | 7                         |

| 720p59.94  |           |           | 59.94 |                |                         | 6                         |

| 720p50     |           | 1980      | 50    |                |                         | 5                         |

| 720p30     |           | 3300      | 30    |                |                         | 4                         |

| 720p29.97  |           |           | 29.97 |                |                         | 3                         |

| 720p25     |           | 3960      | 25    |                |                         | 2                         |

| 720p24     |           | 4125      | 24    |                |                         | 1                         |

| 720p23.97  |           |           | 23.97 |                |                         | 0                         |

| 1035i30    | 1035      | 2200      | 30    | 3              | 0                       | 4                         |

| 1035i29.97 |           |           | 29.97 | 3              | 0                       | 3                         |

| 1080i25    | 1080      | 2376      | 25    | 4              | 0                       | 2                         |

| 1080i60    |           | 2200      | 60    | 1              |                         | 7                         |

| 1080i59.94 |           |           | 59.94 |                |                         | 6                         |

| 1080i50    |           | 2640      | 50    |                |                         | 5                         |

| 1080i24    |           | 2750      | 24    |                |                         | 1                         |

| 1080i23.97 |           |           | 23.97 |                |                         | 0                         |

| 1080p60    | 1080      | 2200      | 60    | 1              | 1                       | 7                         |

| 1080p59.94 |           |           | 59.94 |                |                         | 6                         |

| 1080p50    |           | 2640      | 50    |                |                         | 5                         |

| 1080p30    | 1080      | 2200      | 30    | 1              | 1                       | 4                         |

| 1080p29.97 |           |           | 29.97 |                |                         | 3                         |

|            |           |           |       |                |                         | continued                 |

## 3. 機能の説明

## 683587 | 2020.08.20

| ビデオ規格      | 合計アクティブライ | 合計ラインあたりの | レート   | rx_video_forma | rx_video_forma<br>t [4] | rx_video_f<br>ormat [3:0] |

|------------|-----------|-----------|-------|----------------|-------------------------|---------------------------|

| とデオ規格      | ン         | ワード       | D-F   | t [7:5]        | プログレッシブ/イ<br>ンターレース     | フレームレート                   |

| 1080p25    |           | 2640      | 25    |                |                         | 2                         |

| 1080p24    |           | 2750      | 24    |                |                         | 1                         |

| 1080p23.97 |           |           | 23.97 |                |                         | 0                         |

# 4. SDI IP コアの信号

# 4.1. SDI クロック信号

# 表 14. レシーバーのクロック信号

| 信号                      | 方向 | 説明                                                                                                                                                                                                                       |

|-------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gxb4_cal_clk            | 入力 | Arria II GX、Arria V、Cyclone IV GX、および Stratix IV トランシーバー専用のキャリブレーション・クロックです。                                                                                                                                             |

| rx_sd_oversample_clk_in | 入力 | 67.5MHz のオーバーサンプル・クロック入力で、SD-SDI 専用です。                                                                                                                                                                                   |

| rx_serial_refclk        | 入力 | HD-SDI、デュアル・スタンダードおよびトリプル・スタンダードに向けたトランシーバー・トレーニング・クロックです。 注 Stratix V または Arria V デバイスを使用して SDI デュプレックスを生成する場合意: は、tx_serial_refclk 信号と rx_serial_refclk 信号を結び付ける必要があります。                                               |

| rx_serial_refclk1       | 入力 | 二次トランシーバー・トレーニング・クロックです。HD-SDI の場合は 74.175MHz のクロック周波数、3G-SDI、デュアル・スタンダードおよびトリプル・スタンダードの場合は 148.35MHz のクロック周波数です。 Cyclone IV GX デバイスを使用している場合にのみ利用することができます。                                                             |

| rx_coreclk              | 入力 | レシーバー・コントローラーのクロック入力で、Cyclone IV GX デバイス専用です。このクロックの周波数は、rx_serial_refclkと同じにする必要があります。<br>ハードウェアの制約により、トランシーバー PLL とコアロジックでトランシーバーの PLL6とPLL7を使用する場合は、同じクロック入力ピンを共有することはできません。                                          |

| refclk_rate             | 入力 | この信号は、rx_video_format に関連付けられます。受信したビデオ規格を検出します。 148.35MHz のレシーバー・シリアル・リファレンス・クロックの場合は、入力を 0 に設定します。 148.5MHz の RX シリアル・リファレンス・クロックの場合は、入力を 1 に設定します。 注意: Cyclone IV GX デバイスの場合は、rx_coreclk の周波数に応じて refclk_rate を設定します。 |

| gxb_tx_clkout           | 出力 | トランシーバーのトランスミッター・クロック出力です。このクロックは、電圧制御発振器<br>(VCO) の出力であり、トランスミッターのパラレルクロックとして使用されます。ALTGX または ALT2GXB メガファンクションの tx_clkout 信号に内部で接続されます。                                                                                |

| rx_clk                  | 出力 | トランシーバーの CDR クロック。                                                                                                                                                                                                       |

| rx_sd_oversample_clk_ou | 出力 | 67.5MHz のオーバーサンプル・クロック出力で、MegaCore ファンクションをカスケード接続します。SD-SDI 専用です。                                                                                                                                                       |

| rx_video_format         | 出力 | この信号は、refclk_rate に関連付けられます。受信したビデオのフォーマットを示します。rx_video_format の値は、フレームロック信号がアサートされた後に有効になります。                                                                                                                          |

Intel Corporation. 無断での引用、転載を禁じます。Intel、インテル、Intel ロゴ、その他のインテルの名称やロゴは、Intel Corporation またはその子会社の商標です。インテルは FPGA 製品および半導体製品の性能がインテルの標準保証に準拠することを保証しますが、インテル製品およびサービスは、予告なく変更される場合があります。インテルが書面にて明示的に同意する場合を除き、インテルはここに記載されたアプリケーション、または、いかなる情報、製品、またはサービスの使用によって生じるいっさいの責任を負いません。インテル製品の顧客は、製品またはサービスを購入する前、および、公開済みの情報を信頼する前には、デバイスの仕様を最新のバージョンにしておくことをお勧めします。

# 表 15. トランスミッターのクロック信号

| 信号                | 方向 | 説明                                                                                                                                               |

|-------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_pclk           | 入力 | トランスミッターのパラレルクロック入力です。 • SD-SDI = 27MHz • HD-SDI = 74MHz • 3G-SDI = 148.5MHz                                                                     |

| tx_serial_refclk  | 入力 | トランシーバーのリファレンス・クロック入力で、低ジッターです。 注 Stratix V または Arria V デバイスを使用して SDI デュプレックスを生成する場合 意: は、tx_serial_refclk 信号と rx_serial_refclk 信号を結び付ける必要があります。 |

| tx_serial_refclk1 | 入力 | トランシーバーのリファレンス・クロック入力に向けたオプションのポートで、低ジッターです。tx_serial_refclkと同様です。<br><i>注意</i> : Arria II および Stratix IV GX デバイスでのみ利用することができます。                 |

## 表 16. トランシーバー PHY の管理信号

これらの信号は、Arria V および Stratix V デバイスでのみ利用することができます。

| 信号                 | 方向 | 説明                                                                                                                                                                                                                                                           |

|--------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| phy_mgmt_clk       | 入力 | トランシーバー PHY 管理インターフェイスの Avalon-MM クロック入力です。同じクロックを PHY 管理インターフェイスとトランシーバー・リコンフィグレーションに使用します。周波数の範囲は 100 から 125MHz で、それによってトランシーバー・リコンフィグレーション・クロックの仕様を満たします。                                                                                                 |

| phy_mgmt_clk_reset | 入力 | トランシーバー PHY 管理インターフェイスのリセット信号です。この信号はアクティブ High で、レベル・センシティブです。シンプレックス・モードでは、この信号を tx_rst または rx_rst 信号と同じリセットポートに接続することができます。 デュプレックス・モードでは、このリセット信号はトランスミッターとレシーバーに対するグローバルリセットとして機能します。トランスミッターとレシーバーに異なるリセットが必要な 場合は、この信号を tx_rst 信号と rx_rst 信号から切り離します。 |

# 表 17. ソフト・トランシーバー信号

| rx_sd_refclk_337       | 入力 | ソフト・トランシーバーの 337.5MHz サンプリング・クロック             |

|------------------------|----|-----------------------------------------------|

| rx_sd_refclk_337_90deg | 入力 | ソフト・トランシーバーの 337.5MHz サンプリング・クロック、90°の位相シフトあり |

| rx_sd_refclk_135       | 入力 | レシーバーに向けたソフト・トランシーバーの 135MHz パラレルクロック         |

| rx_sd_refclk_270       | 入力 | トランスミッターに向けたソフト・トランシーバーの 270MHz パラレルクロック      |

# 4.2. SDI インターフェイス信号

| 信号               | 幅          | 方向 | 説明                                              |

|------------------|------------|----|-------------------------------------------------|

| enable_crc       | [(N-1):0]  | 入力 | HD-SDI および 3G-SDI の CRC 挿入を有効にします。              |

| enable_sd_search | [1:0]      | 入力 | デュアルまたはトリプル・スタンダード・モードにおいて SD-SDI 信号の検索を可能にします。 |

| enable_hd_search | [1:0]      | 入力 | デュアルまたはトリプル・スタンダード・モードにおいて HD-SDI 信号の検索を可能にします。 |

| enable_3g_search | [1:0]      | 入力 | トリプル・スタンダード・モードにおいて 3G-SDI 信号の検索を可能<br>にします。    |

| enable_ln        | [(N- 1):0] | 入力 | HD-SDI および 3G-SDI のライン番号 (LN) 挿入を有効にします。        |

|                  |            |    | continued                                       |

| 信号                         | 幅           | 方向 | 説明                                                                                                                                                                                                                                                             |

|----------------------------|-------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| en_sync_switch             | [1:0]       | 入力 | アライナーブロックおよびフォーマット・ブロックをすぐに再アライ<br>メントすることで、ダウンストリームが完全に中断しなくなります。                                                                                                                                                                                             |

| rst_rx                     | [1:0]       | 入力 | リセット信号で、レシーバーをリセット状態に保ちます。 Cyclone IV GX デバイスの場合、この信号はレシーバーの rx_coreclock クロックドメインに同期している必要があります。電源投入後に SDI IP コアにリセットを発行し、信頼性の高い動作を保証します。 HD-SDI のデュアル・リンク・レシーバーの場合は、リンク A とリンク B の両方で準備が整った際にこの信号をアサートします。                                                   |

| rst_tx                     | [1:0]       | 入力 | リセット信号で、トランスミッターをリセット状態に保ちます。トランスミッターのリセット同期は、SDI IP コア内で処理されます。 注 ビデオモード (tx_std) とクロックは、デバイスの起動ま意: たはコアのリセット前にセットアップされて安定している必要があります。 電源投入後に SDI IP コアにリセットを発行し、信頼性の高い動作を保証します。                                                                              |

| rx_serial_refclk_clkswitch | [1:0]       | 入力 | リファレンス・クロックを切り替えます。 Cyclone IV GX デバイスを使用している場合にのみ利用することができます。 トリガーされるそれぞれのポジティブエッジで、 rx_serial_refclkとrx_serial_refclk1を切り替えます。                                                                                                                               |

| rx_protocol_clk            | [(N-1):0]   | 入力 | プロトコルデータ向けの外部クロック                                                                                                                                                                                                                                              |

| rx_protocol_hd_sdn         | [(N-1):0]   | 入力 | デュアルまたはトリプル・スタンダード・プロトコル・ブロックにおける HD-SDI または SD-SDI の処理を選択します。 この信号は、デュアルまたはトリプル・スタンダード・プロトコル・ブロックにのみ表示され、rx_protocol_in 信号の 3G-SDI(1)、HD-SDI(1)、または SD-SDI(0) のデータを示します。分割プロトコル/トランシーバーのデザインでは、この信号をトランシーバー・ブロックの rx_std_flag_hd_sdn 出力に接続する必要があります。          |

| rx_protocol_in             | [(20N-1):0] | 入力 | プロトコル専用モードの外部データ入力                                                                                                                                                                                                                                             |

| rx_protocol_locked         | [(N-1):0]   | 入力 | トランシーバーのコントロール・ロジックへの入力です。アクティブになると、この信号はプロトコルブロックがロックされていることをトランシーバーのコントロール・ロジックに示すことにより、現在のレートでトランシーバー検索アルゴリズムを停止します。                                                                                                                                        |

| rx_protocol_rst            | [(N-1):0]   | λカ | プロトコルブロックのリセットです。この信号はプロトコルブロックをリセットします。<br>分割トランシーバー/プロトコルのデザインでは、この信号を<br>rx_status[1] ピン (sdi_reset) に接続することができます。                                                                                                                                          |

| rx_protocol_valid          | [(N-1):0]   | 入力 | プロトコル専用モードの外部データ有効入力                                                                                                                                                                                                                                           |

| rx_protocol_rate           | [1:0]       | 入力 | プロトコルブロックへの入力です。この信号は、受信したビデオ規格をプロトコルブロックに示します。<br>ただし、この信号は 3G-SDI の Level A ストリームと 3G-SDI の Level B ストリームを区別しません。プロトコルブロックのアライナーブロックで、3G-SDI の Level A ストリームと 3G-SDI の Level B ストリームを区別します。分割トランシーバー/プロトコルのデザインでは、この信号をトランシーバー・ブロックの rx_std ポートに接続する必要があります。 |

| rx_xcvr_trs_lock           | [(N-1):0]   | 入力 | トランシーバーのコントロール・ロジックへの入力です。この信号は、プロトコル専用レシーバーブロックの rx_status[3] ピン(trs_locked)に接続する必要があります。                                                                                                                                                                     |

|                            |             |    | continued                                                                                                                                                                                                                                                      |

| 信号             | 幅           | 方向 | 説明                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|-------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sdi_rx         | [(N-1):0]   | 入力 | シリアル入力                                                                                                                                                                                                                                                                                                                                                                                     |

| txdata         | [(20N-1):0] | 入力 | ユーザーによって提供されるトランスミッター・パラレル・データの Valid です。SD-SDI では 9:0 を使用し、HD-SDI では 20N - 1:0 を使用します。  SD-SDI = ビット 19:10 未使用、ビット 9:0 Cb、Y、Cr、Y マルチプレクス  HD-SDI = ビット 19:10 Y、ビット 9:0 C  デュアルリンク = ビット 39:30 Y リンク B、ビット 29:20 C リンク B、ビット 19:10 Y リンク A、ビット 9:0 C リンク A  3G-SDI Level A = ビット 19:10 Y、ビット 9:0 C  3G-SDI Level B = ビット 19:10 Cb、Y、Cr、Y マルチプレクス (リンク A)、ビット 9:0 Cb、Y、Cr、Y マルチプレクス (リンク B) |

| tx_ln          | [21:0]      | 入力 | トランスミッターのライン番号です。  • HD-SDI = ビット 21:11 11'd0、ビット 10:0 LN  • デュアルリンク = ビット 21:11 LN リンク B、ビット 10:0 LN リンク A  • 3G-SDI Level A = ビット 21:11 11'd0、ビット 10:0 LN  • 3G-SDI Level B = ビット 21:11 LN リンク A、ビット 10:0 LN リンク B                                                                                                                                                                       |

| tx_trs         | [(N-1):0]   | 入力 | トランスミッターの TRS 入力です。HD-SDI の LN および CRC の<br>挿入で使用します。<br>EAV TRS と SAV TRS の最初のワードでアサートします。                                                                                                                                                                                                                                                                                                |

| tx_std         | [1:0]       |    | トランスミッターのスタンダードです。     SD-SDI = 00     HD-SDI = 01     3G-SDI Level A = 11     3G-SDI Level B = 10  注意: この信号は、デバイスの起動またはコアのリセット前にセットアップされて安定している必要があります。                                                                                                                                                                                                                                   |

| trs_loose_lock | [(N-1):0]   | 出力 | プロトコル専用のレシーバーモードの TRS ロック信号です。この信号は、トランシーバー専用レシーバーブロックのrx_protocol_locked ピンに接続することができます。                                                                                                                                                                                                                                                                                                  |

| crc_error_y    | [1:0]       | 出力 | <ul> <li>ルーマチャネルの CRC エラーです。</li> <li>HD-SDI: ビット 1 未使用、ビット 0 crc_error_y</li> <li>デュアルリンク: ビット 1 リンク B crc_error_y、ビット 0 リンク A crc_error_y</li> <li>3G-SDI Level A: ビット 1 未使用、ビット 0 crc_error_y</li> <li>3G-SDI Level B: ビット 1 リンク A crc_error_y、ビット 0 リンク B crc_error_y</li> </ul>                                                                                                       |

| crc_error_c    | [1:0]       | 出力 | クロマチャネルの CRC エラーです。  • HD-SDI: ビット 1 未使用、ビット 0 crc_error_c  • デュアルリンク: ビット 1 リンク B crc_error_c、ビット 0 リンク A crc_error_c  • 3G-SDI Level A: ビット 1 未使用、ビット 0 crc_error_c  • 3G-SDI Level B: ビット 1 リンク A crc_error_c、ビット 0 リンク B crc_error_c                                                                                                                                                   |

| rx_AP          | [1:0]       | 出力 | これは、アクティブ画像間隔のタイミング信号です。アクティブ画像間隔がアクティブな際に、レシーバーはこの信号をアサートします。                                                                                                                                                                                                                                                                                                                             |

|                |             |    | continued                                                                                                                                                                                                                                                                                                                                                                                  |

| 信号                 | 幅           | 方向 | 説明                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|-------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |             |    | <ul> <li>SD-SDI/HD-SDI: ビット 1 未使用、ビット 0 rx_ap</li> <li>デュアルリンク: ビット 1 リンク B 未使用、ビット 0 リンク A rx_ap</li> <li>3G-SDI Level A: ビット 1 未使用、ビット 0 rx_ap</li> <li>3G-SDI Level B: ビット 1 リンク A rx_ap、ビット 0 リンク B rx_ap</li> </ul>                                                                                                                                |

| rxdata             | [(20N-1):0] | 出力 | レシーバーのパラレルデータです。SD-SDIでは 9:0 を使用し、<br>HD-SDIでは 20N-1:0 を使用します。  SD-SDIのビット 19:10 未使用、ビット 9:0 Cb、Y、Cr、Yマルチプレクス  HD-SDIのビット 19:10 Y、ビット 9:0 C  デュアルリンク: ビット 39:30 Y リンク B、ビット 29:20 C リンク B、ビット 19:10 Y リンク A、ビット 9:0 C リンク A  3G-SDI Level A: ビット 19:10 Y、ビット 9:0 C  3G-SDI Level B: ビット 19:10 Cb、Y、Cr、Yマルチプレクス (リンク A)、ビット 9:0 Cb、Y、Cr、Yマルチプレクス (リンク B) |

| rx_data_valid_out  | [1:0]       | 出力 | オーバーサンブリング・ロジックからのデータの Valid です。アサートされると、rxdata の現在のデータが有効であることを示します。このパスのビット 0 は、rxdata の有効なデータを示します。3G-SDI またはトリプル・スタンダードで SMPTE 425M-B 信号を受信している場合は、ビット 1 は rxdata のデータが仮想リンク A からであることを示します。ビット 0 はデータが仮想リンク B からであることを示します。                                                                                                                        |

| rx_F               | [1:0]       | 出力 | これは、フィールド・ビット・タイミング信号です。この信号は、現在アクティブなビデオフィールドを示します。インターレース・フレームの場合、0 は最初のフィールド (F0) を意味し、1 は 2 番目のフィールド (F1) を意味します。プログレッシブ・フレームの場合は、値は常に 0 です。  SD-SDI/HD-SDI: ビット 1 未使用、ビット 0 rx_f デュアルリンク: ビット 1 未使用、ビット 0 rx_f 3G-SDI Level A: ビット 1:0 未使用  3G-SDI Level B: ビット 1:0 未使用                                                                            |

| rx_H               | [1:0]       | 出力 | <ul> <li>これは、水平ブランキング間隔のタイミング信号です。水平ブランキング間隔がアクティブな場合に、レシーバーはこの信号をアサートします。</li> <li>SD-SDI/HD-SDI: ビット 1 未使用、ビット 0 rx_h</li> <li>デュアルリンク: ビット 1 未使用、ビット 0 rx_h</li> <li>3G-SDI Level A: ビット 1 未使用、ビット 0 rx_h</li> <li>3G-SDI Level B: ビット 1 リンク A rx_h、ビット 0 リンク B rx_h</li> </ul>                                                                      |

| rx_ln              | [21:0]      | 出力 | レシーバーのライン番号です。  HD-SDI = ビット 21:11 未使用、ビット 10:0 LN  デュアルリンク = ビット 21:11 未使用、ビット 10:0 LN  3G-SDI Level A = ビット 21:11 未使用、ビット 10:0 LN  1G-SDI Level B = ビット 21:11 LN リンク A、ビット 10:0 LN リンク B                                                                                                                                                              |

| rx_std_flag_hd_sdn | 1           | 出力 | デュアルまたはトリプル・スタンダード専用で、受信したスタンダードを示します。<br>HD-SDI = 1、SD-SDI = 0                                                                                                                                                                                                                                                                                         |

| rx_V               | [1:0]       | 出力 | これは、垂直ブランキング間隔のタイミング信号です。垂直ブランキング間隔がアクティブな場合に、レシーバーはこの信号をアサートします。                                                                                                                                                                                                                                                                                       |

|                    |             |    | continued                                                                                                                                                                                                                                                                                                                                               |

| 信号              | 幅           | 方向 | 説明                                                                                                                                                                                                      |

|-----------------|-------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |             |    | <ul> <li>SD-SDI/HD-SDI: ビット 1 未使用、ビット 0 rx_v</li> <li>デュアルリンク: ビット 1 未使用、ビット 0 rx_v</li> <li>3G-SDI Level A: ビット 1 未使用、ビット 0 rx_v</li> <li>3G-SDI Level B: ビット 1 リンク A rx_v、ビット 0 リンク B rx_v</li> </ul> |

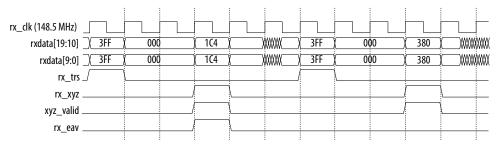

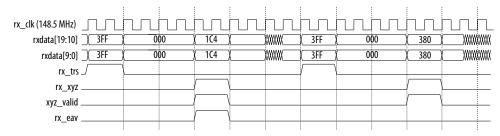

| rx_xyz          | 1           | 出力 | レシーバーの出力で、現在のワードが XYZ ワードであることを示し<br>ます。                                                                                                                                                                |

| xyz_valid       | 1           | 出力 | レシーバーの出力で、現在の TRS フォーマットが有効である (XYZ<br>ワードが正しい) ことを示します。                                                                                                                                                |

| rx_eav          | 1           | 出力 | レシーバーの出力で、現在の TRS が EAV であることを示します。                                                                                                                                                                     |

| rx_trs          | 1           | 出力 | レシーバーの出力で、現在のワードが TRS であることを示します。<br>この信号は、3FF 000 000 TRS の最初のワードでアサートされま<br>す。                                                                                                                        |

| sdi_tx          | [(N-1):0]   | 出力 | シリアル出力                                                                                                                                                                                                  |

| tx_protocol_out | [(20N-1):0] | 出力 | データ出力 (プロトコル専用モード)                                                                                                                                                                                      |

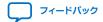

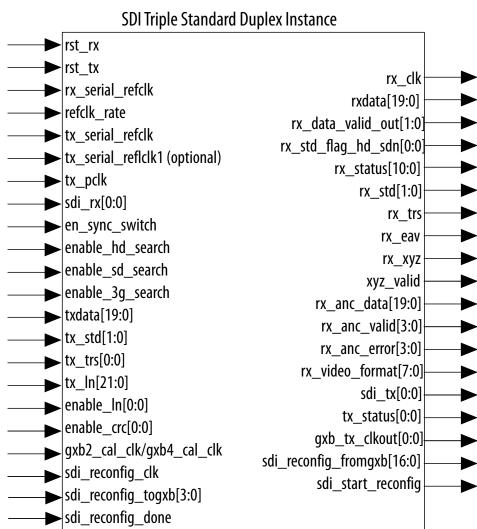

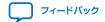

次の図は、SDI トリプル・スタンダード・インスタンスの入力および出力インターフェイス信号を示しています。

# 図 -21: SDI トリプル・スタンダードのレシーバーにおけるインターフェイス信号